1、编写目的

整理IIC开发流程。本次设计实现使用 PS 端的 I2C 控制来完成对 EEPROM 芯片的读写。由于芯片位于拓展板上,属于 PL 侧资源,因此,我们需要通过 EMIO 将 PS 端的I2C 控制器接口信号路由到 PL。为了确保设计成功完成了对 EEPROM 的读写,我们将向 EEPROM 指定寄存器地址中写入一串自加的数据,并读回比较。通过对比写入和读出数据是否一致来判断读写是否成功,并通过串口, 打印出判断结果。

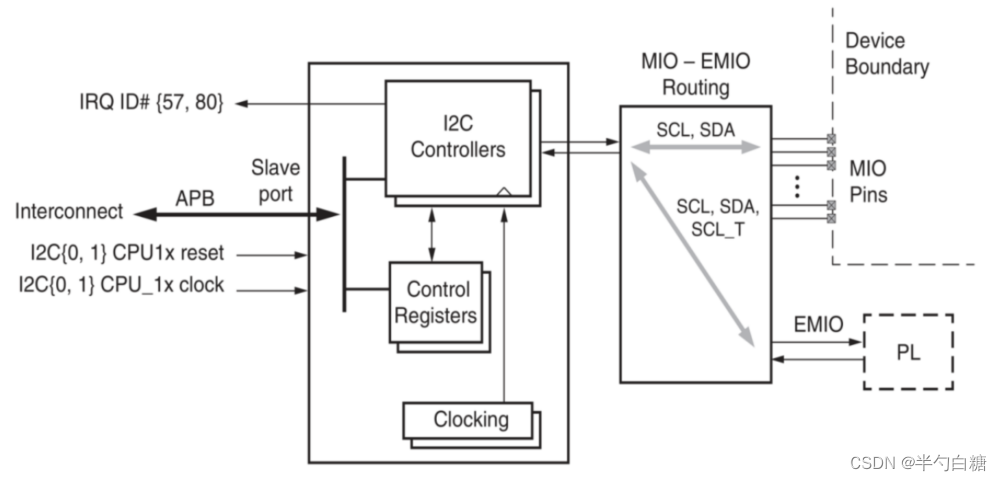

2、IIC控制器框图

用户通过 APB 总线对 I2C 控制器进行交互;22

3、IIC接口

I2C 分为软件 I2C 和硬件 I2C:

软件 I2C:软件 I2C 通信指的是通过两个 I/O 端口模拟出来的 I2C,用软件控制管脚状态以模拟 I2C 通信波形,软件模拟寄存器的工作方式。

硬件 I2C:一块硬件电路,硬件 I2C 对应芯片上的 I2C 外设,有相应 I2C 驱动电路,其所使用的 I2C 管脚也是专用的,硬件(固件) I2C 是直接调用内部寄存器进行配置。硬件 I2C 的效率要远高于软件的,而软件 I2C 由于不受管脚限制,接口则比较灵活。

4、IIC通信原理

4.1、主机和从机概念

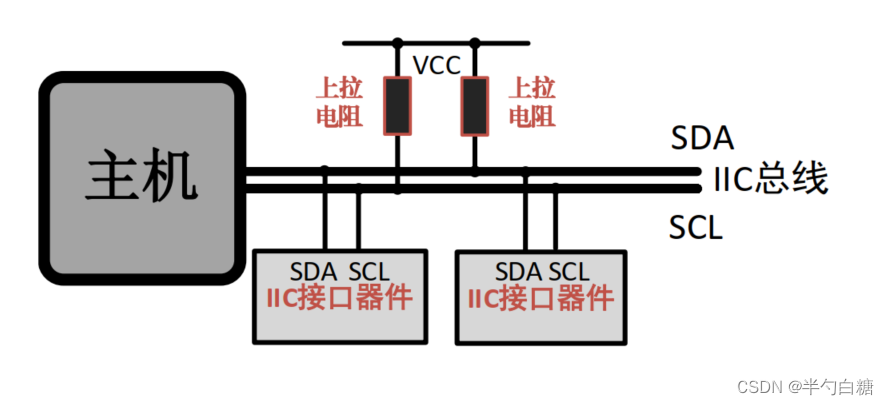

主机负责整个系统的任务协调与分配,从机一般是通过接收主机的指令从而完成某些特定的任务,主机和从机之间通过总线连接,进行数据通讯。主机往总线上发送地址,所有的从机都能接收到主机发出的地址,然后每个从机将主机发送的地址与自己的地址比较,如果匹配上,这个从机就会向总线发出一个响应信号。主机收到响应信号后,开始向总线上发送数据。

I2C 通信原理是通过对 SCL 和 SDA 线高低电平时序的控制,来产生 I2C 总线协议所需要的信号进行数据的传递。在总线空闲状态时, SCL 和 SDA 被上拉电阻拉高,使 SDA 和 SCL 线都保持高电平。 I2C 通信方式为半双工,只有一根SDA 线,同一时间只可以单向通信。

5、IIC读写时序

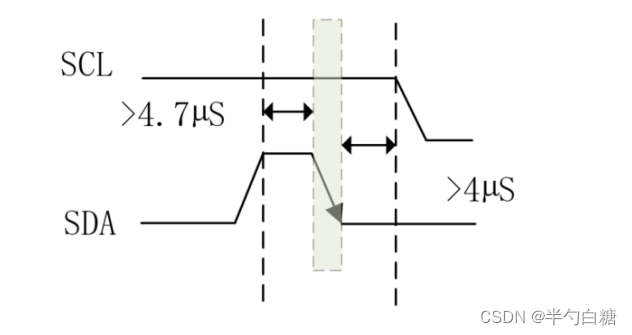

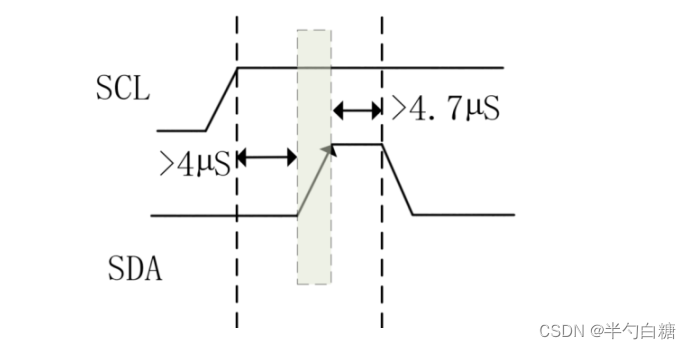

5.1起始信号

当时钟线 SCL 为高电平期间,数据线 SDA 电平由高到低的跳变为起始信号

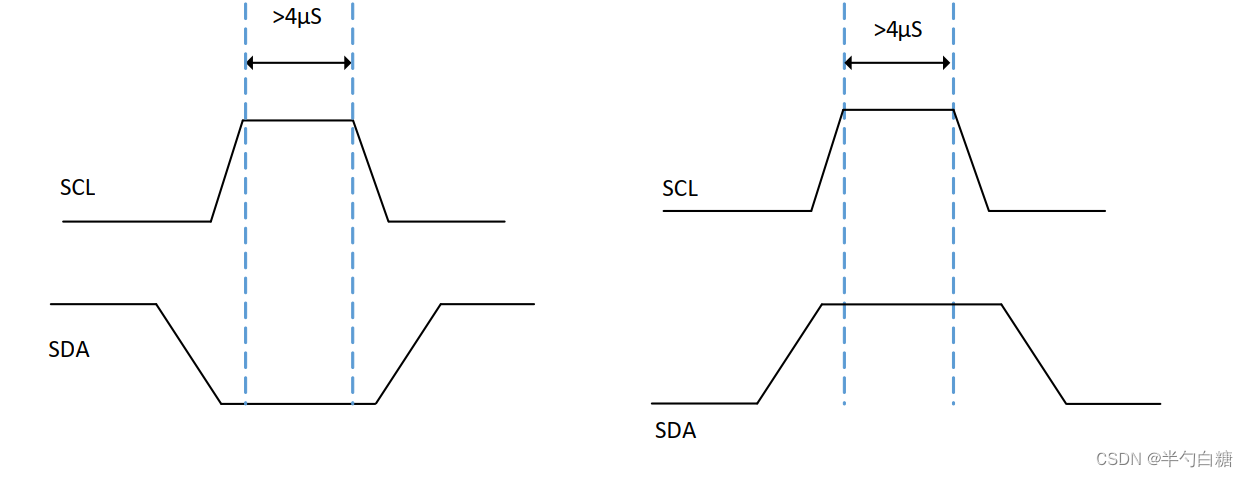

5.2结束信号

当所有数据都发送完成时, 主机将产生一个停止条件。停止条件定义为:在 SDA 置于低电平时,将 SCL 拉高并保持高电平,然后将 SDA 拉高。

5.3应答信号

I2C 总线上的所有数据都是以 8 位字节传送的,发送器每发送一个字节,就在第 9 个时钟脉冲期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK 简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收该字节没有成功

5.4数据发送

5.4数据发送

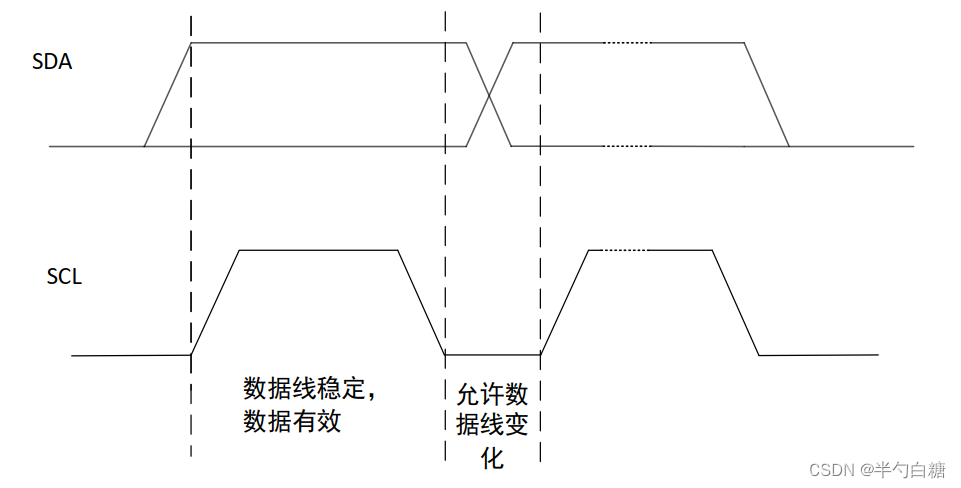

在 I2C 总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在 SCL串行时钟的配合下,在SDA 上逐位地串行传送每一位数据。进行数据传送时,在 SCL 呈现高电平期间,SDA上的电平必须保持稳定,低电平为数据 0,高电平为数据 1。只有在 SCL为低电平期间,才允许SDA上的电平改变状态

5.5IIC写时序

5.5IIC写时序

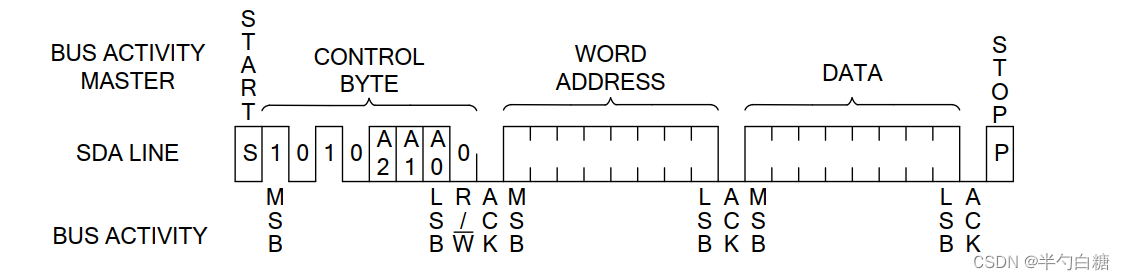

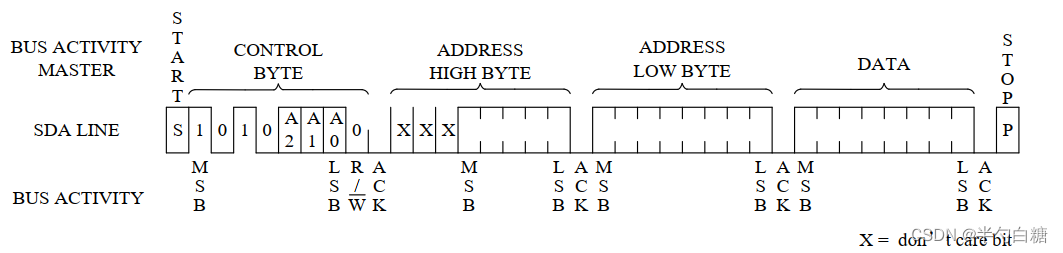

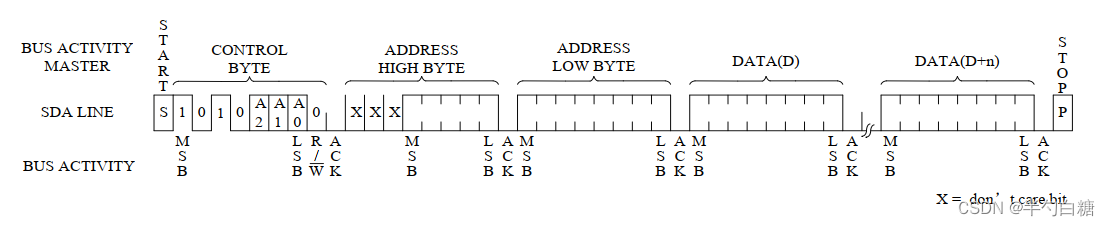

上图为1 字节地址段器件和 2 字节地址段器件单字节写时序图

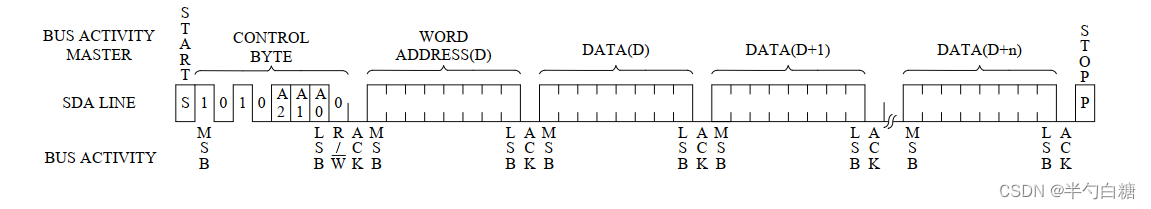

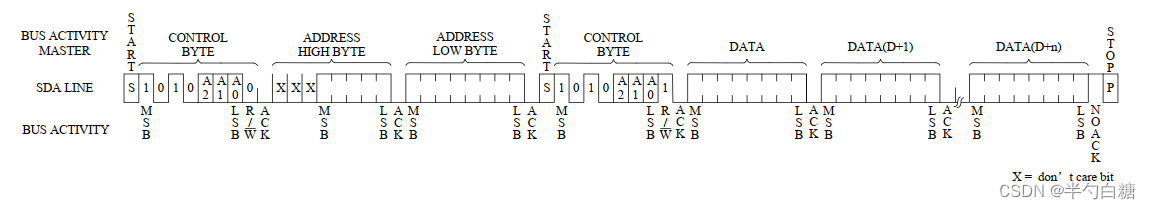

上图为为 1 字节地址段器件和 2 字节地址段器件连续多字节写时序图

5.6IIC读时序

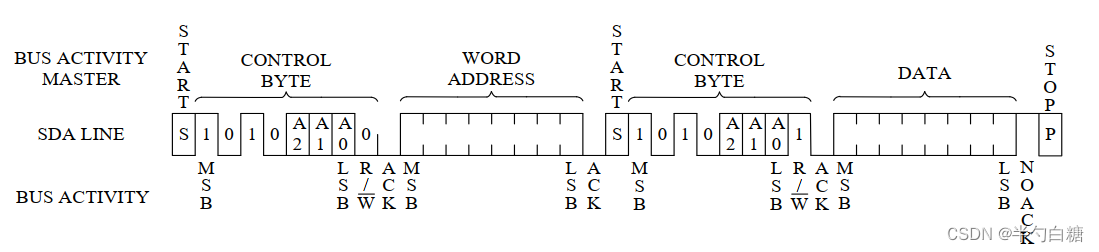

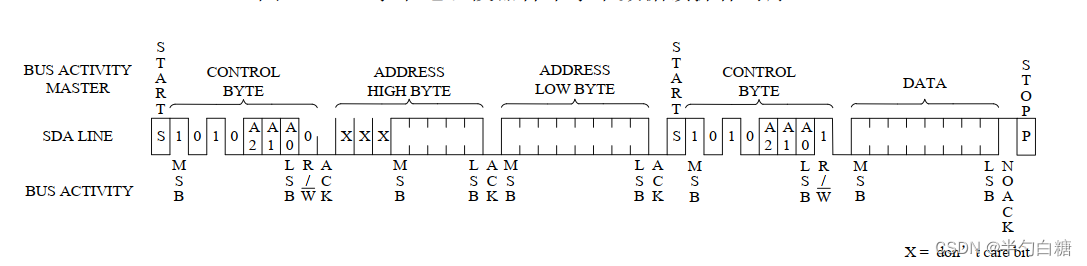

上图分别为 1 字节地址段器件单字节数据读操作和 2 字节地址段器件单字节数据读操作时序图

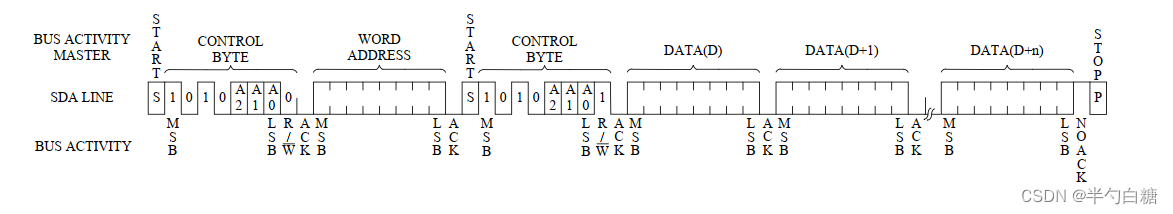

上图分别为 1 字节地址段器件和 2 字节地址段器件连续多字节读时序图

6.PS侧软件程序设计

1、在PL搭建硬件系统,生成.hdf文件

2、在SDK中进行软件程序开发

下面重点简述在SDK软件程序开发:

1、查找IIC设备

2、初始化IIC设备

3、设置IIC串行时钟频率

4、将数据写入EEPROM中

5、读取EEPROM数据

6、对比写入读取数据是否相同

7、串口打印结果

1548

1548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?