1.SignalTap简介

SignalTap II全称SignalTap II Logic Analyzer,是一款功能强大且极具实用性的FPGA片上debug工具软件,它集成在altera公司提供的FPGA开发工具Quartus II中,是第二代系统级调试工具,可以捕获和显示实时信号,观察在系统设计中的硬件和软件之间的互相作用。

Quartus II软件可以选择要捕获的信号、开始捕获的时间,以及要捕获多少数据样本。还可以选择时间数据从器件的存储器块通过JTAG端口传送至SignalTap II Logic Analyzer,还可以连接I/O引脚以供外部逻辑分析仪或示波器使用。将实时数据提供给工程师帮助debug。

2.实例讲解SignalTap的使用

本文通过DE2板卡上的拨动开关SW[7:0]控制LEDR[7:0]的亮灭,并利用SignalTap检测SW[7:0]电平的实时变化。

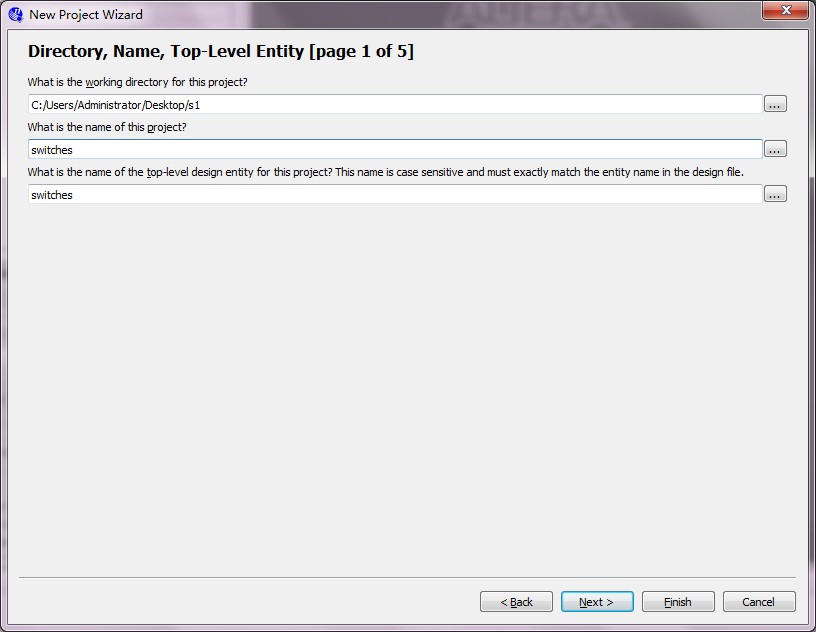

(1)建立工程switches。

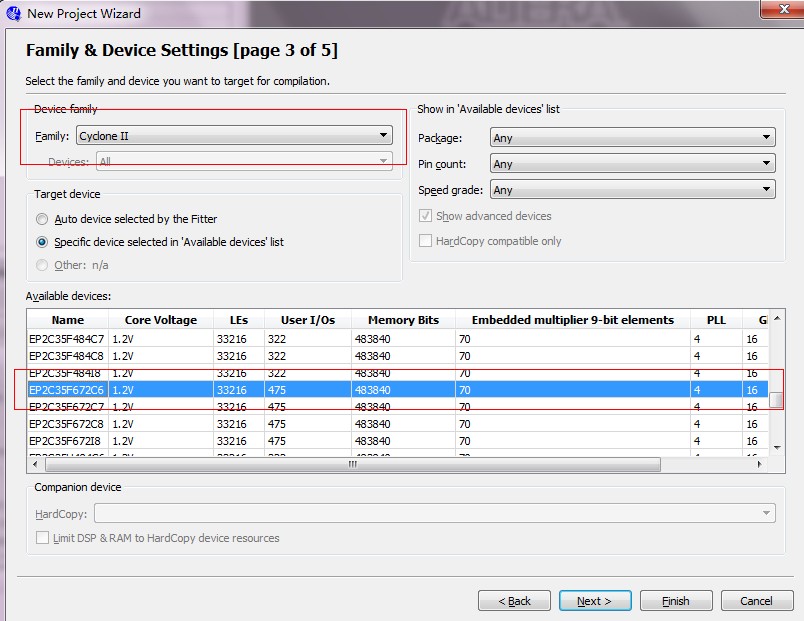

(2)Device选择DE2对应的Cyclone II 系列的EP2C35F672C6。

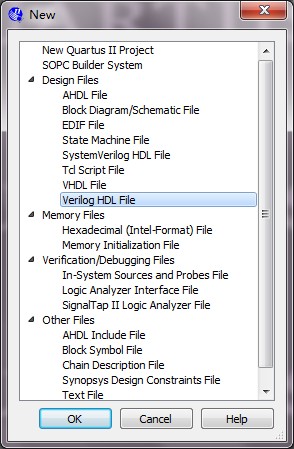

(3)建立VerilogHDL File 并命名为switches.v文件。

switches.v文件内源码如下图所示。

(4)点击assignments->import assignments,导入DE2管脚配置信息DE2_pin_assignments.csv文件。

(5)新建SignalTap II Logic Analyzer File文件,如图所示。

另存为switches.stp,出现下图提示选择OK和Yes。

(6) Compile Design

(7)双击如图所示空白处,添加检测节点。

(8)点击List,从中选择SW[7:0]。

Signal Configuration中的Clock选择CLOCK_50。

(9)给DE2开发板上电,Hardware选择USB-Blaster。

(10)选择相应的SOF文件。

(11)重新Complie Design。

(12)下载SOF文件。

(13)选择自动分析。

(14)拨动开关,对应的LED亮灭,检测到的电平变化如图所示。

3.实现原理

SignalTap II获取实时数据的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以预先设定的时钟采样实时数据,并存储于FPGA片上ram资源中,然后通过JTAG传送回Quartus II分析。可见SignalTap II,其实也是在工程额外加入了模块来采集信号,所以使用SignalTap II需要一定的代价,首先是逻辑单元(ELA),其次是ram,如果工程中剩余的ram资源比较充足,则SignalTap II 一次可以采集较多的数据,相应的如果FPGA资源已被工程耗尽则无法使用SignalTap II调试。

本文详细介绍了SignalTap II——一款强大的FPGA片上调试工具。文章通过实例演示了如何使用SignalTap II 捕获和显示实时信号,帮助读者了解其在Quartus II中的集成方式及具体操作步骤。

本文详细介绍了SignalTap II——一款强大的FPGA片上调试工具。文章通过实例演示了如何使用SignalTap II 捕获和显示实时信号,帮助读者了解其在Quartus II中的集成方式及具体操作步骤。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?