一、操作步骤

每一操作步骤的具体过程此处不再赘述了,已经有了很多很好的教程。

此处主要是对大概过程的记录(方便后续忘记咋用时回看)以及个别个人认为需要注意的点的记录。

1、创建stp文件。

2、添加时钟。

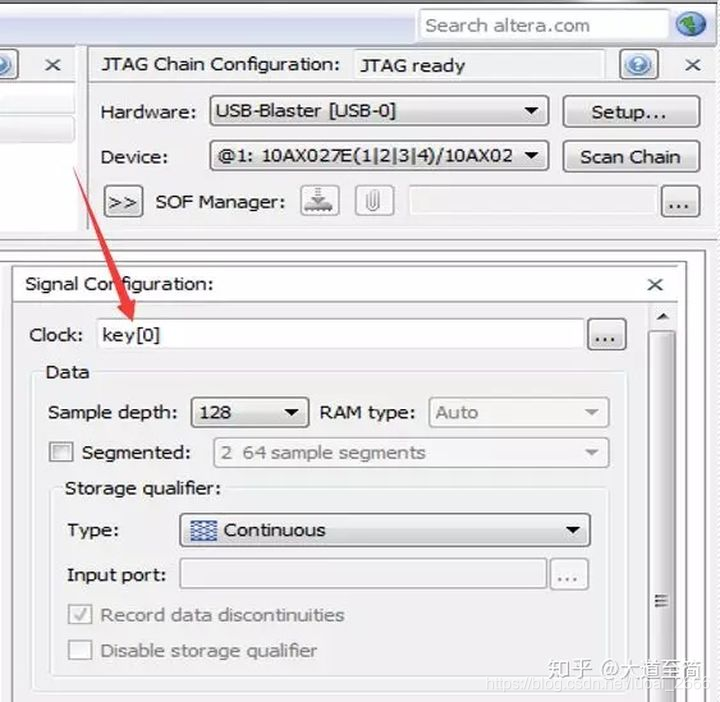

SIGNALTAP的采样时钟,不一定是时钟信号,可以是其他任意的信号。总之,SIGNALTAP会在采样时钟的上升沿去捕捉信号的值,如果没有上升沿,则会一直等待。例如下图所示,就是以按键信号key【0】为采样时钟。在key【0】由0变1时,就会采样一个值。

若该工程使用到几个模块,并且每个模块的时钟不一定相同,则我们选择采样时钟时,要根据我们要测试的信号所在的模块的时钟是什么。

3、添加待观察信号和触发条件

Filter中的【pre_synthesis】表示综合前设计中的信号,与Verilog设计中存在的信号最为贴近;

【post-fitting】表示添加了综合优化、布局布线之后的一些信号,与设计电路的物理结构最为接近。

触发条件含义:在采样时钟的上升沿,当所有触发使能信号都满足触发条件时,将会出现触发。

4、设置仿真模式。

① 采样深度:表示采多少个样点的信号。

② 采样模式:分段采样【Segmented】与循环采样。

循环采样:在信号触发后连续采样至采样深度;

分段采样:将采样深度分为N段,信号每触发一次就采样一段长度的数据,需要连续触发N次来填满整个存储。

本文档详细介绍了SignalTap逻辑分析仪的使用步骤,包括创建stp文件、添加时钟、选择采样模式以及设置触发条件。重点强调了采样时钟的选择、触发条件的设置和信号观察的注意事项。在遇到instance not found问题时,提供了解决方案,如检查.pof与.stp匹配,以及在修改STP文件时何时需要重新编译。此外,还提到了Signaltap的文件导出格式和时间单位设置,以及如何观察wire和reg信号的方法。

本文档详细介绍了SignalTap逻辑分析仪的使用步骤,包括创建stp文件、添加时钟、选择采样模式以及设置触发条件。重点强调了采样时钟的选择、触发条件的设置和信号观察的注意事项。在遇到instance not found问题时,提供了解决方案,如检查.pof与.stp匹配,以及在修改STP文件时何时需要重新编译。此外,还提到了Signaltap的文件导出格式和时间单位设置,以及如何观察wire和reg信号的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1029

1029

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?