目录

Wild equality and wild inequality 不定值的比较

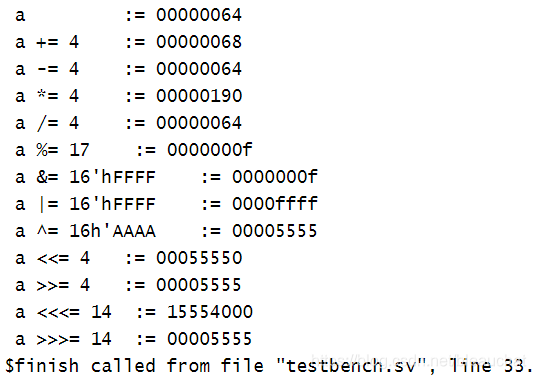

Assignment operators 赋值操作

- +=

- -=

- *=

- /=

- %=

- &=

- |=

- ^=

- <<= 左移后赋值

- >>= 右移后赋值

- <<<= 算术左移后赋值

- >>>= 算术右移后赋值

注意:逻辑移位(<<和>>)时移入的是0,算术右移(>>>)移入的是标志位(最高位),算术左移移入的是0;

module assignment_operator ();

reg [31:0] a = 100;

initial begin

$display (" a := %h", a );

a += 4;

$display (" a += 4 := %h", a );

a -= 4;

$display (" a -= 4 := %h", a );

a *= 4;

$display (" a *= 4 := %h", a );

a /= 4;

$display (" a /= 4 := %h", a );

a %= 17;

$display (" a %s= 17 := %h", "%", a );

a &= 16'hFFFF;

$display (" a &= 16'hFFFF := %h", a );

a |= 16'hFFFF;

$display (" a |= 16'hFFFF := %h", a );

a ^= 16'hAAAA;

$display (" a ^= 16h'AAAA := %h", a );

a <<= 4;

$display (" a <<= 4 := %h", a );

a >>= 4;

$display (" a >>= 4 := %h", a );

a <<<= 14;

$display (" a <<<= 14 := %h", a );

a >>>= 14;

$display (" a >>>= 14 := %h", a );

#1 $finish;

end

endmodule

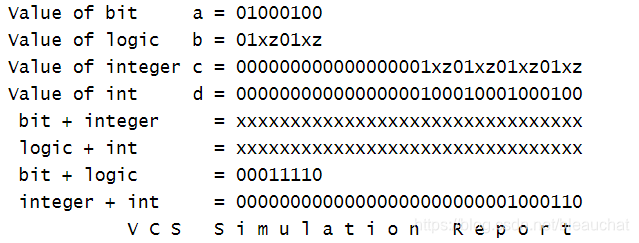

再来看常用的两种类型logic和bit的操作:

module bit_logic_operator ();

bit [7:0] a = 8'b01xz_01xz;

logic [7:0] b = 8'b01xz_01xz;

integer c = 32'b01xz_01xz_01xz_01xz;

int d = 32'b01xz_01xz_01xz_01xz;

initial begin

$display ("Value of bit a = %b", a);

$display ("Value of logic b = %b", b);

$display ("Value of integer c = %b", c);

$display ("Value of int d = %b", d);

$display (" bit + integer = %b", a + c);//任何带不定值的操作,结果都是不定值

$display (" logic + int = %b", b + d);

a = 10;

b = 20;

c = 30;

d = 40;

$display (" bit + logic = %b", a + b);

$display (" integer + int = %b", c + d);

end

endmodule

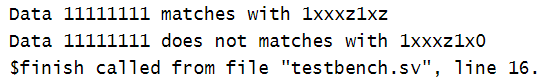

Wild equality and wild inequality 不定值的比较

不定值的比较主要涉及到两个操作符:=?=和 !?=,例子如下:

module wild_equality_operator ();

bit [7:0] data = 8'hFF;

initial begin

// Compare with wild equality

if (data =?= 8'b1xxx_z1xz) begin

$display ("Data %b matches with %b", data, 8'b1xxx_z1xz);

end

// Compare with wild non-equality

if (data !?= 8'b1xxx_z1x0) begin

$display ("Data %b does not matches with %b", data, 8'b1xxx_z1x0);

end

#1 $finish;

end

endmodule

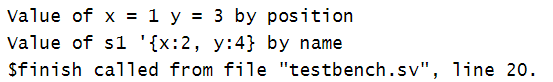

struct expressions 结构体表达式

module struct_expr_operator();

typedef struct {

int x;

int y;

} myStruct;//定义结构体

myStruct s1;//结构体实例

int k = 1;

initial begin

#1 s1 = '{1, 2+k}; //初始化结构体,格式与数组是相同的

// by position

#1 $display("Value of x = %g y = %g by position", s1.x, s1.y); //调用结构体元素,这与调用类中的方法是一致的

#1 s1 = '{x:2, y:3+k};

// by name

#1 $display("Value of s1 ", s1, " by name");

#1 $finish;

end

endmodule

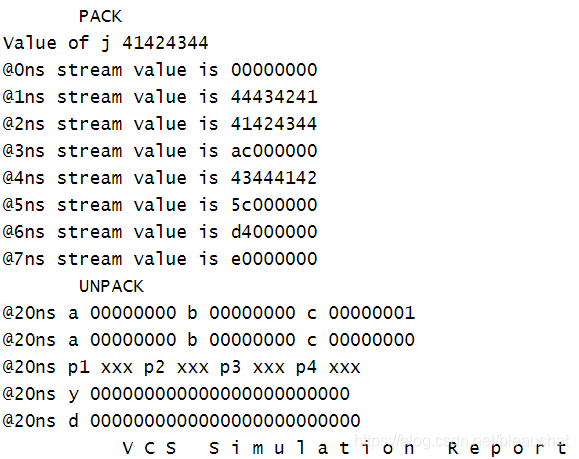

Streaming operators 流操作符

流操作符用于把其后的数据打包成一个比特流。操作符>>把数据从左至右变成流,而<<把数据从右至左变成流 .

module streaming();

//-------------------------------

// PACK Example

//-------------------------------

int j = { "A", "B", "C", "D" };

bit [31:0] stream;

initial begin

$display(" PACK");

$display("Value of j %0x",j);

$monitor("@%0dns stream value is %x",$time, stream);

#1 stream = { << byte {j}};

#1 stream = { >> {j}} ;

#1 stream = { << { 8'b0011_0101 }};

#1 stream = { << 16 {j}};

#1 stream = { << 4 { 6'b11_0101 }};

#1 stream = { >> 4 { 6'b11_0101 }} ;

#1 stream = { << 2 { { << { 4'b1101 }} }};

end

//-------------------------------

// UNPACK Example

//-------------------------------

int a, b, c;

logic [10:0] up [3:0];

logic [11:1] p1, p2, p3, p4;

bit [96:1] y;

int j ;

bit [99:0] d;

initial begin

#20;

$display(" UNPACK");

// Below line should give compile error

//{>>{ a, b, c }} = 23'b1;

{>>{ a, b, c }} = 96'b1;

$display("@%0dns a %x b %x c %x",$time,a,b,c);

{>>{ a, b, c }} = 100'b1;

$display("@%0dns a %x b %x c %x",$time,a,b,c);

{ >> {p1, p2, p3, p4}} = up;

$display("@%0dns p1 %x p2 %x p3 %x p4 %x",$time,p1,p2,p3,p4);

y = {>>{ a, b, c }};

$display("@%0dns y %x",$time,y);

// Below line should give compile error

//j = {>>{ a, b, c }};

d = {>>{ a, b, c }};

$display("@%0dns d %x",$time,d);

end

endmodule

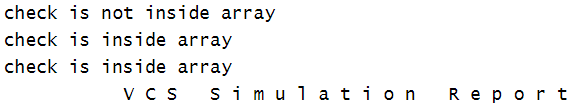

inside 操作符

看例子:

module set_member();

int array [$] = {1,2,3,4,5,6,7};

int check = 0;

initial begin

if (check inside {array}) begin

$display("check is inside array");

end else begin

$display("check is not inside array");

end

check = 5;

if (check inside {array}) begin

$display("check is inside array");

end else begin

$display("check is not inside array");

end

check = 1;

// Constant range

if (check inside {[0:10]}) begin

$display("check is inside array");

end else begin

$display("check is not inside array");

end

end

endmodule

6078

6078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?