完成原理图后,必须做这样几件事情,否则设计可能前功尽弃。

第一:DRC检查,检查设计中的一些单端网络,或者其他简单错误;

第二:输出原理图,用来调试时候方便查看;

第三:导出BOM,用来物料采购;

第四:导出网表,用来在allegro中绘图;

第五:处理网表导出过程中的一些错误;

1. DRC检查

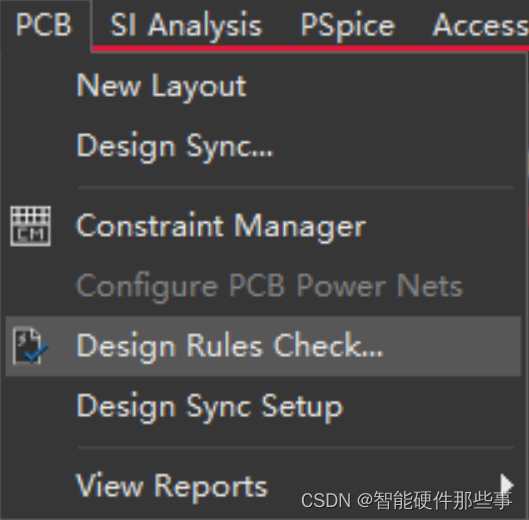

在PCB中,选择Design Rules Check,进入DRC检查界面。下面对DRC选项进行讲解。讲解中我们分为两类:一类是必须勾选的,也就是必须做的DRC检查。另外一类是不必做的DRC检查。

1.1 DRC选项

1. 在线DRC: 默认选择开启,在原理图设计时,能够实时更新DRC状态;

2. DRC Action:

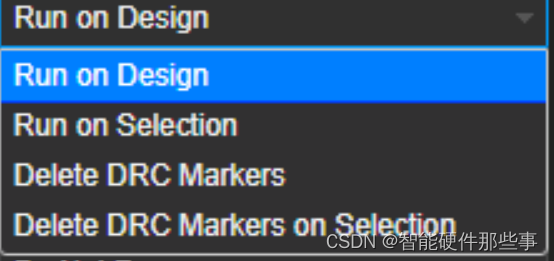

默认是Run on Design。也就是整个设计范围内进行DRC检查。

其中Delete DRC Markers的作用是:选择此选项,再Run DRC,可以把上次产生的DRC Marker删除。

3. Use Properties: 默认为Instance,这个不需要改动;

4. Warning: 默认为Create DRC Markers,就是创建DRC标志;

5. Waived DRC: 就是手动免除的DRC, 默认不显示;

6. Show DRC Output: 默认为DRC 窗口显示;

7. Report: DRC报告保存路径。注意:路径中不能有中文。

上面的DRC选项保持默认即可。

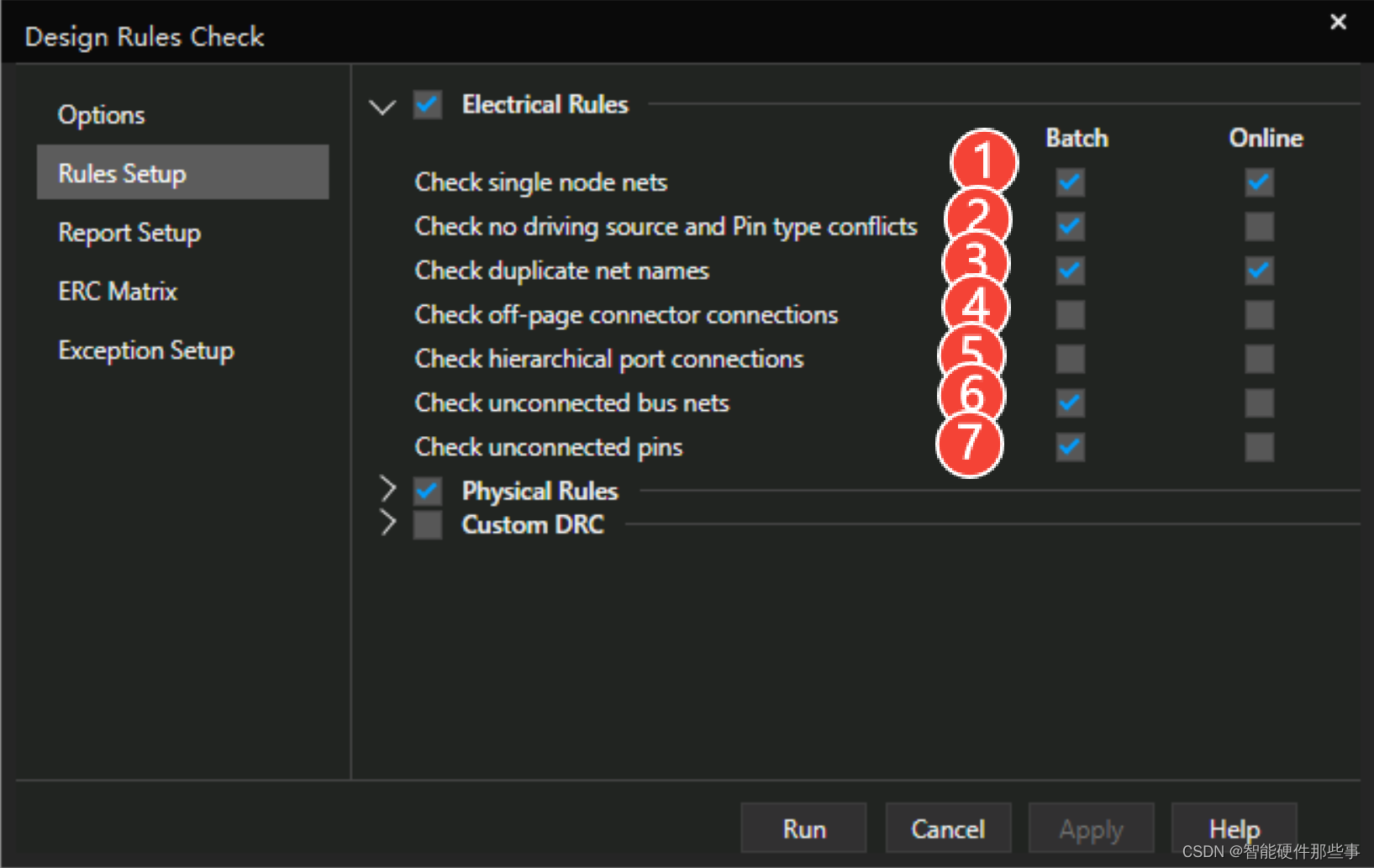

1.2 DRC规则设置

DRC规则设置一般也保持默认即可,但是我们还是有必要快速了解一下,DRC检查都检查了那些东西?

1. 检查单端网络:比如如果一个网络名为SPI_CS,另外一个网络名为SPI-CS,肉眼很难发现,但是DRC检查就会发现,并且把它标记为单端网络。

2. 检查管脚类型冲突:主要检查电源是否已经链接,检查输出和输出是否匹配;

3. 检查重复网络:检查网络名是否有重复;

4. 检查off-page:当用到多页原理图时候,页面和页面之间连接的网络,需要用OFF-PAGE进行标记。

5.检查层级连接:复杂原理图一般采用层级连接,这个用的不多;

6. 检查未连接的总线:当用到总线时,会进行检查;

7. 检查未连接管脚:有些管脚未连接这里会记录。

1.3讲解ERC矩阵

ERC矩阵中,需要了解一下他们的原理。

例如第三行第三列,有个红色的E。这里说明:如果Output和Output接在一起,就会报错。

第三行第二列有黄色的W,说明如果Output和Bidirectional接在一起,就会报警告。

通过这个矩阵,我们可以设置不同具体的DRC规则。

一般来说,我们不需要修改这个矩阵,按照默认即可。

1.4查看DRC错误

********************************************************************************

*

* Design Rules Check

*

********************************************************************************

--------------------------------------------------

Checking Schematic: SCHEMATIC1

--------------------------------------------------

Checking Electrical Rules

Checking For Single Node Nets

Checking For Unconnected Bus Nets

Checking Physical Rules

Checking Pins and Pin Connections

--------------------------------------------------

Checking Schematic: SCHEMATIC1

--------------------------------------------------

Report for Invalid References

Report for Duplicate References

--------------------------------------------------

Checking Entire Design: TPRJ1

--------------------------------------------------

Reporting Unused Refdes in multiple part packages

Part Quantity Reference

-----------------------------------------------------------------------------------------

完成DRC后,在session.log中,会呈现对应的DRC报告。报告中会展示检查了哪些部分。上面的内容是没有错误的。如果有错误,就会在各自部分进行展示。

2.打印原理图

在这里我们学习如何打印原理图。这一步骤一定不要跳过,因为当你后续面试时,完全可以把打印出来的原理图作为简历的一部分,呈现给面试官。

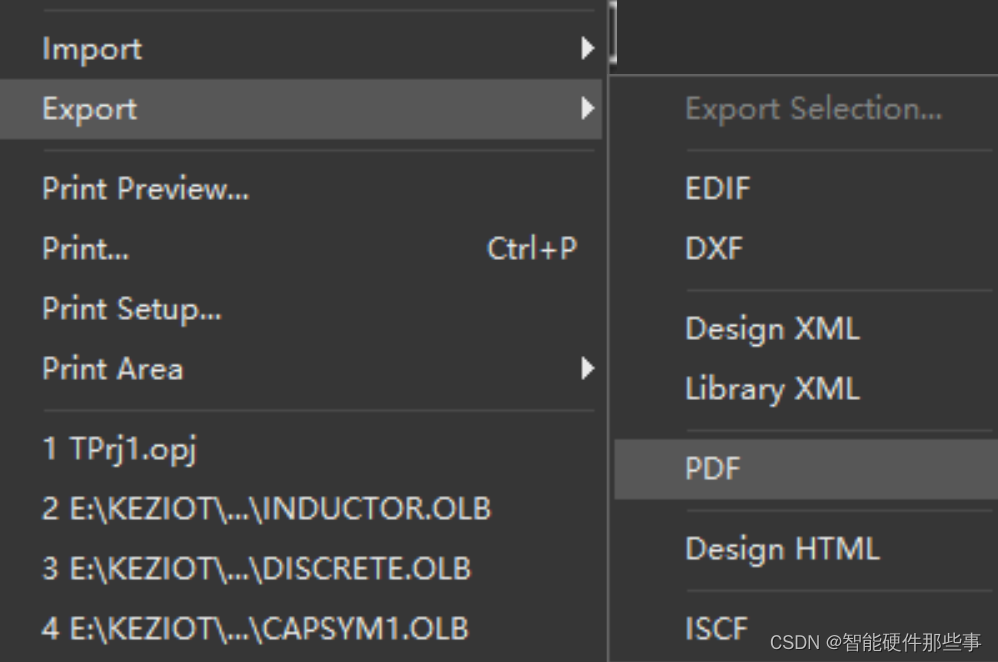

我们采用Export PDF的方式完成打印。这样输出的PDF文件,能够单列每个原件,使用起来非常方便。

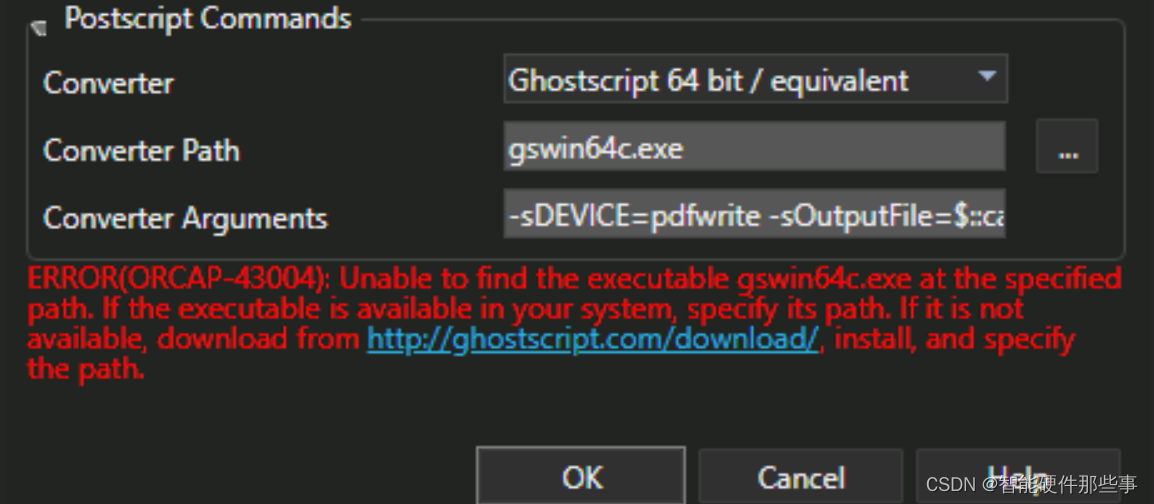

选中输出的是,会提示没有找到对应的PDF工具。这时候我们需要到对应的网址下载安装工具。

我们可以到这个网址下载:

Ghostscript官方版_Ghostscript官方版免费下载[图片浏览]-下载之家

下载到默认目录即可。这个文件尺寸不大。下载完之后,需要指定一下路径

c:\program files\gs\gs9.52\uninstgs.exe

路径指定成功后,就会变成绿色。这时表示能够顺利打印PDF了。

顺利输出的PDF文件为PS格式的,这个格式只能采用adobe acrobat dc来打开。用acrobat dc打开后,直接保存文件即可。

3.输出料单

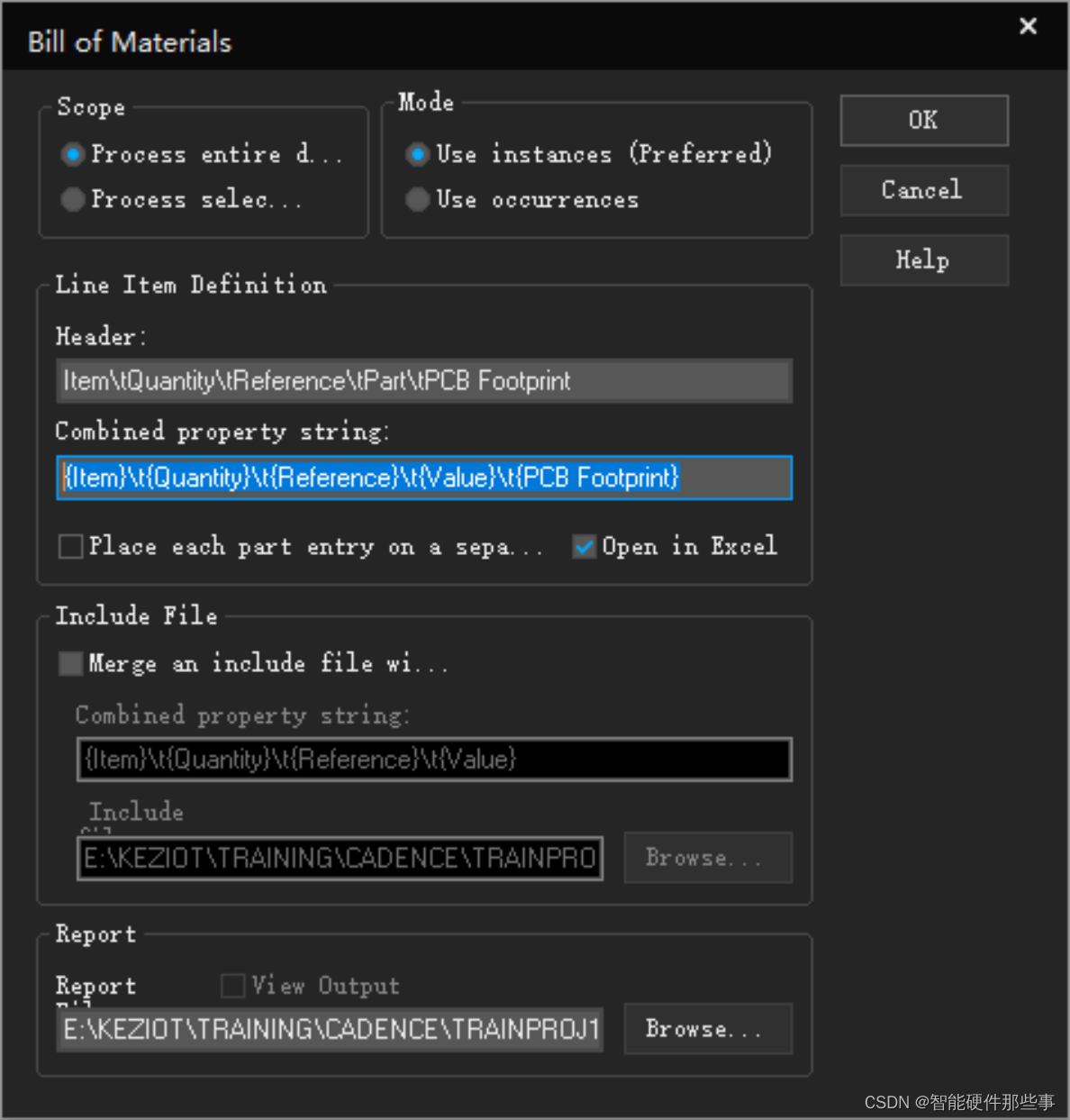

Item\tQuantity\tReference\tPart\tPCB Footprint

{Item}\t{Quantity}\t{Reference}\t{Value}\t{PCB Footprint}

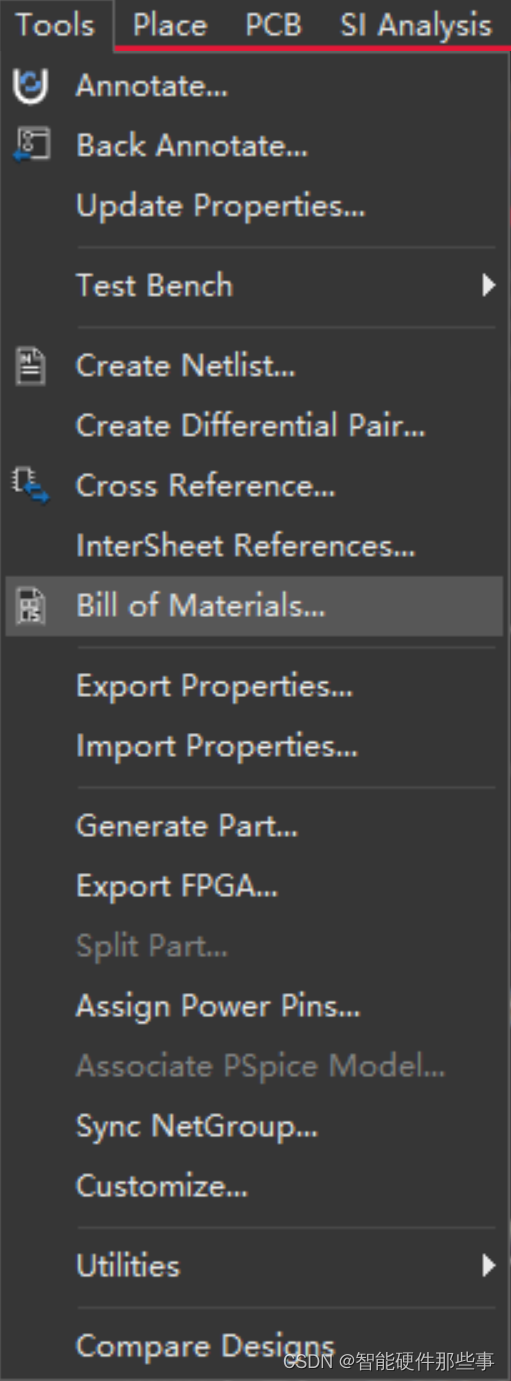

选择Tool->Bill of Material即可输出料单。输出的料单是以BOM结尾的,但是可以用EXCEL文件打开,打开后,即可看到完整料单。

4.输出网表

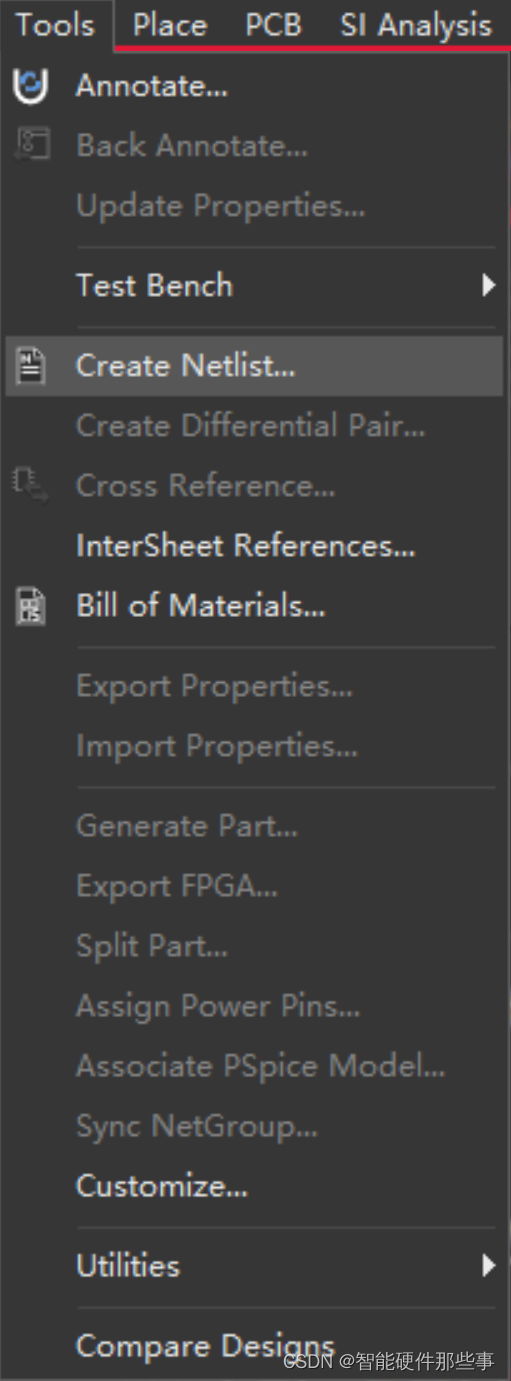

选择Tool->Create Netlist即可导出网表。

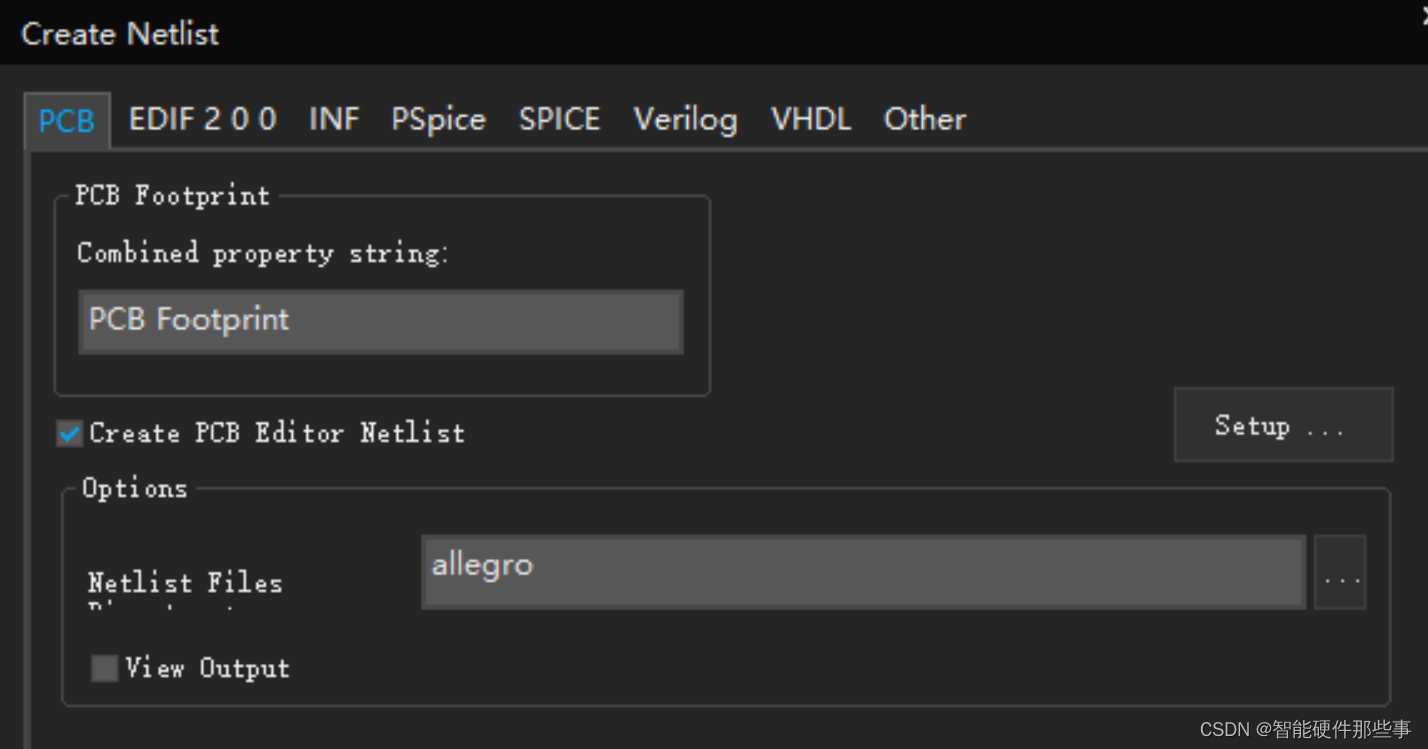

Capture支持多种类型的网表。其中PCB就是指兼容Allegro的网表。我们这里采用默认的Allegro作为设计工具。

输出网表有些类似代码中的编译,通过输出网表可以发现原理图设计中的一些语法错误。同时,对于ALLEGRO来说,唯一输入内容就是网表中的内容。因此,网表其实就是原理图信息。

5. 输出网表中遇到的一些错误和处理方法

(这里有待增加)

4256

4256

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?