目录

2.Vivado中set_output_delay的语法与参数

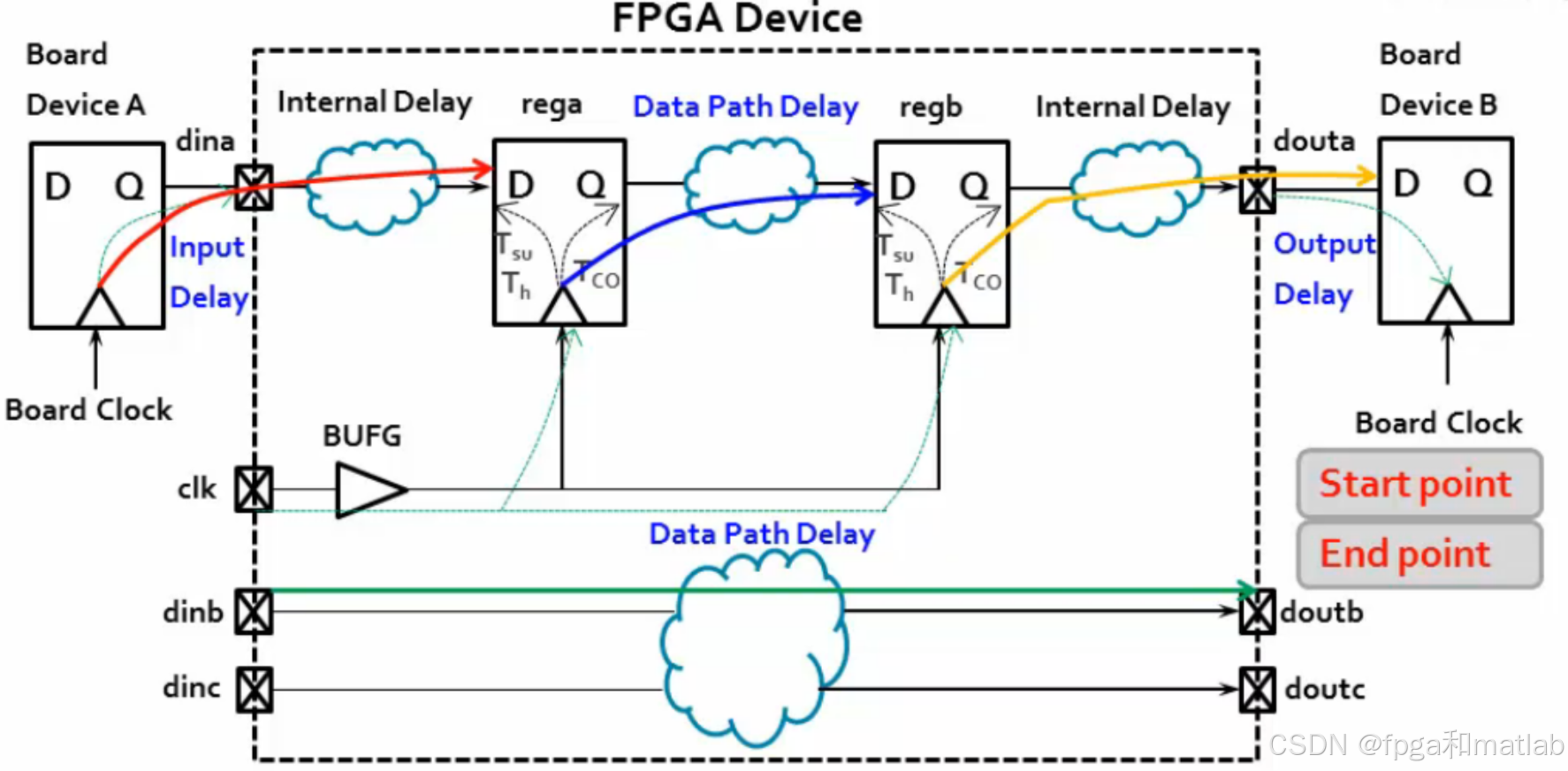

在FPGA设计中,输出延迟约束(Output Delay Constraint)是时序约束的关键部分,用于定义FPGA输出端口到外部芯片输入端口的时序要求,确保外部芯片能正确采样FPGA输出的数据。

1.输出延迟约束的原理

输出延迟约束针对reg2pin路径(从FPGA内部寄存器到输出端口的路径),需考虑外部芯片的建立时间(Setup Time) 和保持时间(Hold Time),以及PCB走线延迟等因素。其核心是通过set_output_delay命令,告诉时序分析工具FPGA输出数据相对于时钟的最大/最小延迟,从而验证时序是否满足外部芯片的要求。

最大输出延迟(T(output_delay)max):对应外部芯片的建立时间要求,确保数据在外部芯片时钟沿到来前稳定。

最小输出延迟(T(output_delay)min):对应外部芯片的保持时间要求,确保数据在外部芯片时钟沿到来后仍能保持稳定。

2.Vivado中set_output_delay的语法与参数

语法格式:

set_output_delay [-clock <clock>] [-clock_fall] [-max] [-min] [-add_delay] <delay> <objects>-clock <clock>:指定输出延迟参考的时钟(如 FPGA 的输出时钟txclk)。-clock_fall:可选,指定延迟相对于时钟的下降沿(默认相对于上升沿)。-max:指定最大输出延迟(对应外部芯片的建立时间)。-min:指定最小输出延迟(对应外部芯片的保持时间)。-add_delay:可选,用于添加新的约束而不覆盖已有约束(如 DDR 模式下双边沿约束)。<delay>:延迟数值(单位:ns),需根据外部芯片手册和 PCB 走线确定。<objects>:需要约束的输出端口(如data_out)。

下面我们给出几种应用场景下的约束编写方法:

场景1:SDR模式(单沿触发,如上升沿)

外部芯片要求:建立时间Tsetup=2ns,保持时间Thold=1ns,FPGA 输出时钟为txclk,数据端口为data_out。

约束代码:

# 1. 定义输出时钟(假设txclk由MMCM生成)

create_generated_clock -name txclk -source [get_pins mmcm/CLKOUT0] -divide_by 1 [get_ports clk_out]

# 2. 约束最大输出延迟(对应建立时间)

set_output_delay -clock txclk -max 2 [get_ports data_out]

# 3. 约束最小输出延迟(对应保持时间)

set_output_delay -clock txclk -min 1 [get_ports data_out]场景2:SDR模式(下降沿触发)

若外部芯片采样时钟为下降沿,需添加-clock_fall参数:

约束代码:

set_output_delay -clock txclk -max 2 [get_ports data_out] -clock_fall

set_output_delay -clock txclk -min 1 [get_ports data_out] -clock_fall场景3:DDR模式(双边沿触发,上升沿+下降沿都传输数据)

需同时约束上升沿和下降沿的延迟,且用-add_delay避免约束覆盖:

约束代码:

# 上升沿约束

set_output_delay -clock txclk -max 2 [get_ports data_out]

set_output_delay -clock txclk -min 1 [get_ports data_out]

# 下降沿约束(添加-add_delay)

set_output_delay -clock txclk -max 2 [get_ports data_out] -clock_fall -add_delay

set_output_delay -clock txclk -min 1 [get_ports data_out] -clock_fall -add_delay在实际使用过程中,我们需要注意的是:

时钟域一致性:确保-clock指定的时钟与FPGA输出数据的驱动时钟属于同一时钟域。

延迟数值来源:需结合外部芯片手册的建立/保持时间、PCB走线延迟(可通过阻抗、长度计算)综合确定。

DDR模式的-add_delay:双边沿约束时必须添加该参数,否则后定义的约束会覆盖先定义的约束。

8474

8474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?