✅ 博主简介:擅长数据搜集与处理、建模仿真、程序设计、仿真代码、论文写作与指导,毕业论文、期刊论文经验交流。

✅ 具体问题可以私信或扫描文章底部二维码。

(1) 时间交织模数转换器时间误差分析与问题总结

时间交织模数转换器(TI-ADC)通过多个子ADC的并行采样来实现高速采样率,广泛应用于通信、雷达和医疗成像等领域。然而,TI-ADC的实际性能常受到通道间失配误差的限制,尤其是时间误差问题。时间误差主要体现在各子ADC之间的采样时钟相位偏差上,导致系统输出信号在频域内出现杂散分量,从而严重降低信噪比(SNR)和有效位数(ENOB)。时间误差的处理难度较大,主要体现在以下几个方面:

-

宽带输入信号处理困难:对于宽带信号,子ADC无法满足奈奎斯特采样定理,导致时间误差校准方向的确定性受限。

-

算法复杂度与硬件实现冲突:传统校准算法需要高复杂度的硬件资源,难以满足低功耗、低成本设计需求。

-

动态性能优化不足:现有算法在处理高精度TI-ADC时,校准速度和精度无法同时满足设计需求。

在深入分析时间误差产生机理和其对系统性能的影响后,本文针对以上问题设计了三种全数字校准算法,从结构设计、算法改进和硬件实现三个层面进行优化,提升TI-ADC系统的动态性能。

(2) 全数字校准算法设计与改进

-

基于通道复用技术的校准结构设计 本文提出了一种基于通道复用技术的时间误差校准结构。通过在子ADC通道间引入复用单元,降低硬件实现复杂度,使硬件资源的需求不随通道数的增加而显著提升。校准结构结合改进的时间误差估计算法,能够有效解决宽带输入信号下的校准方向问题。

-

特点:在不满足子ADC奈奎斯特采样定理的情况下,利用通道复用技术扩展系统带宽,使系统适应宽带输入信号。

-

优势:通过减少通道硬件的冗余设计,显著降低功耗,同时保证校准精度。

-

-

校准方向纠错算法设计 针对输入信号不满足奈奎斯特采样定理时校准方向出错的问题,本文设计了一种校准方向纠错算法。算法通过动态调整误差估计方向,确保校准结果始终指向误差最小化路径。

-

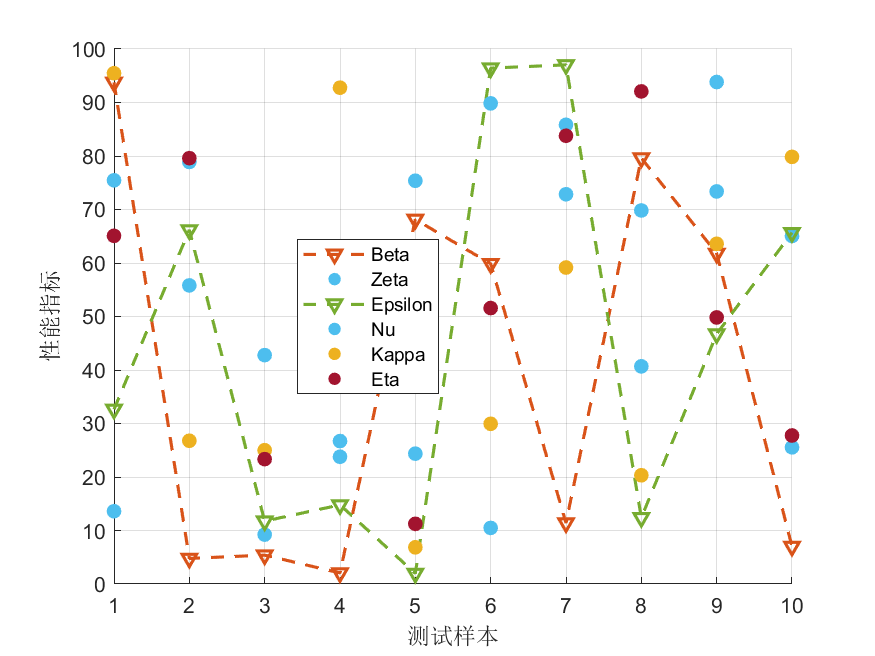

实现方法:在每次误差估计后,通过比较校准前后的动态性能指标,如杂散分量功率和信号总功率比值(SFDR),判断校准方向的正确性。若方向错误,动态调整校准参数。

-

实际效果:与传统算法相比,纠错算法对宽带信号表现出更好的适应性,使校准后的系统性能显著提升。

-

-

带参考通道的时间误差校准算法设计 为提升高精度TI-ADC校准效率,本文设计了一种带参考通道的时间误差校准算法。在TI-ADC系统中引入参考通道,通过变步长LMS算法动态优化时间误差。

-

核心思想:利用参考通道对时间误差进行全局参考,避免因单通道数据波动而导致的误差积累。

-

变步长LMS算法:在算法迭代过程中,根据误差变化幅度动态调整步长大小,使校准过程快速收敛,同时保持较高的校准精度。

-

实验验证:针对理想ENOB分别为8 Bits、12 Bits和20 Bits的TI-ADC进行FPGA验证,校准后的ENOB分别提升至7.81 Bits、11.80 Bits和19.54 Bits。

-

(3) 时间误差估计与补偿算法的优化

本文提出了一种基于信号与其导数正交性的时间误差估计算法,并对传统的基于Taylor展开的时间误差补偿算法进行了改进。

-

时间误差估计算法 利用输入信号在理想情况下与其一阶导数正交的特点,构建误差估计模型。在实际采样数据中,通过最小化信号与其导数的相关性来实现误差估计。

-

优点:该算法能够避免复杂的频域转换操作,直接在时域内完成时间误差的精确估计。

-

-

改进的时间误差补偿算法 传统时间误差补偿算法基于Taylor展开的低阶近似,精度受限于展开项数。本文对其进行了改进:

-

在补偿模型中引入高阶项修正误差,提升补偿精度;

-

结合输入信号的统计特性,自适应调整补偿参数,使算法适应不同信号条件。

-

实验结果:通过MATLAB/Simulink仿真,验证了改进算法在宽带信号下的稳定性和精确性,补偿后系统的动态性能提升显著。

-

(4) 多平台验证与结果分析

为了验证所提出算法的有效性,本文在MATLAB/Simulink、Modelsim和FPGA开发平台上进行了多平台验证。

-

MATLAB/Simulink仿真

-

在MATLAB中搭建TI-ADC系统模型,输入多种宽带信号进行校准仿真。

-

结果表明,提出的算法能够在宽频带范围内有效校准时间误差,提升系统的信噪比和ENOB。

-

-

Modelsim仿真

-

在Modelsim中进行硬件级仿真,验证校准算法的逻辑实现和资源消耗。

-

结果显示,改进的校准算法硬件资源需求较低,适用于低功耗设计。

-

-

FPGA验证

-

在FPGA开发板上实现完整的TI-ADC校准系统,验证实际硬件环境下的校准效果。

-

对于理想ENOB分别为8 Bits、12 Bits和20 Bits的TI-ADC,校准后的实际ENOB显著提升,证明了算法的工程适用性。

-

% 时间误差校准主函数

clc; clear;

% 参数初始化

numChannels = 4; % 子ADC数量

samplingRate = 1e9; % 采样率

inputSignal = generateSignal(samplingRate); % 生成输入信号

% 时间误差估计

timeErrors = estimateTimeErrors(inputSignal, numChannels);

% 时间误差补偿

compensatedSignal = compensateTimeErrors(inputSignal, timeErrors);

% 性能评估

[snrBefore, enobBefore] = evaluatePerformance(inputSignal);

[snrAfter, enobAfter] = evaluatePerformance(compensatedSignal);

fprintf('校准前SNR: %.2f dB, ENOB: %.2f Bits\n', snrBefore, enobBefore);

fprintf('校准后SNR: %.2f dB, ENOB: %.2f Bits\n', snrAfter, enobAfter);

% 时间误差估计算法

function errors = estimateTimeErrors(signal, numChannels)

% 实现基于正交性的时间误差估计

errors = zeros(1, numChannels);

for i = 1:numChannels

% ... 误差估计逻辑

end

end

% 时间误差补偿算法

function output = compensateTimeErrors(signal, errors)

% 实现改进的时间误差补偿

output = signal;

for i = 1:length(errors)

% ... 补偿逻辑

end

end

3666

3666

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?