以查看上升沿D触发器的仿真波形为例:

上升沿D触发器的设计文件(仅参考):

module moduleName(

input wire clk,

input wire in,

output wire out

);

reg mem;

always @ (posedge clk)

mem <= in;

assign out = mem;

endmodule上升沿D触发器的仿真激励文件(仅参考):

module sim_moduleName(

);

reg clk, in;

wire out;

moduleName U0(.clk(clk), .in(in), .out(out));

initial begin

clk = 0;

in = 0; #100;

in = 1; #100;

in = 0; #100;

in = 1; #100;

in = 0; #100;

$finish;

end

always #50 clk = ~clk;

endmodule一、vivado如何调出仿真波形窗口

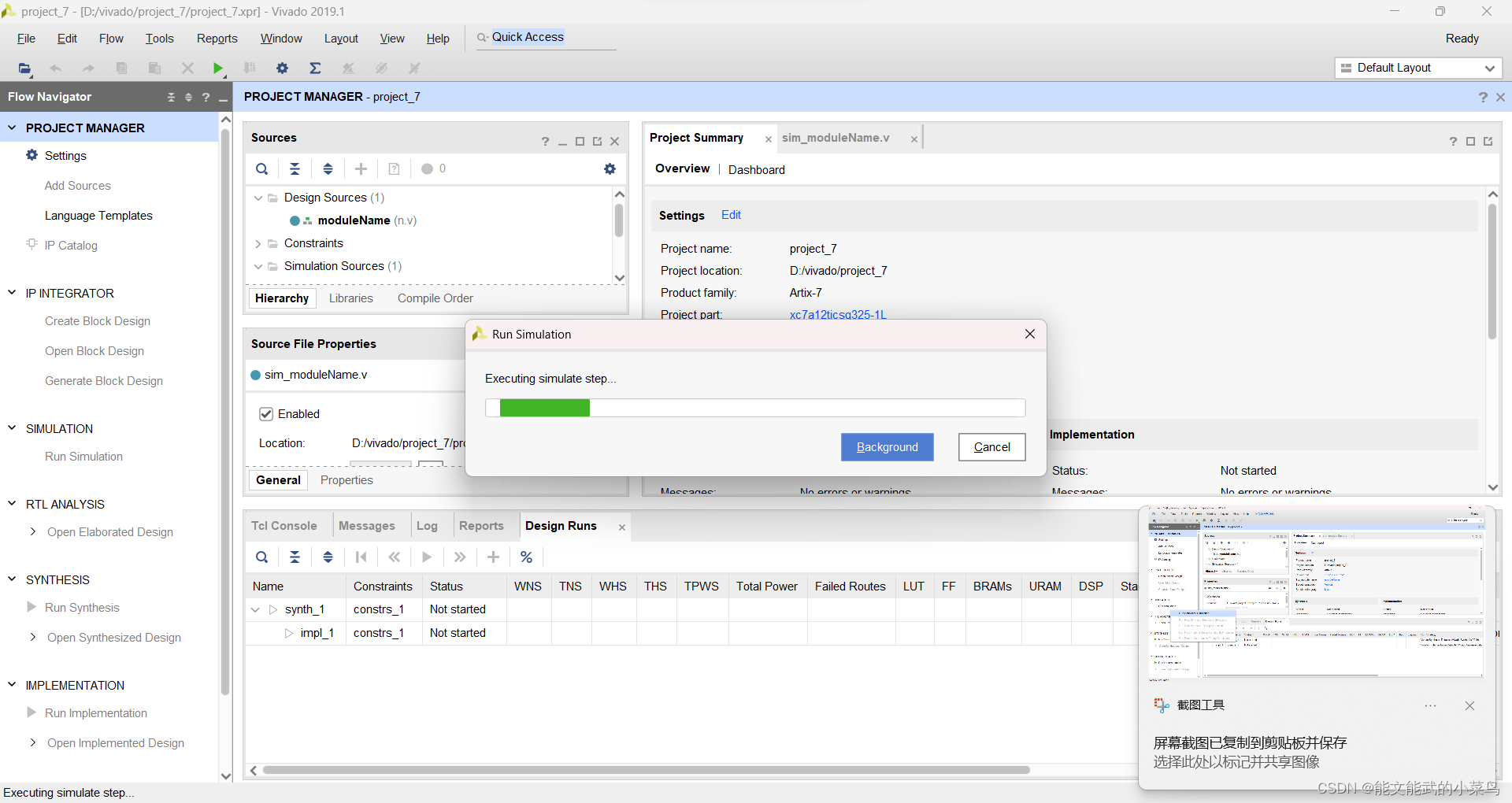

在编写完设计文件和仿真激励文件后:

1、点击左侧项目管理器中的“Run simulation”。

2、在弹出的选项卡中点击“Run Behavioral Simulation”。

3、弹出加载窗口,等待其加载完毕。

4、加载完毕。

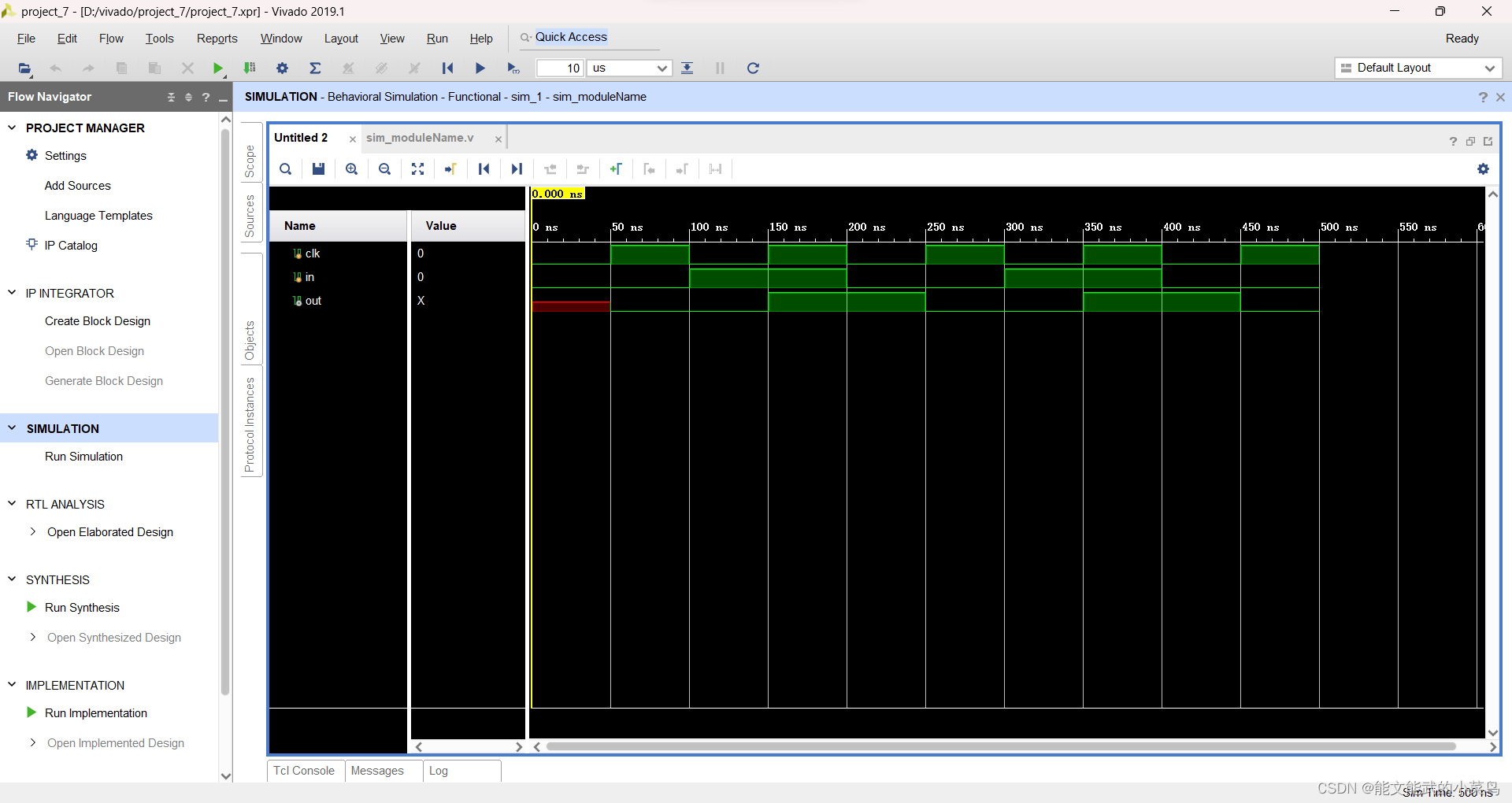

5、点击最右侧窗口左上角的“Untitled 1”,经过窗口调整,就可以观察到如下的仿真波形。

二、仿真波形窗口的手动调整

调整前的窗口如下:

1、点击该窗口右上角的最大化按钮,将窗口最大化,方便后续观察。(最大化效果如下图)

2、点击该窗口上方菜单中的“ |< ”图标(下图选中图标“go to time 0”),将仿真波形调整到从0

时刻开始。

点击后:

3、调整时间轴刻度(下图紫色线框中的部分就是时间轴)。

具体方法为按住键盘Ctrl键,上下滑动鼠标滚轮。(调整后的窗口如下图)

其实,vivado仿真波形窗口上方有一个自适应按键,可以省去以上步骤,直接点击,一步到位。

有时,仿真波形用时较长,超过默认仿真时长,这时候就需要手动操作,使它继续仿真一段时间。

1、不停仿真(时间一直向后推移,仿真一直进行,一般都是有限时间内的仿真,所以一般不使用)。

2、一段仿真(在当前仿真结果后继续仿真一段时间,这个时间可以设置,较常使用)。

上图情况下,如果点击一段仿真按钮,那么仿真波形就会向后延伸10us(如下图)。

三、四种波形状态

1、低电平波形,上图中第一行0ns到50ns之间的波形,此时该信号为低电平。

2、高电平波形,上图中第一行50ns到100ns之间的波形,此时该信号为高电平。

3、未知态波形,上图中第三行0ns到50ns之间的波形(红色波形),往往出现在电路未初始化的时候。

4、高阻态波形,上图中第三行50ns到500ns之间的波形(蓝色波形),往往出现在器件断连的时候(即该信号没有驱动)。

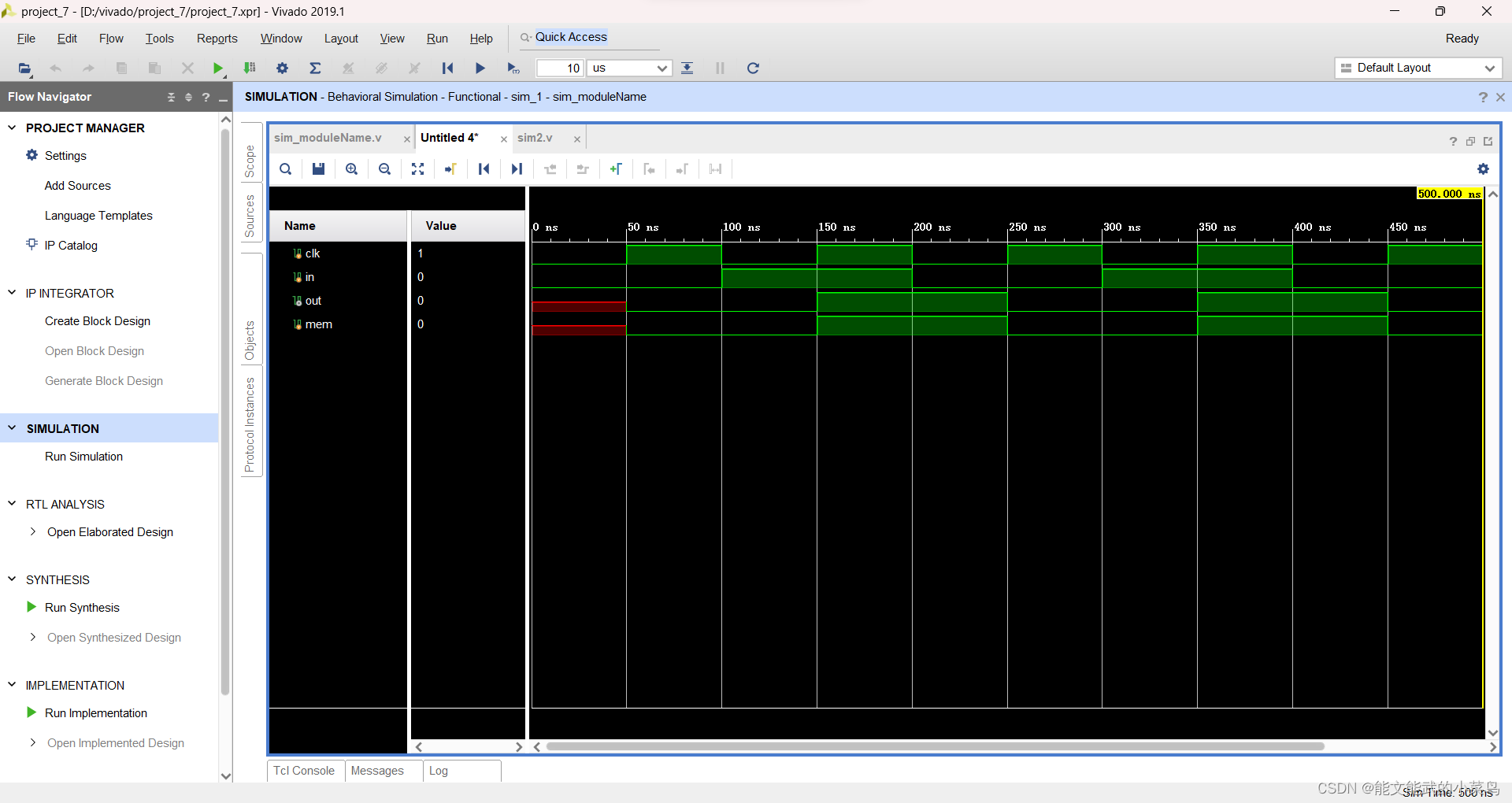

四、观察仿真波形的作用

观察仿真波形可以对自己设计的电路进行逻辑上的验证(其实仅观察波形图并不能确定电路结构,甚至连电路类型都无法分辨,想要确定电路结构,还需要参考本身的设计文件)(对于一些较复杂的电路,需要考虑全部情况,只有每种情况都符合设计功能才能称为验证成功),下面利用仿真结果对示例中设计的D触发器进行验证:

第一行为时钟信号clk,第二行为输入信号in,第三行为输出信号out。当clk的上升沿到来,out的值就瞬间变为in的值。符合D触发器的功能,所以该D触发器的逻辑设计正确。

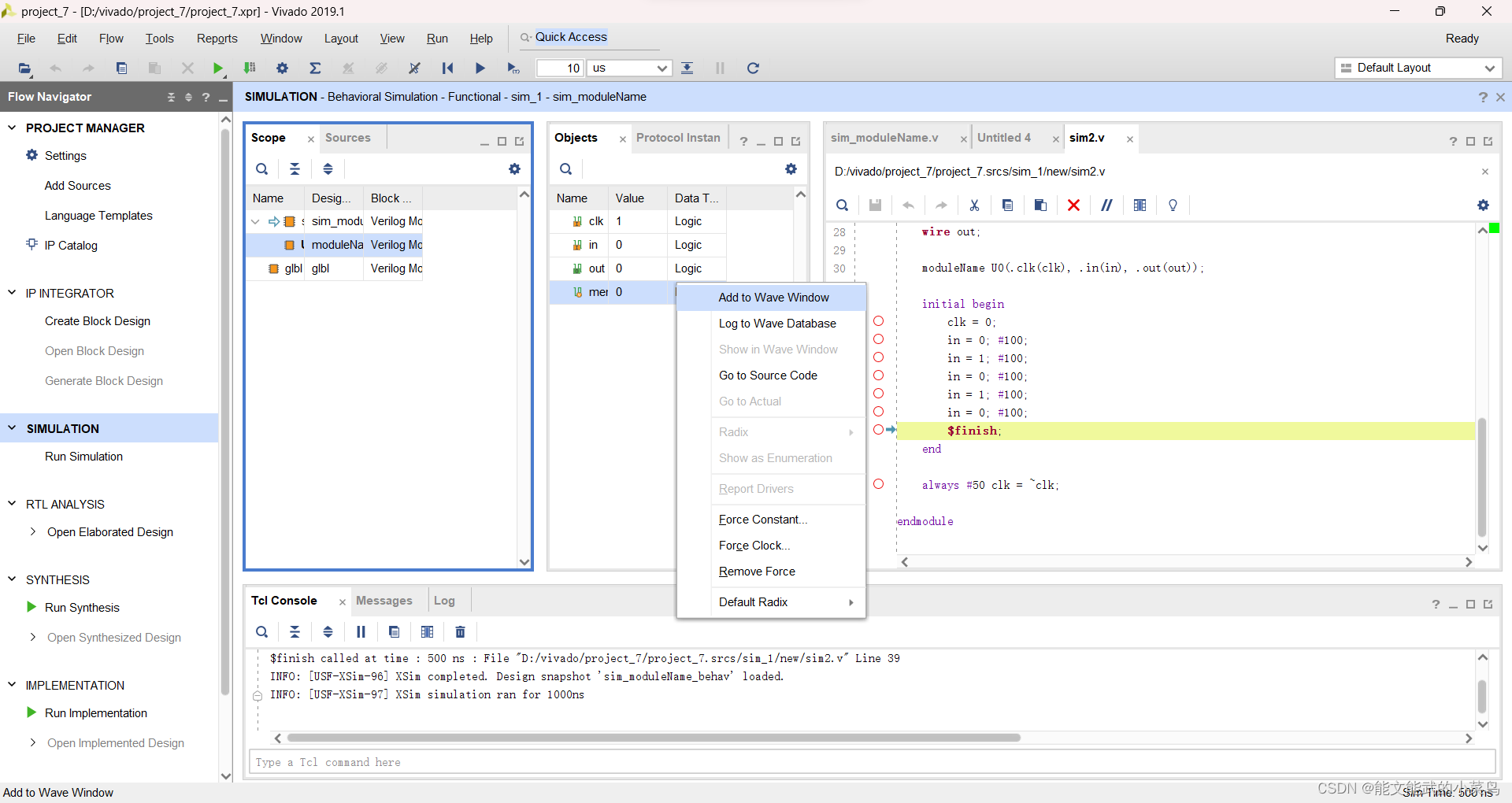

五、查看内部变量的仿真波形

对于一些含有内部变量或者内部寄存器的模块(寄存器堆模块、存储器模块等),我们需要手动调整才能看到它们的内部变量或者内部寄存器的波形图。示例的D触发器含有内部寄存器型变量mem,我们可以通过以下操作查看其波形:

1、在仿真界面点击Scope。

2、在Scope窗口找到想要的内部变量所属的模块,点击。

3、在弹出的Objects窗口,找到想要的内部变量,鼠标右键单击。

4、在弹出的选项卡中点击“Add to Wave Window”。

5、可以看到,内部变量已经出现在仿真窗口左侧列表中,只是右侧还未出现其波形。这时只需点击重新仿真按钮即可。

6、调整完成,如下图,内部变量mem的波形已经出现在仿真波形窗口。

六、注意事项

每次仿真只能针对一个仿真文件,即仿真部分的顶层文件。如果对同一项目中的多个设计文件分别进行仿真,需要一个一个的仿真,并且每次都需要把顶层仿真文件调整为与设计文件相对应的仿真激励文件,必要时可以将其他仿真文件Disable掉(具体步骤为:在Sources窗口下对应位置右键单击想要disable的文件,在弹出的选项卡中选择disable file,如下图,注意不要点击Remove File from project,容易出现问题)。

6511

6511

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?