用Vivado进行硬件调试,就是要插入ila核,即“集成逻辑分析仪”,然后将想要引出来观察的信号连到这个核的probe上。

首先第一步,需要把想要观测的信号标记出来,即mark_debug,有两种mark_debug的方法,我用verilog写了一个简单的流水灯程序,只有几行代码,如下:

- module main(

- input clk,

- input rst,

- output reg [7:0] led

- );

- (*mark_debug = "true"*)reg [23:0] counter;

- always @(posedge clk) begin

- if(rst) begin

- counter <= 0;

- led <= 8'b00000001;

- end

- else counter <= counter + 1;

- if (counter == 24'hffffff)

- led <= {led[6:0],led[7]};

- end

- endmodule

- signal counter : std_logic_vector (23 downto 0);

- attribute mark_debug: string;

- attribute mark_debug of counter : signal is "true";

在信号前面加入mark debug的好处

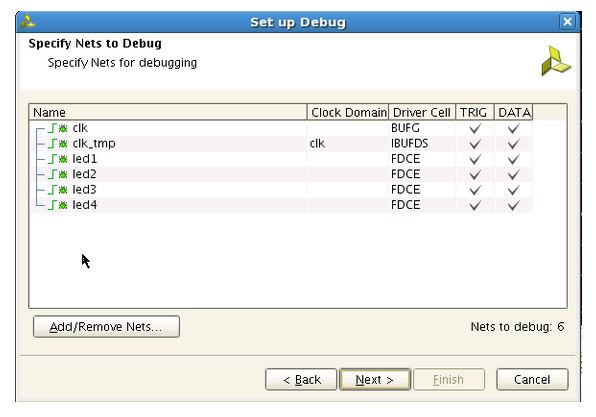

接着第二步就是插入调试内核了,在Vivado界面下方,找到Unassigned Debug Nets,右键选择 set up debug,在接下来的对话框中列出了counter信号的lk domain是CLK_IBUG_BUFG,其trig和data项都打了对勾,表示counter信号既作为触发信号也作为数据信号。

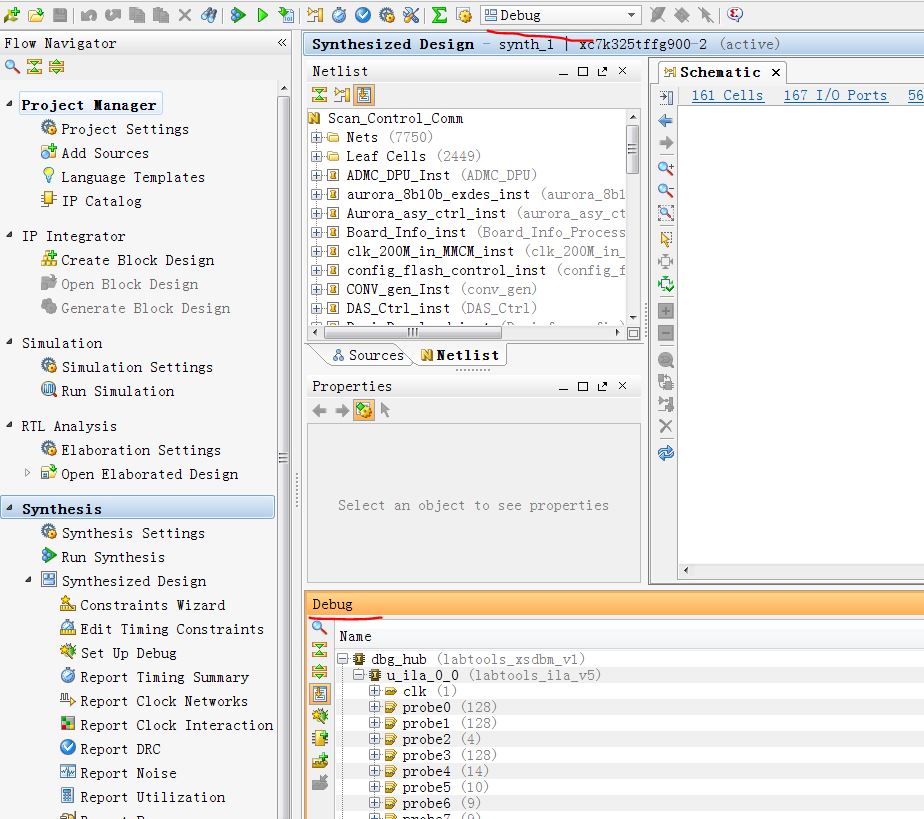

选择next,在接下来的对话框中将enable advanced trigger mode 和enable basic capture mode勾选上,继续next,最后finish,在界面下方的debug窗口显示如下:

选择next,在接下来的对话框中将enable advanced trigger mode 和enable basic capture mode勾选上,继续next,最后finish,在界面下方的debug窗口显示如下:

右键dbg_hub,选择implement debug cores,接着在打开的schematic中,可以看见插入的ila核,其probe端口与counter相连,打开xdc文件,在最后几行多出来这几行代码:

右键dbg_hub,选择implement debug cores,接着在打开的schematic中,可以看见插入的ila核,其probe端口与counter相连,打开xdc文件,在最后几行多出来这几行代码:

- create_debug_core u_ila_0 labtools_ila_v3

- set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0]

- set_property ALL_PROBE_SAME_MU_CNT 4 [get_debug_cores u_ila_0]

- set_property C_ADV_TRIGGER true [get_debug_cores u_ila_0]

- set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila_0]

- set_property C_EN_STRG_QUAL true [get_debug_cores u_ila_0]

- set_property C_INPUT_PIPE_STAGES 0 [get_debug_cores u_ila_0]

- set_property C_TRIGIN_EN false [get_debug_cores u_ila_0]

- set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0]

- set_property port_width 1 [get_debug_ports u_ila_0/clk]

- connect_debug_port u_ila_0/clk [get_nets [list clk_IBUF_BUFG]]

- set_property port_width 24 [get_debug_ports u_ila_0/probe0]

- connect_debug_port u_ila_0/probe0 [get_nets [list {counter[0]} {counter[1]} {counter[2]} {counter[3]} {counter[4]} {counter[5]} {counter[6]} {counter[7]} {counter[8]} {counter[9]} {counter[10]} {counter[11]} {counter[12]} {counter[13]} {counter[14]} {counter[15]} {counter[16]} {counter[17]} {counter[18]} {counter[19]} {counter[20]} {counter[21]} {counter[22]} {counter[23]}]]

- set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

到此为止,成功将要观察的信号引出来,完成了插入调试内核,接着直接运行generate bitstream,即可生成bit文件。

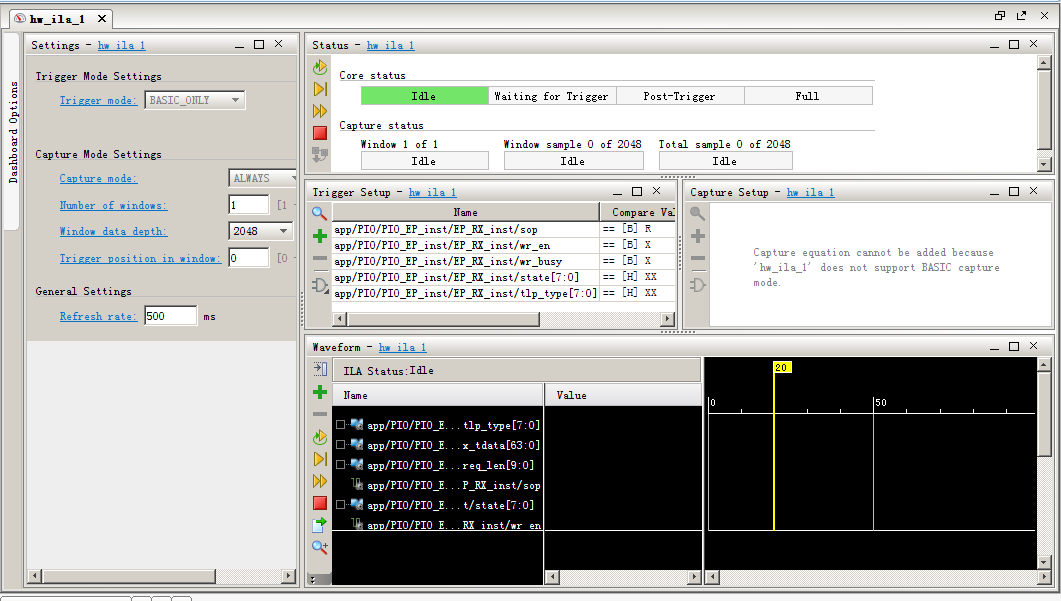

最后一步,连上单板开始调试,用impact将bit文件下载到板卡上,或者在后面hardware manager中选择program device也可以。打开hardware manager,然后open new target,一直next直到结束,即可打开Vivado硬件逻辑分析仪,如下图所示:

要查看波形,必须要有信号触发,将counter信号拖入右方的basic trigger setup窗口,可以设置,想要counter等于何值时触发,右键counter,选择run trigger,并将counter信号添加到波形窗口中,接着便可以在打开的波形窗口中观察counter信号的变化。

要查看波形,必须要有信号触发,将counter信号拖入右方的basic trigger setup窗口,可以设置,想要counter等于何值时触发,右键counter,选择run trigger,并将counter信号添加到波形窗口中,接着便可以在打开的波形窗口中观察counter信号的变化。

硬件调试的流程大致如上述所示,这只是非常简单的一个例子,作为对官网视频教程的一个翻译加补充吧,如果工程较大的话,debug时还会遇到各种问题,就需要一步步慢慢摸索解决啦。

参考官网视频教程,另外在xilinx官网上也可以搜到debug的文档:

http://china.xilinx.com/training/vivado/inserting-debug-cores-into-the-design.htm

http://china.xilinx.com/training/vivado/programming-and-debugging-design-in-hardware.htm

附加两点我曾遇到的小问题:

(1)在进行综合之前,需要将先将xdc约束文件添加到工程中,否则最后write bitstream时出错。Vivado的一个问题就是,有好多ise中综合时就能检测出的错误,而Vivado要等到生成bitstream时才报错。

(2)在打开hardware manager之后,提示vcseserver没有开启,在vivado/2013.4/bin下面运行vcseserver的bat程序即可。

debug工具详细说明

Vivado和ISE相比ChipScope已经大幅改变,很多人都不习惯。在ISE中称为ChipScope而Vivado中就称为in system debug。下面就介绍Vivado中如何使用debug工具。

Debug分为3个阶段:

1. 探测信号:在设计中标志想要查看的信号

2. 布局布线:给包含了debug IP的设计布局布线

3. 分析:上板看信号

一 探测信号

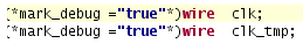

探测信号有2种方法一种是直接在HDL源代码中用(*mark_debug = “true”*)标识出要探测的信号 另一种是 在综合过后的网表文件中添加标志。

1 .在HDL源代码中添加标志

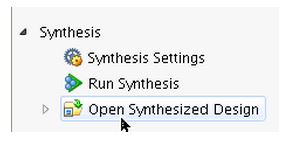

然后点击open Synthesized Design

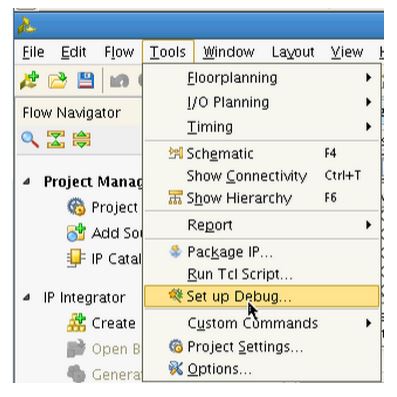

然后点击Tools-> Set Up Debug

点击 Next

点击Add/Remove Nets

点击find会出来所有信号。如果需要添加debug的信号,从左边框中选择所需信号,点击 按 钮加到右边来。如果需要去除不需要的debug信号,从右边框中选择所需信号,点击

按 钮加到右边来。如果需要去除不需要的debug信号,从右边框中选择所需信号,点击 按钮就 去除了。选好信号之后,在右下角点击Ok按钮。

按钮就 去除了。选好信号之后,在右下角点击Ok按钮。

在此框中为所有debug信号选择时钟域,选择debug信号,右键选择Select Clock Domain。注意每一个时钟域对应一个单独的ILA 2.0core。

在此框中选择所需时钟,点击ok

点击next

然后继续下面的Implement 流程

点击Save保存修改后的工程

后面像以前一样等工程跑结束。

2.在网表文件中添加标志

网表文件添加标志,第一步也是打开综合后设计。如下图所示

第二步是打开debug窗口

Open synthesized Design之后,有2种方法来标志debug信号

(1) 第一种方法是在Netlist窗口中选择信号,右键点击Mark Debug

(2) 第二种方法是在Tools中选择Setup Debug 推荐使用此方法

然后和前面一样继续跑工程。

二 上板调试

上板的时候选择Open hardware session ,然后Open a new hardware target

选择next

选择next

选择Next

选择FPGA来配置文件

注意移到另一台电脑看debug信号时,必须将debug_nets.ltx 文件和bit文件一起移过去。如下图红框所示

如果需要设置触发条件,选择Windows –> Debug Probes

在Debug Probe窗口中选择需要设置的信号,然后设置触发条件。在Trigger Pos中可以设置抓取到触发信号跳变前N个时钟周期可以被抓到

fpga验证的步骤一般是:

× 在代码中加入关键字,表示信号要被调试.

× 进行elaboration和synthesis.

× 打开synthesis, 设置debug核.

× 重新进行synthesis和implement以及write bitstream.

1,vivado中debug核的生成:

原来在ise中,要进行fpga的验证,必须生成两个debug核,一个是ICon,另外一个就是ILA,分别对应是控制和收集波形。但是在vivado中,我们只需生成ILA即可,不需生成ICon。

在生成ILA之前,我们要指定哪些信号应该被调试,原来在ise中,如果不用例化的方式的话,我们就必须一点点去net中找哪些信号应该被调试,很不方便,但是在vivado中,我们可以事先在源代码中加入关键字mark_debug="true"来告诉软件这个信号是要被调试的,从而在生成debug核的过程中,这些被调试的信号就直接显示出来了。如下所示:

接着我们对加入关键字的代码进行elaborate和synthesis。等到综合完成之后,我们就要生成debug核了,生成debug核的方式有好几种,这里只说我感觉比较方便的一种,及Open Implemention Design下的Set Up Debug选项,如下所示:

上图中的信号就是我们在verilog源码中标记的要debug的信号,在生成debug核之前,首先要为debug核生成时钟信号,即上图蓝色圆圈标记的部分。这里Set UpDebug是自动为所选信号生成debug核,也就是说我们可以全选上面的信号,然后点击Next就自动生成所需要的debug核。

2,观察调试信号

在debug核生成之后,我们要对设计重新synthesis和implementation,然后生成比特流下载到fpga上进行验证。在配置好bit流和debug文件之后,就会自动出现调试波形接口,如下所示:

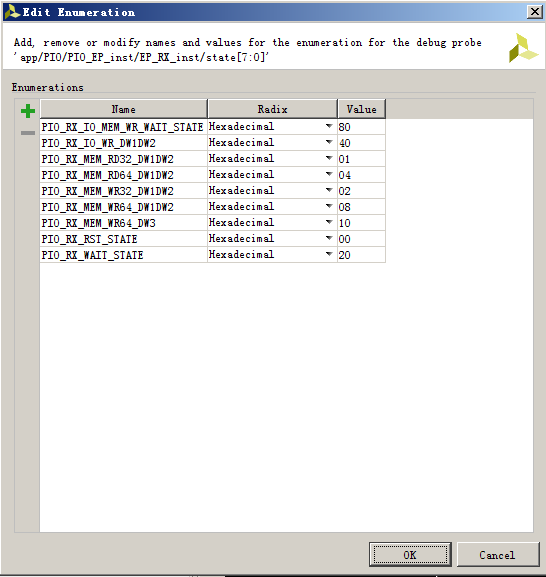

在调试窗口中,可以设置Tigger Setup,这里要说一个对实际观察波形非常方便的一个功能,就是在Trigger Setup窗口中可以选择一个信号,然后编辑enumeration,就是现实信号所代表的含义,而不是只现实数值,这在状态机观察中非常方便,如下图所示:

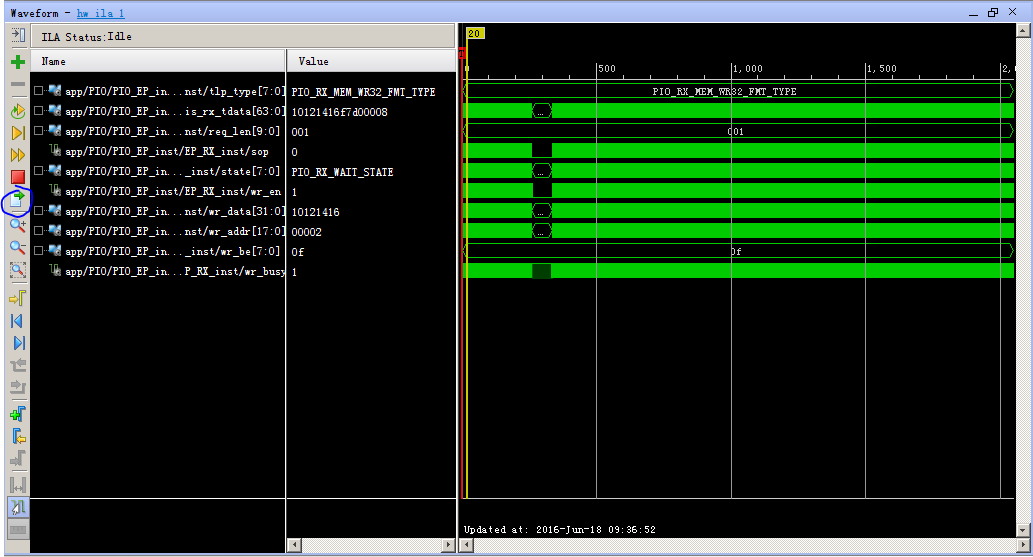

然后在点击Trigger程序就可观察实时的波形了,如下图所示:

如何保存vivado中ila采集到的数据

最后可以选择保存收集到的波形,可以看出上图中的Enumeration的作用(例如PIO_RX_WAIT_STATE不是数值而是名称),这个比chipscope方便多了,因为在chipscope里面好像就无法保存收集到的波形(至少我现在还没有找到),保存(上图蓝色圆圈标记的部分),可以选择不同的格式,Native(vivado本身波形的格式),CSV和VCD,保存成VCD格式,其他软件就能打开了。

导出csv或者vcd文件,vcd文件为通用波形文件,只能用来查看;所以只能通过csv文件解析数据。

5890

5890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?