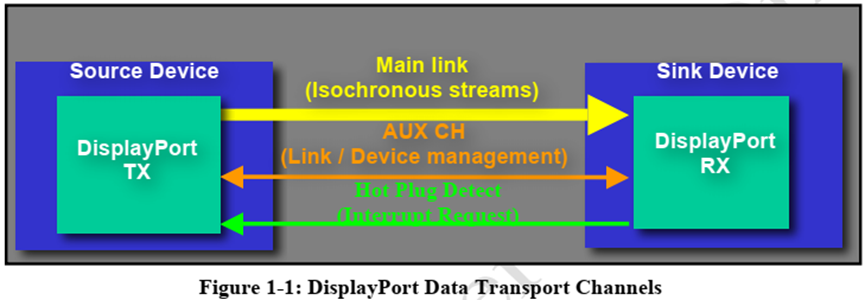

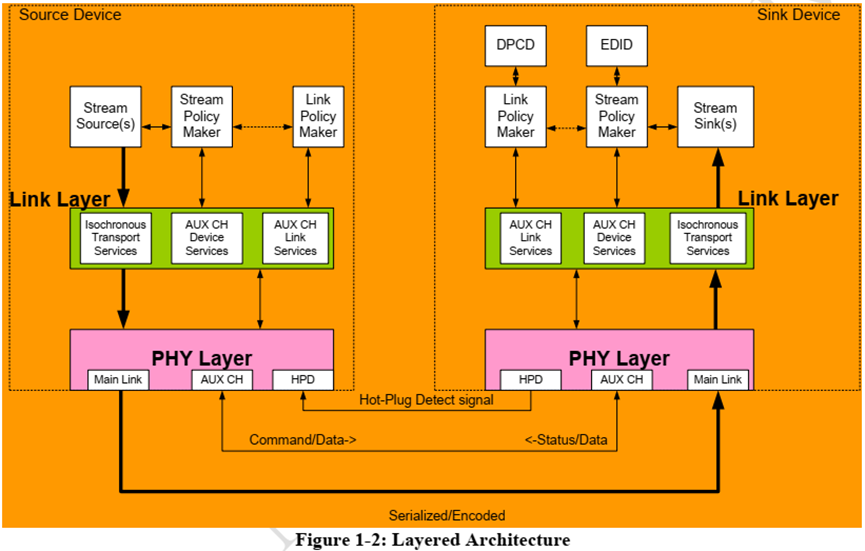

DisplayPort(简称DP)是一个标准化的数字式视频接口标准,具有三大基本架构包含影音传输的主要通道(Main Link)、辅助通道(AUX)、与热插拔(HPD)。

Main Link:用来传输各种类型的视频数据和音频数据,Main Link由1~4对差分线构成,这些数据线是单向的,从source指向sink。Main Link具体需要几对数据线,取决于屏幕的分辨率和颜色位数。

AUX:是一条独立双向半双工的传输通道,它也是一对差分信号线。其数据传输速率1Mbps,用来传输配置参数与指令。具体来说它与EDID及DPCD存储器相连,并通过总线方式读写。

HPD:该项功能是可选的,实现中断以及链路故障通知。

DisplayPort1.4协议可以从以下地址下载https://download.csdn.net/download/cjie221/90649332。

1.结构框图

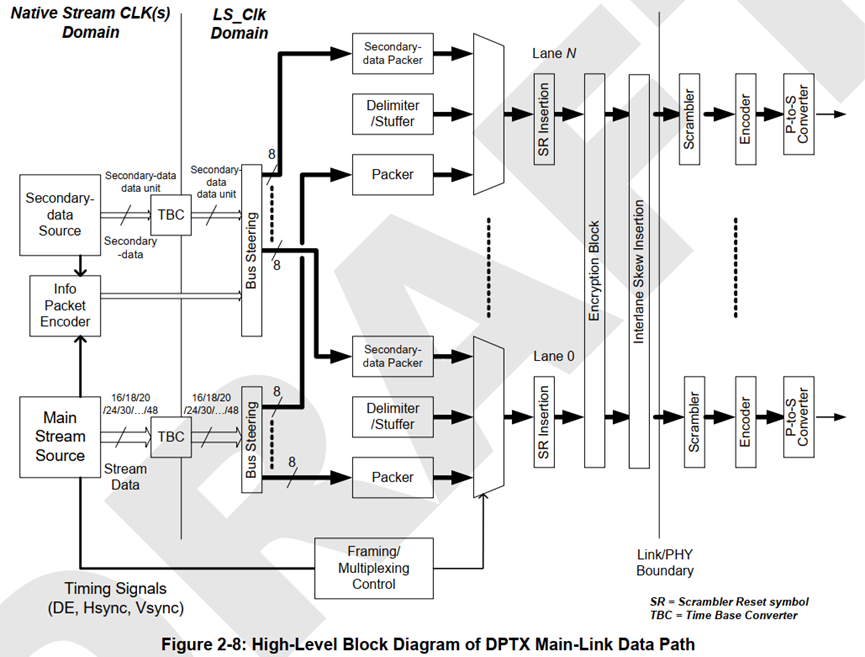

我们根据DP1.4协议的DPTX框图进行说明。在Main Link主通道中主要有视频数据包和第二数据包。视频数据包就是传图像数据,第二数据包用来传输音频数据和其他控制数据,这里我们只介绍视频数据包。另外DP视频流传输还分为Multi-Stream Transport(MST)多流传输模式和Single-Stream Transport(SST)单流传输模式。这两种模式数据格式差别很大。我们先从简单的开始,这里只介绍SST模式。

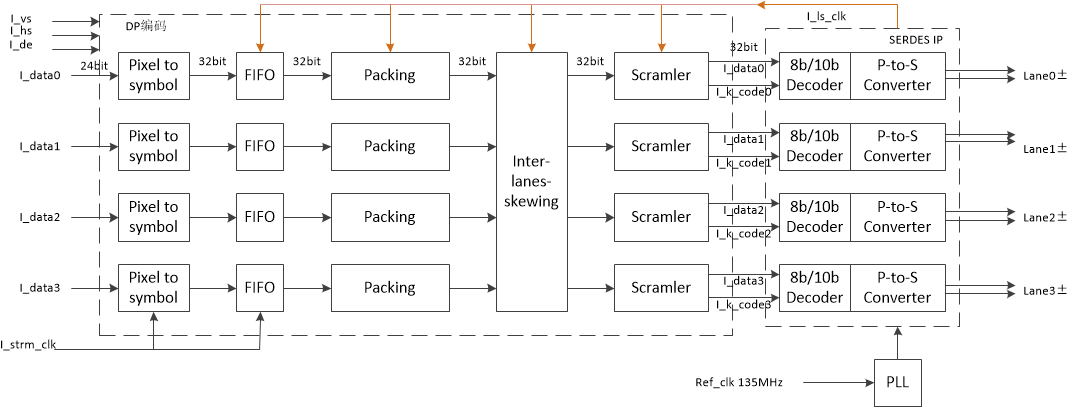

从以下DPTX框图中可以看出数据处理分成两个时钟域,一个是Stream CLK时钟域,一个是LS CLK时钟域。那么这里就涉及时钟域转换,一般用FIFO实现,并且还可以完成数据位宽的转换。Stream CLK时钟域是像素数据,数据位宽一般是24/30bit,LS CLK时钟域是字节数据,一般是8bit,但在FPGA中实现时,为了降低时钟频率,往往采用数据位宽16/32bit。

首先在Stream CLK时钟域一般完成视频数据接收,以及数据位宽转换,然后存入FIFO中。

其次在LS CLK时钟域分别对每个lane的数据进行封包,然后是SR Insertion模块。Encryption模块就是HDCP加密模块,加密模块是可选项。之后是Interlane Skew通道偏移模块,Scrambler扰码模块,还有8b/10b Encoder编码模块,最后是并串转换。

2.实现原理

2.1数据排序

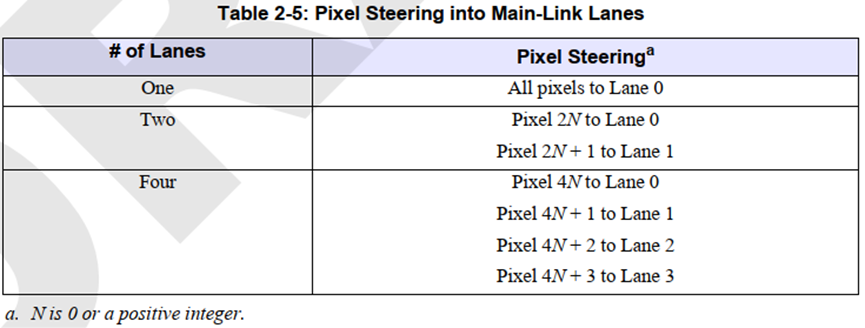

根据DP协议主链路可支持1,2或4 lanes。无论视频流的颜色空间和像素位深度如何,依照下表进行像素数据的填充。

上面框图中的Bus Steering模块功能是就根据lane数对数据进行分配,可以在LS CLK时钟域实现,也可以在Stream CLK时钟域实现。

甚至输入视频源直接根据lane数就按照相应的像素模式输入,这样实现更简单。比如链路数为1 lane,视频输入数据为单像素模式,即每个像素时钟传输1个像素。链路数为2 lanes,视频输入数据为双像素模式,即每个像素时钟传输2个像素。链路数为4 lanes,视频输入数据为四像素模式,即每个像素时钟传输4个像素。这样就可以不使用Steering模块,每个像素直接送到各自的lane,存入相应的FIFO中。

2.2数据封包

根据DP1.4协议,封包的数据是以符号Symbol为单位,一个Symbol 8bit,可以分为数据符号和控制符号。以下控制符号用于组帧。每个控制符号都是一个特殊的K码。

BS: Blanking Start,视频消隐开始标志

BE: Blanking End,视频消隐结束标志,每行第一个有效视频前插入

FS: Fill Start,填充数据开始标志

FE: Fill End,填充数据结束标志

SS: Secondary-data Start,第二数据填充开始标志

SE: Secondary-data End,第二数据填充结束标志

SR: Scrambler Reset,SR symbol用来复位LFSR到初始值

BF: Blanking Fill,增强帧模式填充标志

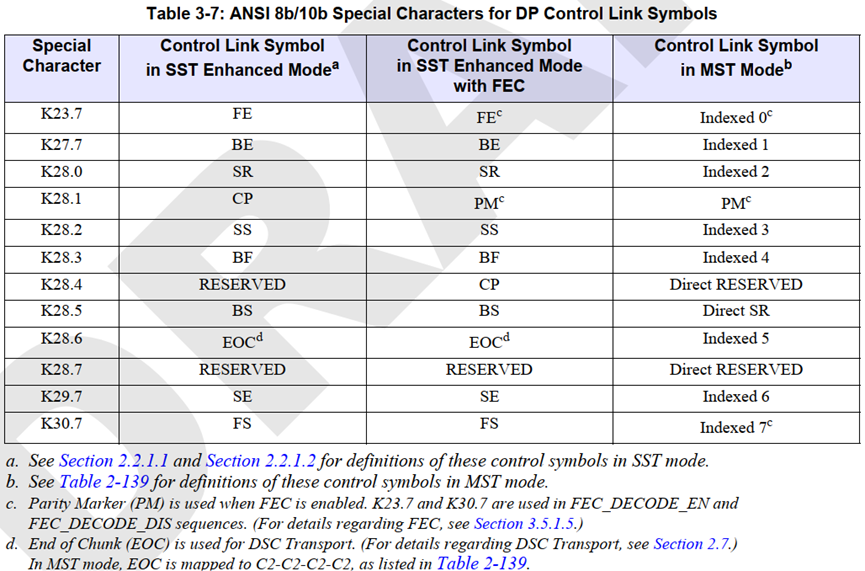

在ANSI标准中8B/10B特殊K码与控制符号对应关系如下表。

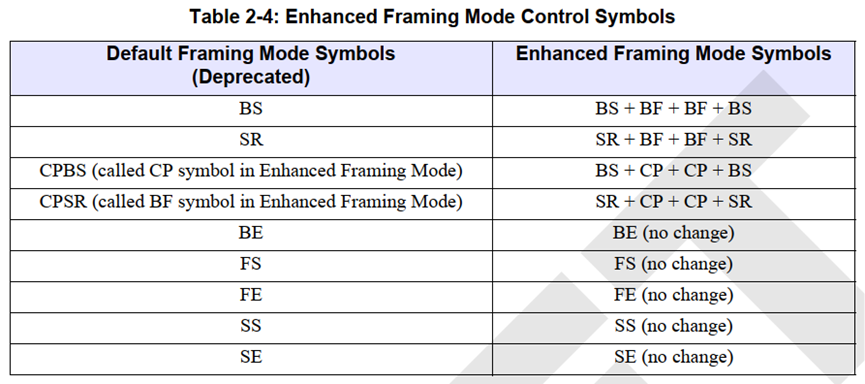

在DP协议中,还有普通帧模式与增强帧模式区别,普通帧模式所有的控制符号都是1个K码,增强帧模式部分控制符号是4个K码的组合,具体控制符号差别如下表。

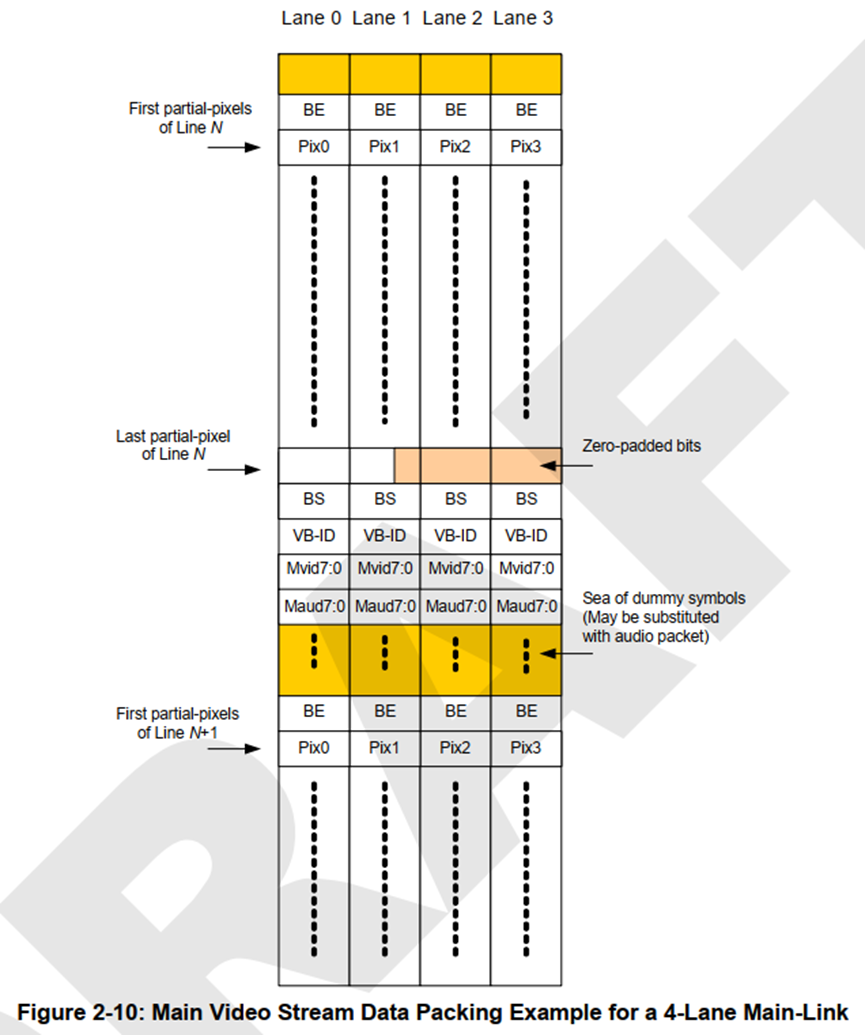

视频流数据封包格式如下图所示。每个lane都从BE(消隐结束)控制符号开始,紧接着是视频数据,然后是BS(消隐开始)控制符号,每个lane的BS后必须跟随VB-ID,Mvid7:0和Maud7:0。之后填充数据零。

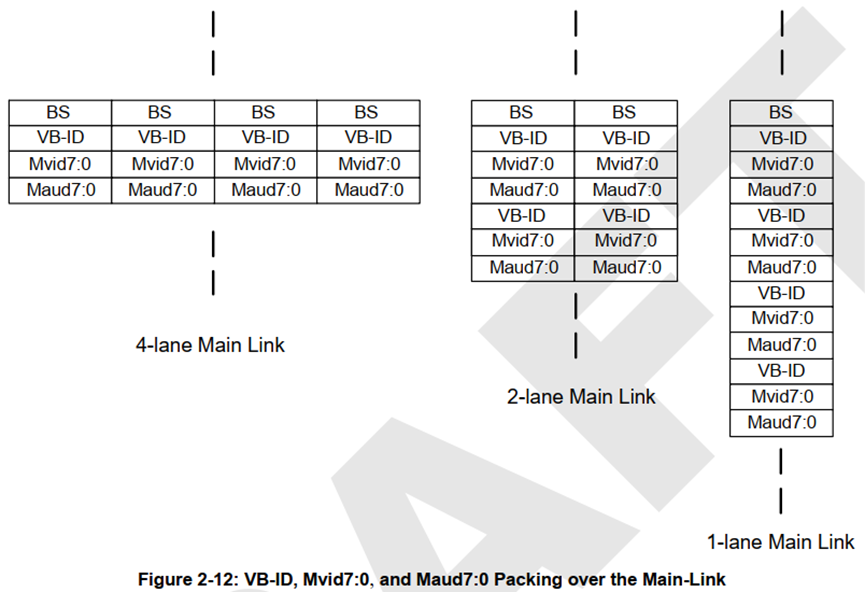

无论lane数量是多少, VB-ID,Mvid7:0和Maud7:0 必须传输4次,如下图所示。

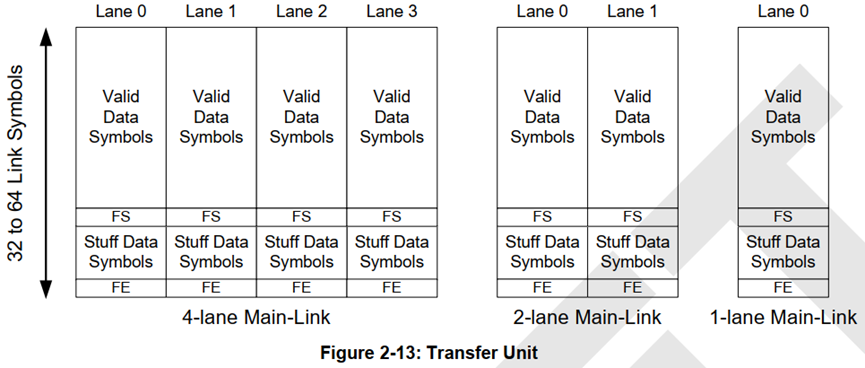

在BE控制符号和BS控制符号之间的视频数据采用一种叫Transfer Unit传输单元的方式传输。每lane的Transfer Unit的大小必须介于32~64个符号。

因为数据打包速率(packed data rates)必须小于等于链路符号速率(link symbols rates)。当打包数据率低于链路符号率时,链路层必须执行符号填充(Symbols stuffing)。也就是说在TU中除了数据,还需要符号填充。

符号填充由stuffing frame symbols和dummy data symbols组成。 Stuffing frame symbols 由FS符号和FE符号构成,位于每个TU (Transfer Unit)之内,dummy data symbols在扰码之前必须是0x00,插在FS和FE之间,如下图所示。

注意,每行视频数据最后一个TU不填充FS和FE,必须全部是视频数据。

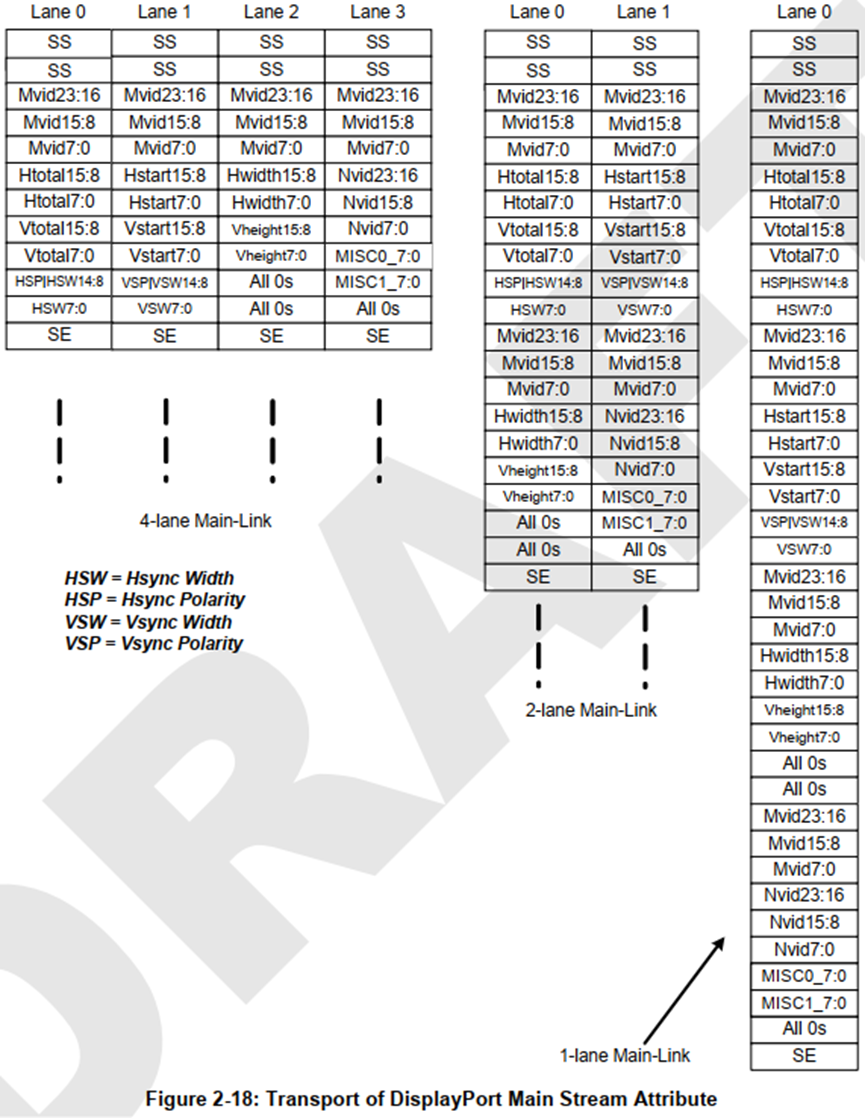

还有DP传输的数据中必须包含视频流的属性信息,叫做主视频流属性数据Main Stream Attribute(MSA)在主视频流的垂直消隐期间每帧发送一次。属性数据包括以下:

(1) 用于视频流时钟恢复的M和N值(24bits each)

(2) 水平总点数和垂直总行数(16bits each)

(3) 水平有效开始点数和垂直有效开始行数(16bits each)

(4) 水平和垂直同步信号极性和宽度(1 bit for polarity and 15 bits for width)

(5) 水平有效点数和垂直有效行数(16bits each)

(6) 杂项0(MISC0, 8bits)

(7) 杂项1(MISC1, 8bits)

通过每lane发送2个连续的SS符号开始,之后就是主流属性数据,最后用SE结束。如下图所示。第二数据包也是用SS符号开始,SE结束,只是区别开始时只用1个SS符号。

根据以上规则,对1lane,2lane,4lane分别处理,在LS CLK时钟域根据视频输入每行的等效长度进行计数,然后分别插入控制符号,以及视频数据,从而完成数据封包。SR符号的插入也可以在封包时完成。

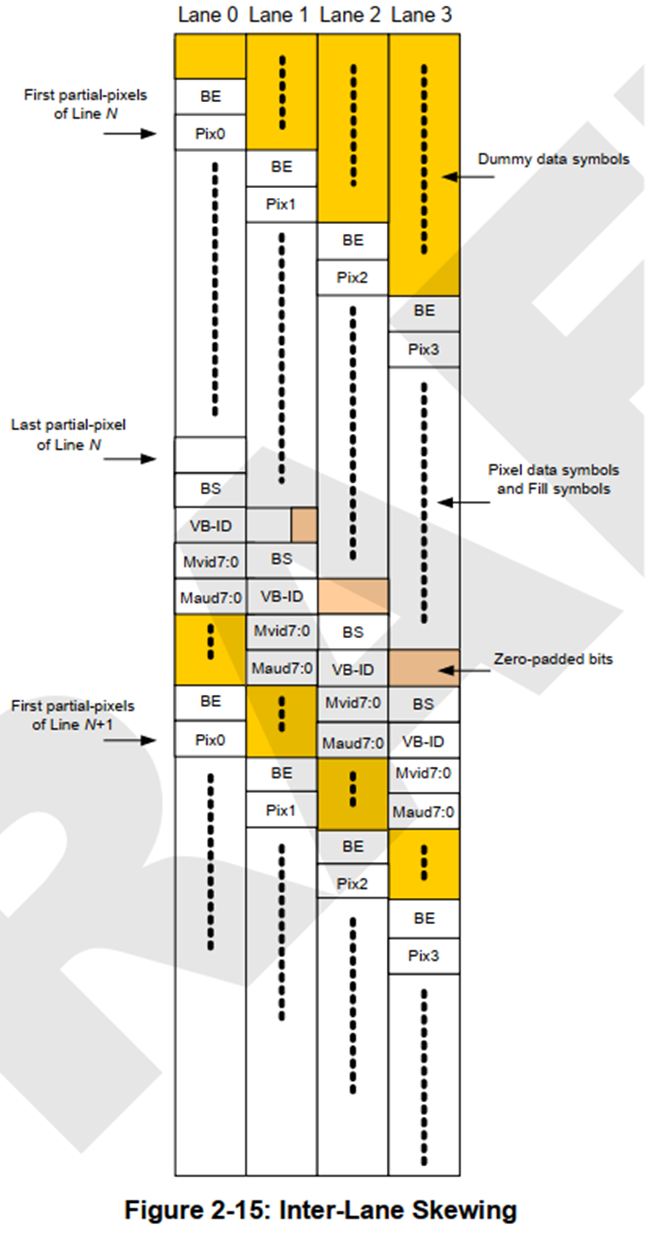

2.3通道间偏移

相邻lane必须插入2个链路时钟LS Clk歪斜,目的是提高链路对外部噪声的抗干扰能力,如下图所示。

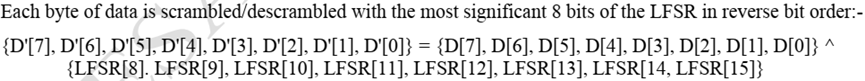

2.4扰码

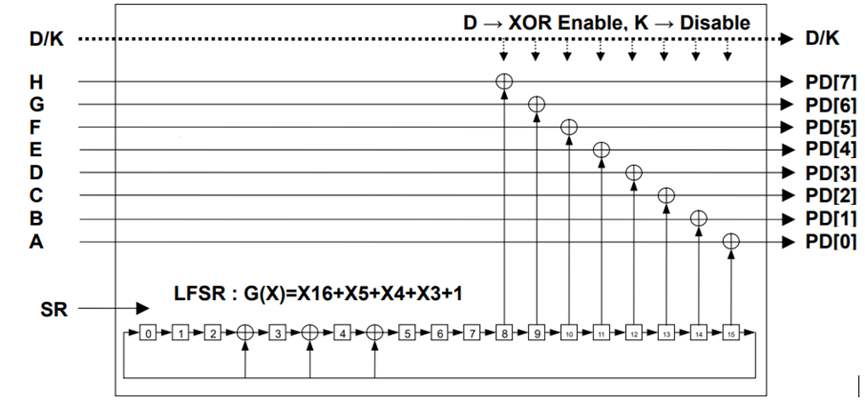

为了减少EMI,在8B/10B编码之前,需进行扰码。16-bit LFSR的多项式为 G(X) = X16 + X5 + X4 + X3 + 1 。数据的每个字节都使用LFSR的最高有效 8 位以相反的位顺序进行加扰/解扰。

SR符号或SR BF BF SR符号序列被用于复位LFSR至初始值FFFFh(或在eDP标准下初始值为FFFEh)。

3.实现框架

根据上述的分析,我们可以将DPTX对应到如下的框架。首先根据lane数,将输入视频数据按对应的像素模式输入,最多是四像素模式。之后是pixel to symbol模块,将像素位宽转成符号位宽。然后存入FIFO。LS CLK时钟域用32bit目的是为了降低处理时钟频率。之后是封包模块,最复杂的操作就在此模块,按行等效长度进行计数,在不同的计数位置,插入控制符号,或者从FIFO中读取视频数据插入。通道间偏移相对简单,寄存器打拍移位就可实现。扰码模块参考DP协议附录,按并行模式实现即可。

因为大多数SERDES IP都集成了8b/10b编解码,所以可以不用单独开发8b/10b编码模块,直接利用SERDES IP就可以实现。至于SERDES IP为什么用135MHz做参考时钟,因为DP的常见速率1.62Gbps/lane(RBR),2.7Gbps/lane(HBR),5.4Gbps/lane(HBR2),8.1Gbps/lane(HBR3)与135MHz都有倍数关系,PLL比较容易产生相应时钟频率。当然如果非要用其他如100MHz时钟做参考时钟,也是可以的,只是有可能PLL输出时钟精度不准,有可能会影响到sink端数据解串。

1668

1668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?