转自:https://www.cnblogs.com/qiweiwang/archive/2011/04/18/2019952.html

Verilog --序列检测器(采用移位寄存器实现)

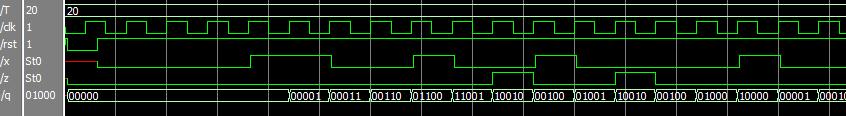

序列检测器就是将一个指定序列从数字码流中识别出来。本例中将设计一个“10010”序列的检测器。设X为数字码流的输入,Z为检测出标记输出,高电平表示发现指定的序列10010.考虑码流为110010010000100101

之前序列检测器看到的都是采用状态机实现,直到偶然看到

https://www.cnblogs.com/qiweiwang/archive/2011/04/18/2019952.html

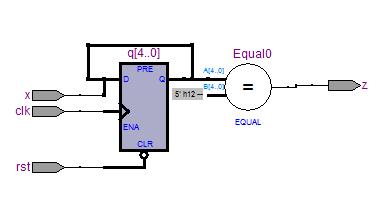

这篇博客,才发现原来使用移位寄存器可以如此简单,原理图如下:

基本思路就是利用移位寄存器作为检测窗口,每进来一个数就跟目标序列进行比较,简单粗暴。

下面贴一下原帖的代码:

module seqdet

(

input wire x,

input wire clk,

input wire rst,

output wire z,

output reg [4:0] q

);

//reg [4:0] q;

assign z = (q == 5'b10010) ? 1'b1:1'b0;

always @ (posedge clk,negedge rst)

if(!rst)

q <= 5'd0;

else

q <= {q[3:0],x};

endmodule

testbench:

`timescale 1ns/1ns

module seqdet_tb;

localparam T =20;

reg clk,rst;

reg [23:0] data;

wire z,x;

wire [4:0] q;

assign x = data[23];

initial

begin

clk =0;

rst =1;

#2 rst =0;

#30 rst =1;

data =20'b1100_1001_0000_1001_0100;

#(T*1000) $stop;

end

always #T clk = ~clk;

always @ (posedge clk)

#2 data = {data[22:0],data[23]};

seqdet U1

(

.x(x),

.z(z),

.clk(clk),

.q(q),

.rst(rst)

);

endmodule

由于移位寄存器的赋值是在always块中,故而相对实际延迟了一个clk.由上面的方针结果可知,输出z相对x晚了一个时钟周期,因为由于移位寄存器的赋值是在always块中,故而相对实际延迟了一个clk.

Note:

- 跟用状态机实现的区别在于,使用移位寄存器需要存储所有的码字,因此如果序列长度为N,则该方法需要消耗的寄存器就是N个。而使用状态机实现时,每个状态代表部分码字,如果使用十进制编码,则只需要使用log2(N)个寄存器即可编码所有状态,从寄存器资源的角度来看FSM实现起来代价较小。

- 此外,寄存器版本每来一个码元都要比较所有码字,因此需要消耗N个比较器,而FSM的的状态寄存器每一位在状态转移时都需要不同的译码逻辑,如果状态转移比较简单,组合逻辑可能会比移位寄存器少,状态转移复杂的化就不好说了。

- 当然,移位寄存器的版本编码更加简洁明了。

76

76

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?