名称:4路限时抢答器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

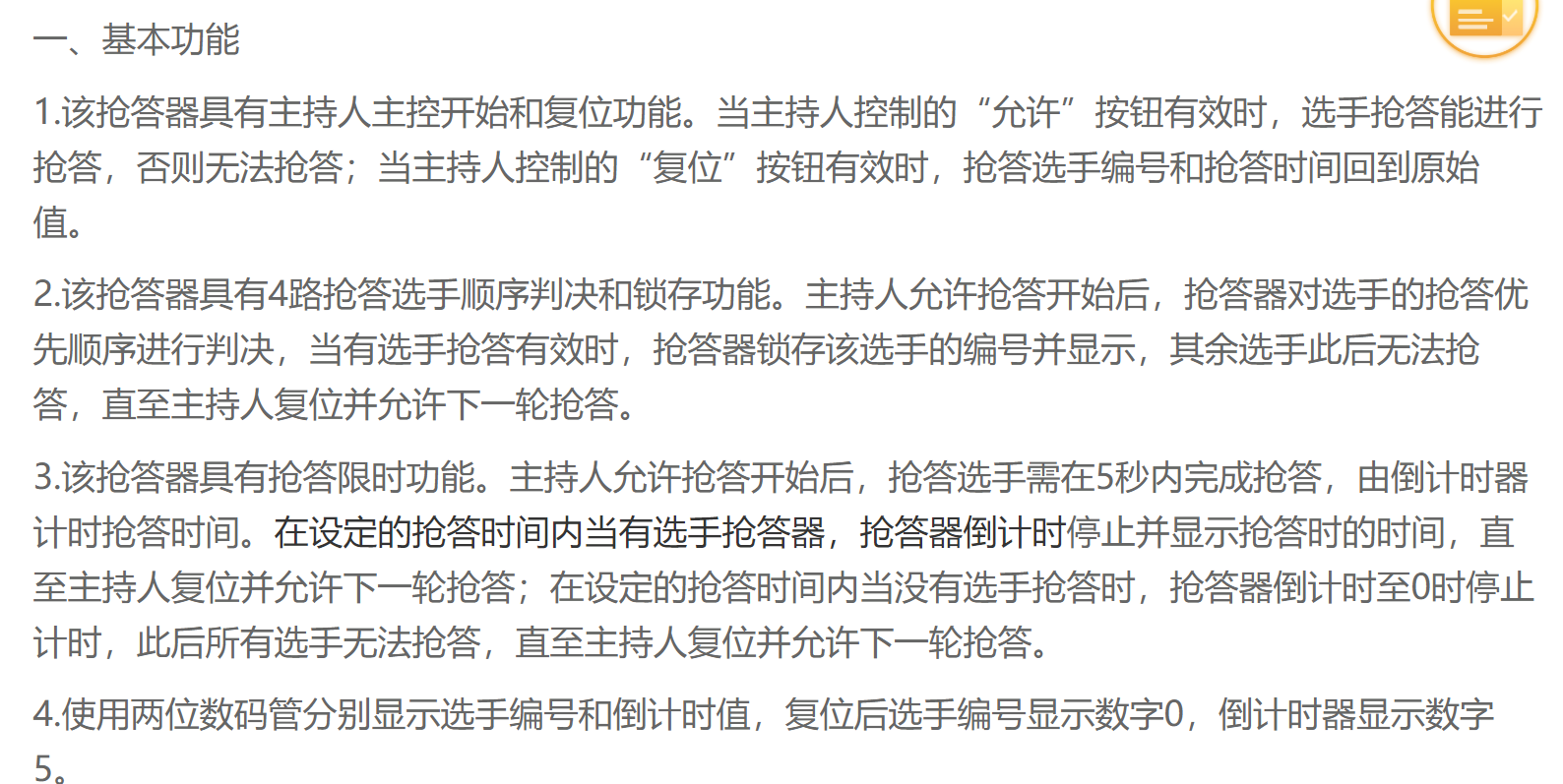

基本功能

1.该抢答器具有主持人主控开始和复位功能。当主持人控制的“允许″按钮有效时,选手抢答能进行抢答,否则无法抢答;当主持人控制的“复位”按钮有效时,抢答选手编号和抢答时间回到原始值

2该抢答器具有4路抢答选手顺序判决和锁存功能。主持人允许抢答开始后,抢答器对选手的抢答优先顺序进行判决,当有选手抢答有效时,抢答器锁存该选手的编号并显示,其余选手此后无法抢答,直至主持人复位并允许下一轮抢答。

3该抢答器具有抢答限时功能。主持人允许抢答开始后,抢答选手需在5秒内完成抢答,由倒计时器计时抢答时间。在设定的抢答时间内当有选手抢答器,抢答器倒计时停止并显示抢答时的时间,直至主持人复位并允许下一轮抢答;在设定的抢答时间内当没有选手抢答时,抢答器倒计时至0时停止计时,此后所有选手无法抢答,直至主持人复位并允许下一轮抢答。

4.使用两位数码管分别显示选手编号和倒计时值,复位后选手编号显示数字0,倒计时器显示数字

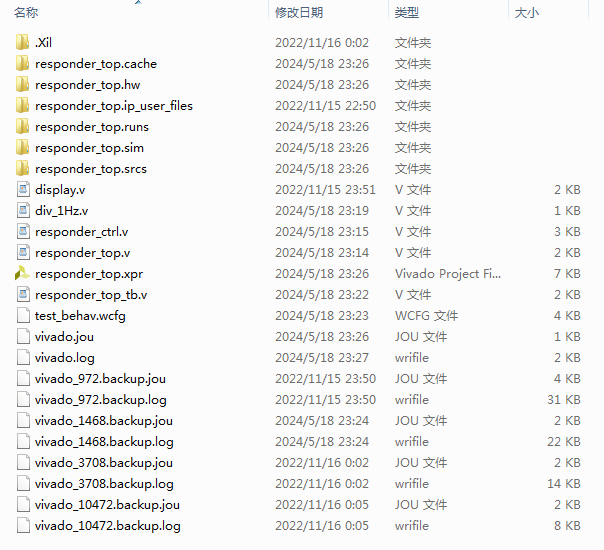

1、工程文件

2、程序文件

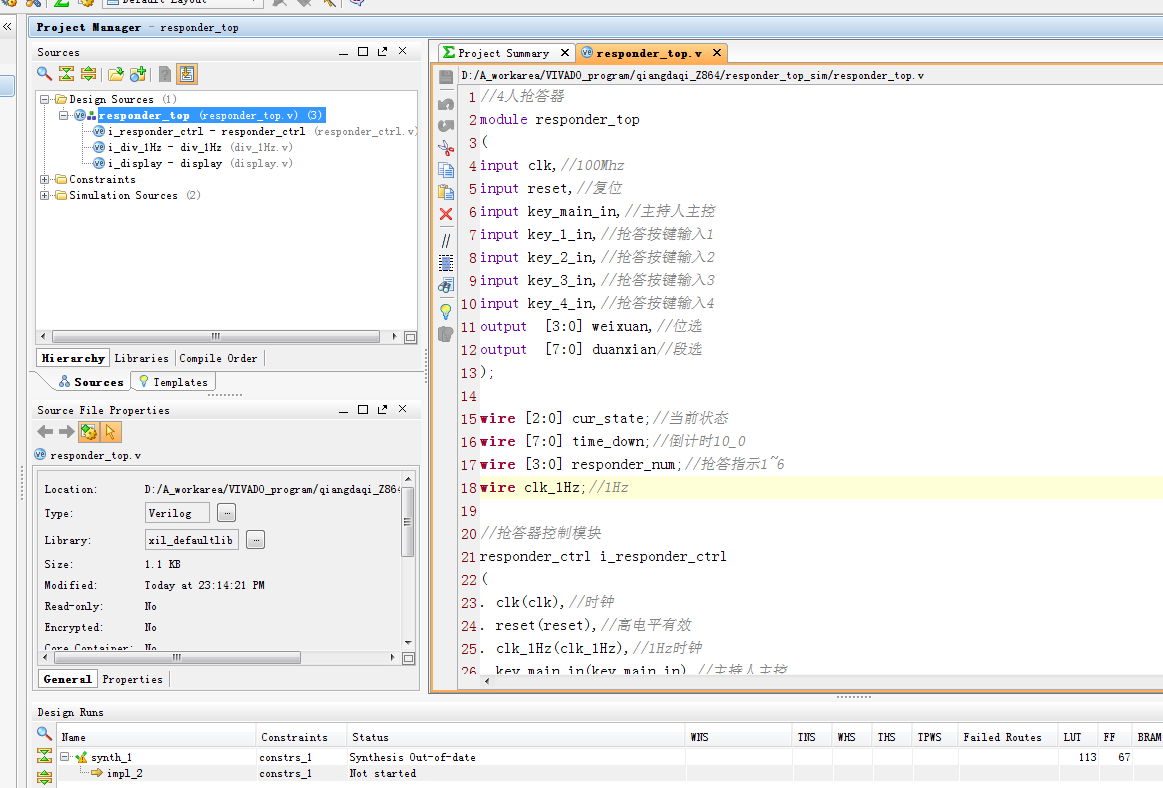

3、程序编译

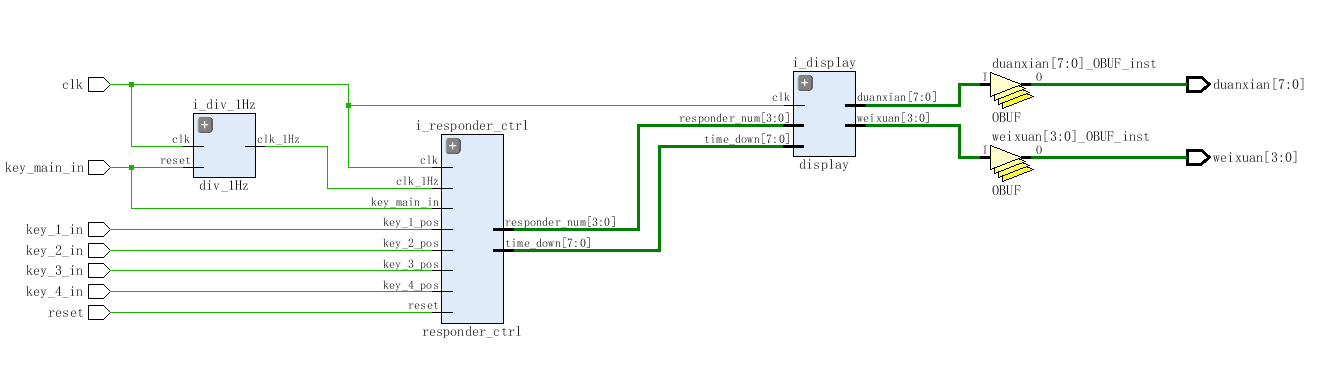

4、RTL图

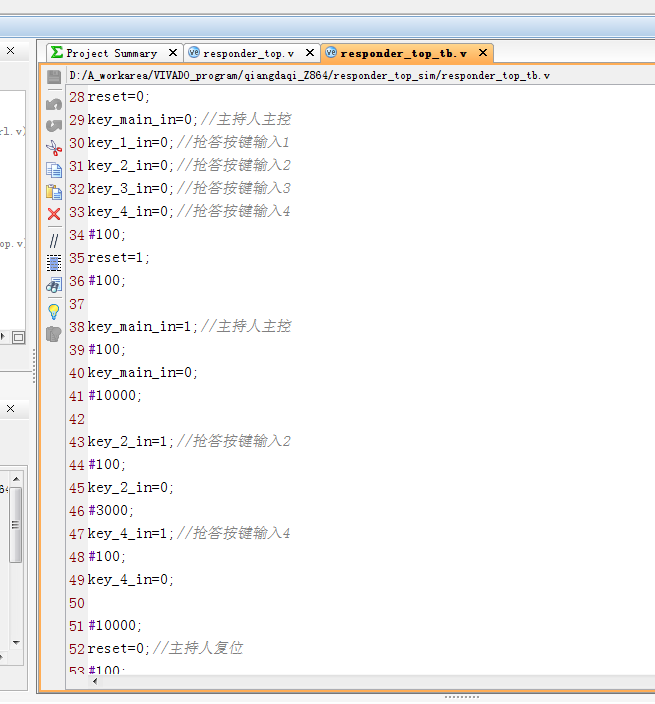

5、Testbench

6、仿真图

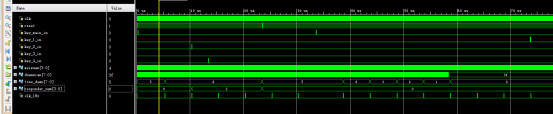

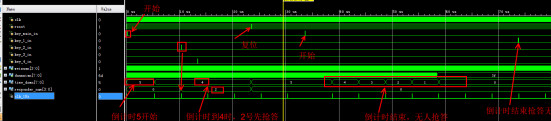

整体仿真图

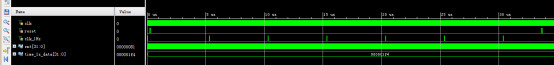

分频模块

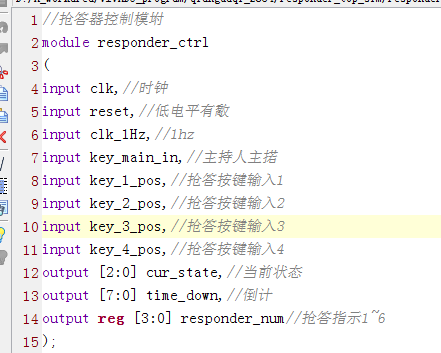

控制模块

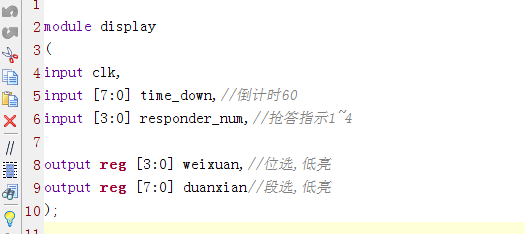

显示模块

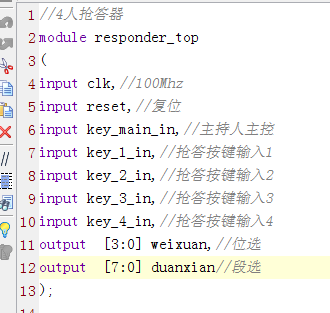

部分代码展示:

//抢答器控制模坿 module responder_ctrl ( input clk,//时钟 input reset,//低电平有敿 input clk_1Hz,//1hz input key_main_in,//主持人主掿 input key_1_pos,//抢答按键输入1 input key_2_pos,//抢答按键输入2 input key_3_pos,//抢答按键输入3 input key_4_pos,//抢答按键输入4 output [2:0] cur_state,//当前状态 output [7:0] time_down,//倒计 output reg [3:0] responder_num//抢答指示1~6 ); parameter s_idle=3'd0;//空闲状 parameter s_start=3'd1;// parameter s_timedowm=3'd2;//倒计 parameter s_qiangda=3'd3;//抢答 parameter s_end=3'd4;//抢答结束 reg [2:0] state=3'd0; reg time_over=0;//倒计时结束指示 assign cur_state=state; always@(posedge clk or negedge reset) if(~reset) state<=s_idle;//空闲 else case(state) s_idle: if(key_main_in)//主控,按键 state<=s_start;// else state<=s_idle;//空闲 s_start: state<=s_timedowm;//倒计时 s_timedowm: state<=s_qiangda;//倒计时 s_qiangda: if(key_1_pos | key_2_pos | key_3_pos | key_4_pos) state<=s_end;//结束 else if(time_over==1)//倒计时 state<=s_end;//倒计时结束 else state<=s_qiangda;//抢答 s_end: if(key_main_in)//主控 state<=s_start;// else state<=s_end;//结束 default:state<=s_idle;//空闲 endcase //always@(posedge clk or negedge reset) //if(~reset) //beep<=0;//复位 //else if(state==s_beep) //beep<=1;//输出报警信号 //else //beep<=0; reg [7:0] down_cnt=8'd5;//倒计时计敿 always@(posedge clk) if(state==s_timedowm || state==s_qiangda)begin if(down_cnt==8'd0)begin down_cnt<=8'd0; time_over<=1;//倒计时 end

源代码

点击下方的公众号卡片获取

3359

3359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?