参考来源:JESD209-4B,JESD209-4E

LPDDR Initial → LPDDR Write Leveling and DQ Training → LPDDR Read and Training → LPDDR Write and Training → LPDDR Clock Switch → PIM Technical

Write Leveling

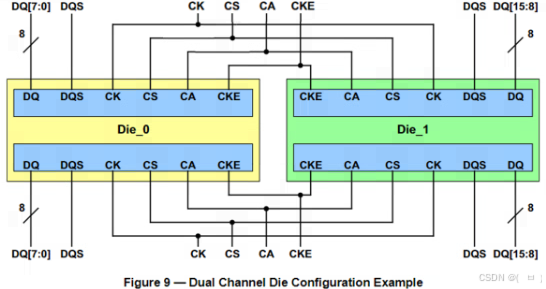

先看下JESD209-4E中Figure 9对LPDDR4下信号线拓扑结构的描述,理解为什么需要Write Leveling。

可以看到不同DRAM的DQ/DQS信号都是分开独立的,所以不同DRAM之间不会存在太大DQ/DQS信号延时差异。

但是Address/Command/CLK信号在Fly By结构下传输到不同DRAM过程中势必存在不同的延时。

所以通过Write Leveling调整不同DRAM上DQS-Data Strobe输入信号相对于CLK信号的延时,从而能够在不同DRAM CLK Delay下采样到正确的DQ Data。

DQS信号由MC控制器驱动,DRAM在DQS边沿采样CLK信号。

DRAM通过提供有关DQ上捕获的CLK电平的反馈来响应MC控制器。

通过DRAM反馈确定DQS相对于CLK是超前还是滞后,从而调整Delay的增加或者减少。

以下是每个DRAM上Write Leveling详细过程:

- 配置MR2寄存器进入Write Leveling Mode

- 当DRAM检测到稳定的DQS信号,就对当前CLK采样,再把CLK Value通过DQ Bus返回MC <

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1465

1465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?