Quartus-II 、Modelsim 安装

选则安装文件夹

一直点ok就安装完成了

设计一个D触发器,进行仿真,时序波形验证

D触发器简介

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

D触发器结构

D触发器由4个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。边沿D触发器可由两个D触发器串联而成,但第一个D触发器的CP需要用非门反向。

创建原理图

创建工程

选择工程路径

next

添加元器件:nand2,二个输入的与非门,添加四个and2和一个非门not

连线

编译原理图文件

硬件电路图如下

设置Node 和 Bus

效果如下

输入Clk,时钟信号如下

时序波形仿真

仿真如下

Quartus-II调用D触发器及时序仿真

创建触发器

测试代码如下

`timescale 1ns / 1ns

module no3_tb;

reg clk,d;

wire q;

no3 u1(.d(d),.clk(clk),.q(q));

initial

begin

clk = 1;

d <= 0;

forever

begin

#60 d <= 1;

#22 d <= 0;

#2 d <= 1;

#2 d <= 0;

#16 d <= 0;

end

end

always #20 clk <= ~clk;//半周期为20ns,全周期为40ns的一个信号

endmodule

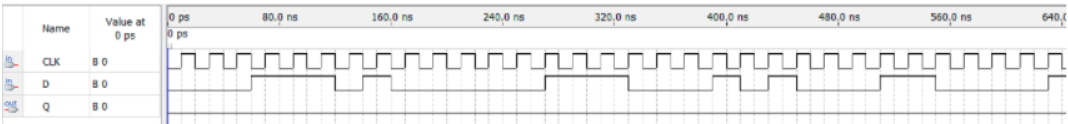

原始波形图如下

功能仿真图如下

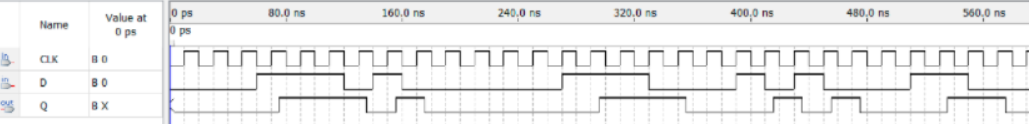

时序仿真图如下

732

732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?