七、设计约束原理

设计约束文件直接影响设计性能和设计效率。xilinx的ISE软件提供了实现不同类型约束的方法:

1、用户约束文件(User Constraints File,UCF)是一个ASCII文件,该文件指明了用于逻辑设计的约束。设计者可以使用文本编

辑器或约束编辑器来创建UCF文件。这些约

束影响逻辑设计在目标器件的实现方式。设计者可以使用UCF文件来覆盖在设计

入口所声明的约束。UCF文件是NGDBuild的输入。UCF文件将成为生成后的NGD文件的

一部分,对于FPGA芯片来说,当

设计被映射时,将使用这些约束中的一部分,并将其中的一部分约束写入到MAP所生成的物理约束(Physical Constraints

File,PCF)

文件中。PCF文件被物理设计工具使用(比如PAR和时序分析工具),在设计映射后,将运行物理设计工具。

在下面的文件中可以找到逻辑约束条件:

(1)网表约束文件(Netlist Constraints File,NCF)是由综合工具生成的ASCII文件。

(2)UCF文件使由用户生成的ASCII文件。

NCF文件和UCF文件的通用规则包括:

(1)UCF和NCF文件使大小写敏感的。

(2)每一个描述使用个“;”结束。

(3)当描述超过一行时,不需要使用连接符进行连接(由于分号“;”表示结束)。

(4)xilinx推荐设计者将相似的块和元件构成一个组进行一个时序约束,而不需要分别进行约束。

(5)UCF和NCF文件的注释使用“#”符号开头。

#file TEST.UCF

#net constraints for TEST design

NET"$SIG_0 MAXDELAY" = 10;

NET"$SIG_1 MAXDELAY" = 12 ns;

(6)在UCF和NCF文件中,描述不需要规则先后顺序。

(7)将NET和INST名字用双引号括住表示。

(8)设计人员可以对一个给定的实例进行多个约束。

INST myInst LOC = P53 | IOSTANDARD = LVPECL33 | SLEW = FAST ;

如果出现约束冲突时,UCF覆盖NCF和原理图/网表的约束。NCF覆盖原理图/网表约束。

PCF文件使一个ASCII文件,其中包含两部分:

(1)由映射工具产生的物理约束。

(2)由用户输入的物理约束。

2、时序约束原理

xilinx软件允许设计者为设计指定精确的时序要求。使用全局或者路径指定的约束,来指定这些要求。用于指定时序约束的

基本方法是在用户约束文件中输入这些约束,此外,能在源文件(HDL和原理图)中输入约束。一旦设计者定义了时序规范和

映射了设计,PAR基于这些要求布局和布线设计。使用命令行工具TRACE或者时序分析器来分析指定时序要求的结果。

当一个网络有多处时序约束时,XST以下面的顺序来处理时序约束。

a、信号上指定的约束。

b、顶层模块指定的约束。

c、顶层模块的全局约束。

时序约束会对设计产生影响,所以要谨慎的使用时序约束的条件。

在XST约束文件中,支持下面8中时序约束类型。

1)FROM-TO:定义了两个群组之间的时序约束。一个组可以使用户定义或者是预定义的(FFS,PADS,RAMS)。下面给

该约束的文字描述:

TIMESPEC "TSname" = FROM "group1" TO "group2" value ;

FROM-TO支持下面的预定义组:

(1)CPUS:PPC405处理器。

(2)DSPS:DPS45。

(3)FFS:所有的CLB和IOB沿触发的触发器、LUT移位寄存器、DDR寄存器。

(4)HSIOS:GT和GT10。

(5)LATCHES:所有CLB和IOB电平敏感的触发器。

(6)MULTIS:所有的同步/异步乘法器。

(7)PADS:所有I/O引脚。

(8)RAMS:所有CLB LUT RAM。

(9)BRAMS_PORTA,BRAMS_PORTB:所有双端口BRAM的端口A或B。

TIMESPEC "TS01" = FROM FFS TO FFS 30;

TIMESPEC "TS02" = FROM LATCHES TO LATCHES 25;

TIMESPEC "TS03" = FROM PADS TO RAMS 70;

TIMESPEC "TS04" = FROM FFS TO PADS 55;

TIMESPEC "TS05" = FROM BRAMS_PORTA TO BRAMS_PORTB(gork *);

2)OFFSET:它指定了一个外部时钟和相关的输入/输出数据引脚之间的时序关系。OFFSET只用于和引脚相关的信号,

不能用来对设计的内部信号进行扩展到达时间说明(即使用OFFSET约束)。该约束可以使设计者:计算来自外部网络

时钟和数据触发器的建立时间是否冲突;并且指明了来自一个内部触发器(该触发器由芯片外部的时钟引脚驱动)的Q

输出的外部输出网络的延迟。

OFFSET = {IN|OUT}"offset_time"[units]{BEFORE|AFTER}"clk_name"[TIMEGRP"group_name"];

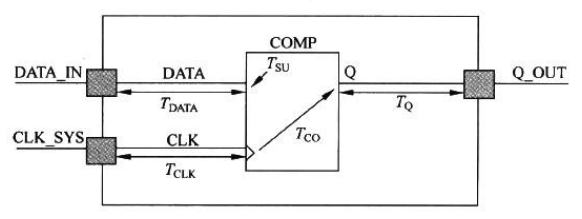

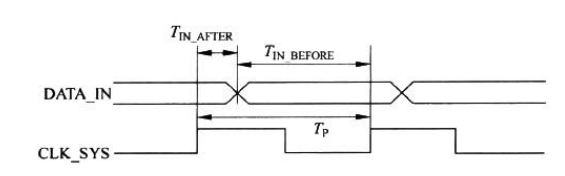

如图所示:通过一个例子来说明该约束条件:

(1)OFFSET IN BEFORE:该约束定义了对数据从引脚传输到同步元件的可用时间。这个时间就是在下个时钟沿到

达芯片前,数据与这个沿的时间差。

从该例子中可以看出时序有如下关系:

Tdata + Tsu - Tclk ≤ Tin_before

其中:Tsu为内在的触发器建立时间;Tclk为到触发器的总的时钟路径延迟;Tdata为从触发器的总的数据

路径延迟;Tin_before为整个建立要求。

当Tin_before = 20ns,可以作如下定义:

NET "DATA_IN" OFFSET = IN 20.0 BEFORE "CLK_SYS" ;

(2)OFFSET IN AFTER:OFFSET减去时钟的周期PERIOD确定了数据从引脚和在元件上建立可用的时间。

根据前面的图很容易得到这个时序关系:

Tdata + Tsu - Tclk ≤ Tp - Tin_after

其中:Tsu为内在的触发器的建立时间;Tclk为到触发器的总的时钟路径延迟;Tdata为从触发器的总的路

径延迟;Tp为单个周期要求;Tin_after为整个建立要求;

当Tin_after = 30ns,可以作如下定义:

NET "DATA_IN" OFFSET = IN 30.0 AFTER "CLK_SYS" ;

(3)OFFSET OUT AFTER:该约束定义对数据从同步元件到引脚可用的时间。这个时间可以看成是当前时候沿到达

芯片后数据离开芯片的时间差。

根据上图所示,很容易得到下面的时序关系:

Tq + Tco + Tclk ≤ Tout_after

其中:Tco为内在的触发器时钟到输出的时间;Tclk为到触发器的总的时钟路径延迟;Tq为从触发器的总的

数据路径延迟;Tin_after为整个时钟到输出的要求;

当Tout_after = 35ns时,可以作如下定义:

NET "Q_OUT" OFFSET = OUT 35.0 AFTER "CLK_SYS";

(4)OFFSET OUT BEFORE:该约束定义了达到FPGA的外部数据的时间。OFFSET从时钟周期PERIOD减去这个时

间确定了对从同步元件到引脚数据可用的时间。

根据前面所示,很容易得到下面的时序关系:

Tq + Tco + Tclk ≤ Tp - Tout_before

其中:Tco为内在的触发器时钟到输出的时间;Tclk为到触发器的总的时钟路径延迟;Tq为从触发器的总的

数据路径延迟;Tp为单个周期要求;Tin_before为整个时钟到输出的要求;

当Tout_before = 15ns时,可以作如下定义:

NET "Q_OUT" OFFSET = OUT 15.0 BEFORE "CLK_SYS";

3)TIG:TIG约束引起贯穿指定网络的路径被时序分析和优化忽略。该约束能用于所影响信号的名字。

Net "netname" TIG ;

TIMESPEC "TSidentifier" = FROM "source_group" TO "dest_group" TIG ;

4)TIMEGRP:是一个基本的组约束。除组命名使用TNM标识符外,设计中可以从其他组来定义自己的组。通过定义

TIMEGRP约束,设计者可以定义与已存在组的关联的

组。

TIMEGRP "netgroup" = "existing_grp1" "existing_grp2" ["existing_grp3"...];

TIMEGRP "big_group" = "small_group" "medium_group";

5)TNM:是一个基本的组约束。使用TNM来识别组成组的元素,这些元素FFS、RAMs、LATCHES、PADS、

BRAMS_PORTA、BRAMS_PORTB、CPUS,HSIOS和MULTS。

{NET|INST|PIN} "net_or_pin_inst_name" TNM = [predefined_group] identifier;

6)TNM Net:除了输入引脚网络外,和TNM是一样的。XST为时序分析的时序模型考虑了逻辑延迟和网络延迟。这些延迟

的大小取决于芯片的速度等级。这些延迟也取决于所选择的技术(比如Virtex和Virtex-E芯片)。逻辑

延迟数据和

Trace(布局布线后的时序分析程序)报告一致。网络延迟模型是基于负载而评估出来的。

7)Timing THRU Point:(TPTHRU)定义了在路径上的中间点。

INST "instace_name" TPTHRU = identifier;

NET "netname" TPTHRU = identifier ;

8)ASYNC_REG:该约束只能用于连接到寄存器和锁存器。只用于当寄存器或锁存器有异步输入的情况。

INST "instance_name" ASYNC_REG = {TRUE|FALSE};

3、引脚和面积约束原理

1)面积约束:AREA_GROUP是设计实现约束,将设计分配到物理区域用于映射、打包、布局和布线。面积约束与设计

中的逻辑块连接,约束的字符串的值表示了逻辑组块的名字。该约束将设计的逻辑块布局到指定的FPGA的面积区域中,

与面积约束相关的UCF描述为:

AREA_GROUP "groupname" RANGE = range;

AREA_GROUP "groupname" COMPRESSION = percent ;

AREA_GROUP "groupname" IMPLEMENT = {FORCE|AUTO};

AREA_GROUP "groupname" GROUP = {OPEN|CLOSED};

AREA_GROUP "groupname" PLACE = {OPEN|CLOSED};

AREA_GROUP "groupname" MODE = {RECONFIG};

下面对这些约束条件进行简单的说明:

(1)RANGE:定义了对放置包含在区域组内可用的芯片逻辑资源的范围。下面给出这些定义的文字描述:

RANGE = SLICE_X# Y# : SLICE_X# Y#

RANGE = RAMB16_X# Y# : RAMB16_X# Y#

RANGE = MULT18X18_X# Y# : MULT18X18_X# Y#

(2)COMPRESSION:为区域组定义了压缩因子。其范围0~100。如果没有RANGE,则只可选择0(无压缩)

1(最大压缩)。映射器从RANGE计算在AREA_GROUP内的CLB数量,并试图将其压缩到指定的百分比范

围。对于TBUF,BRAM,乘法器不能使用该约束条件。

(3)IMPLEMENT:使用FORCE和AUTO字符串选项。FORCE将迫使重新实现AREA_GROUP内的逻辑。AUTO确

定如果AREA_GROUP内的逻辑改变了,则重新实现逻辑。

(4)GROUP:控制逻辑打包(packing of logic)到物理元件(比如slice)。选择CLOSED时,不允许

AREA_GROUP组外的逻辑和AREA_GROUP内的逻辑结合;选择OPEN(默认设置)时,允许

AREA_GROUP组外的逻辑和AREA_GROUP组内的逻辑结合。

(5)PLACE:控制在RANGE内的资源分配情况。选择CLOSED时,不允许不是AREA_GROUP组内的元件放在

RANGE范围内;选择OPEN(默认设置)时,允许不是AREA_GROUP组内的元件放在RANGE范围内。

(6)MODE:用于定义可配置的区域组,比如:MODE = RECONFIG。

2)引脚约束:用来确定IO引脚的工作特性,其约束主要包括以下几个方面:

(1)位置约束:用来定义设计的I/O在器件上的位置。

NET "name" LOC = "A23" ;

(2)IO标准约束:用来定义I/O引脚的电气标准。

NET "name" IOSTANDARD = "LVTTL";

(3)IO驱动能力约束:用来定义输出引脚的驱动能力(以电流mA表示)。

INST "instance_name" DRIVE = {2|4|6|8|12|16|24};

(4)IO抖动率约束:用来定义输出引脚的抖动率。可选择的参数包括SLOW和FAST。

(5)IO延迟约束:用来定义输入路径的延迟元件。可选的参数包括NONE(关闭所有的IBUF和IFD路径延迟)、

BOTH(打开所有的IBUF和IFD路径延迟)、IBUF(设置关闭在I/O元件内的任何寄存器的延迟,同时如果输入

缓冲区驱动I/O元件外的一个寄存器的D引脚则打开元件外的寄存器延迟)、IFD(打开任何I/O元件外的寄存

器,同时如果寄存器占用了I/O元件的输入侧则关闭元件外的寄存器的延迟)(不考虑IOB=TRUE约束)。

INST "instance_name" IOBDELAY = {NONE|BOTH|IBUF|IFD};

(6)IO端接约束:是用于映射约束。可选择的参数:PULLDOWN(当I/O无驱动时,保证其为逻辑低,避免三

态)、PULLUP(当I/O无驱动时,保证其为逻辑高,避免三态)、KEEPER(包含输出引脚的值)。

NET "pad_net_name" {KEEPER|PULLUP|PULLDOWN};

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?