25_实战篇:时钟IP核MMCM(第一讲:时钟资源讲解)_哔哩哔哩_bilibili

25时钟IP核MMCM

7系列的时钟资源

bufferG

bufferR

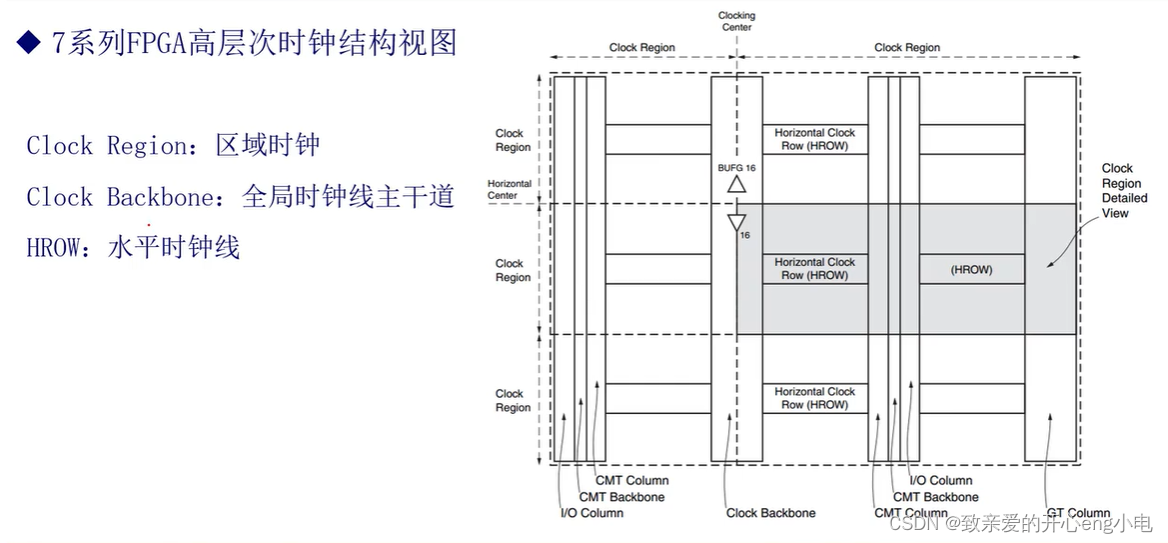

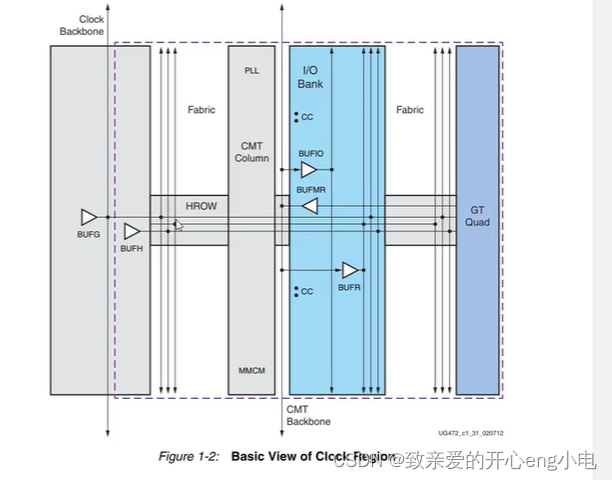

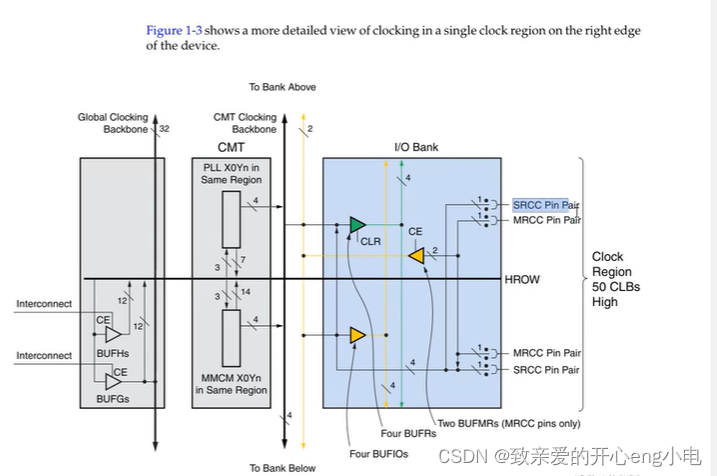

下图可视为一个FPGA(官方手册)

4

4

MRCC,SRCC

全局时钟:MRCC P

差分时钟:MRCC P,N

单时钟:接P

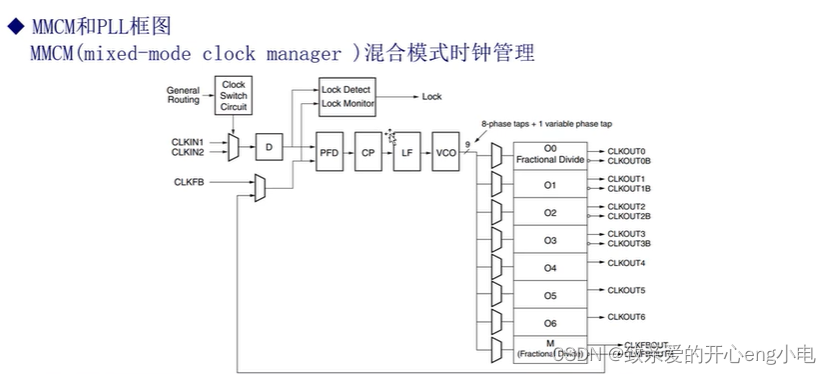

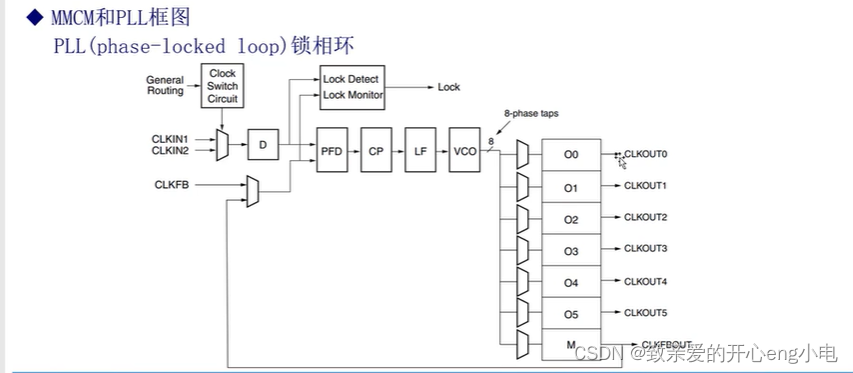

MMCM可以实现动态的调整,输出反向,PLL不行。除了这一点,两者完全相同

实战

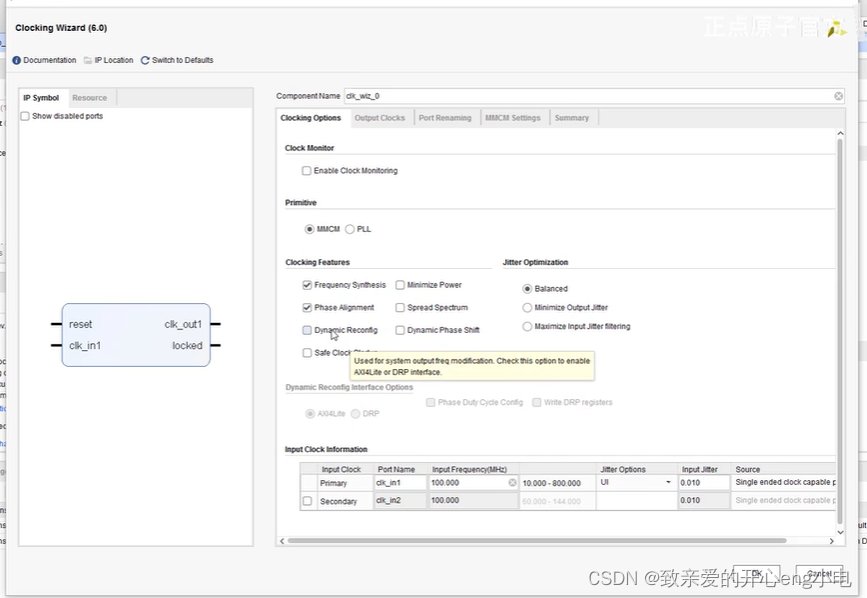

选项卡分析

frequency sythesis:输出不同频率的时钟

phase alignment:相位关系

dynamic recording:动态调整输出时钟频率

safe clock startup:只有在输出稳定的时候有时钟

minimize power:电源优化

dynamic phase shift:动态调整输出时钟相位

7154

7154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?