通过第一章可知,SSD主要由两大模块组成:主控和闪存介质。其中,主控的作用包括:

(1)实现标准主机接口与主机通信;

(2)实现与闪存的通信;

(1)运行SSD内部FTL算法。

主控芯片的好坏直接决定了SSD的性能、寿命、可靠性。

2.1 SSD系统架构

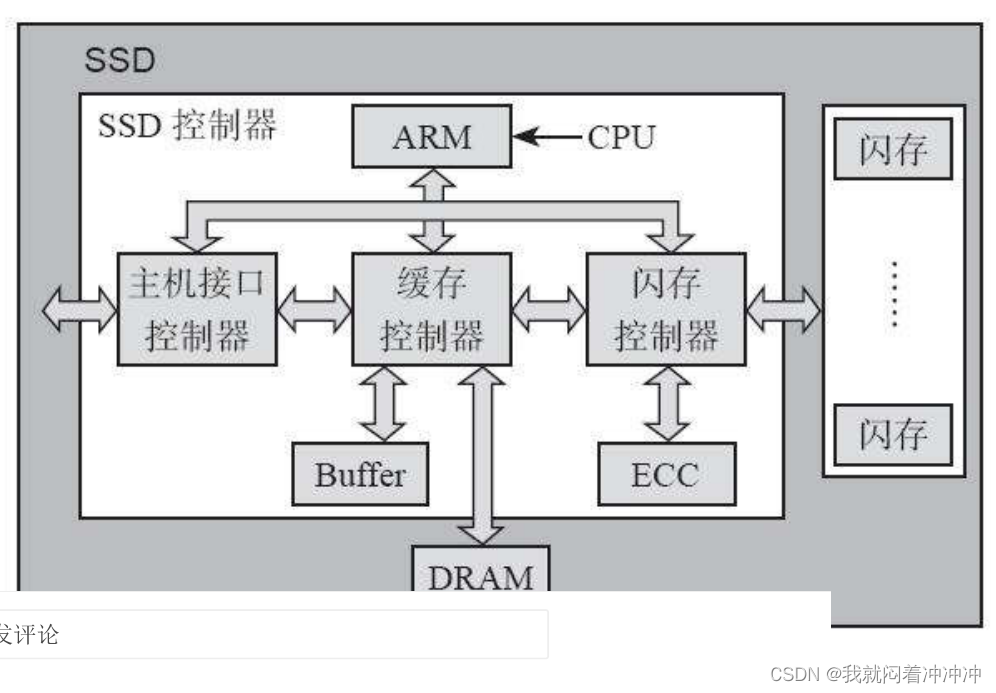

SSD作为数据存储设备,有主控CPU、RAM(随机存储器)、操作加速器、总线、数据编码译码等模块;操作对象为协议、数据命令、介质;操作目的是写入和读取用户数据。SSD的系统架构概略图如下所示:

图中,主控采用ARM CPU,主要分为前端和后端两个部分。其中,前端(主机接口控制器,Host Interface Controller)跟主机打交道,接口可以是SATA、PCIe、SAS等。后端(闪存控制器,Flash Controller)跟闪存打交道,并完成数据编解码和ECC(数据校验、纠错)。除此之外还有缓冲(Buffer)、DRAM(动态随机存取存储器)。

模块之间通过AXI高速和APB低速总线互联互通,完成信息和数据的通信。

2.1.1 前端

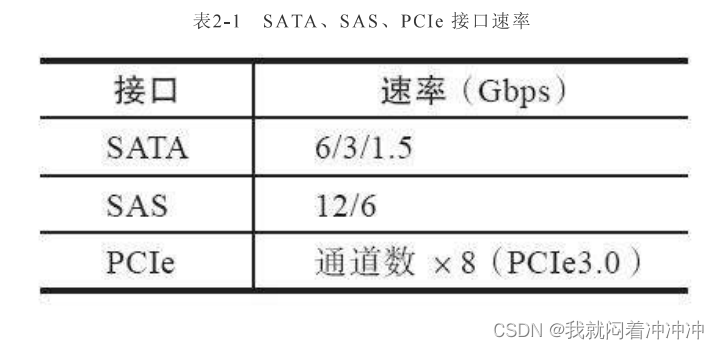

主机接口:与主机进行通信(数据交换)的标准协议接口,主要代表有SATA、SAS、PCIe等。

前端是负责主机和SSD设备通信的接口,命令和数据传输通过前端总线流向或流出SSD设备。

1. SATA

全称是Serial Advanced Technology Attachment(串行高级技术附件),是一种基于行业标准的串行硬件驱动器接口。

Serial(连续的,串联的)。

2. SAS

SAS(Serial Attached SCSI) 即串行连接SCSI(小型计算机系统接口),与SATA类似,都是采用串行技术以获得更高的传输速度,并通过缩短连接线改善内部空间。

SAS的接口技术可以向下兼容SATA。二者的兼容性主要体现在物理层和协议层。在物理层,SAS接口和SATA接口完全兼容,SATA硬盘(拥有SATA接口的固态硬盘)可以直接用在SAS的环境中。在协议层,SAS由三种类型的协议组成,在三种协议的配合下,SAS可以和SATA以及部分SCSI设备无缝结合。

3. PCIe

PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准。PCIe属于高速串行点对点多通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽(带宽,即吞吐量),主要支持主动电源管理、错误报告、端对端的可靠性传输、热插拨以及服务质量等功能。

从硬件模块上看,前端有PHY层(端口物理层),用于接收串行比特数据流,并将其转化成数字信号交给前端的后续模块处理。

例子:从协议角度,主机端发送一条SATA Write FPDMA命令到SSD设备的过程(前端所要进行的操作)

DMA:直接存储器存取。

(1)主机在总线上发出Write FPDMA命令FIS(Frame Information Structure,帧信息结构);

(2)SSD收到该命令,判断自身内部写缓存是否有空间接收新的数据。若有,则向主机发送DMA Setup FIS命令;若无,则什么都不发送,此时主机端处于等待状态(即流控--数据流量控制);

(3)主机收到DMA Setup FIS后,发送不大于8KB的Data FIS给SSD设备;

(4)重复(2)和(3),直到数据发送完毕;

(5)SSD发送一个状态Status FIS到主机,表示从协议层面这条写命令执行完毕。

SSD接收命令和数据并存放到SSD内部缓存区后,前端固件模块还需要对命令进行解析,并分配任务给中端FTL。

命令解析(Command Decoder)将命令FIS解析成固件和FTL可以理解的元素。

命令解析完成后,放入命令队列里等待终端FTL排队处理。

2.1.2 主控CPU

I-RAM:代码存储区。

D-RAM:数据存储区。

SoC:系统级芯片,也叫片上系统。

PLL:锁相环。

URAT:用于控制计算机和串行设备的芯片。

SSD控制器SoC模块一般有一颗或多颗CPU核组成,同时片上还有I-RAM、D-RAM、IO、PLL、URAT、高低速总线等外围电路模块。

固件运行在CPU核上。

若是多核CPU,那么软件可以是对称多处理(SMP)和非对称多处理(AMP)。其中,SMP的多核共享OS和同一份执行代码;AMP的多核分别执行不同代码。

2.1.3 后端

ECC:数据校验、纠错。

后端两大模块分为 ECC模块 和 闪存控制器 。

(1)ECC模块

ECC模块是数据编解码单元。执行写操作时,会给原数据加入ECC检验保护,是一个编码过程;执行读操作时,会通过解码来校验和纠错。

SSD内的ECC算法主要有BCH和LDPC。

(2)闪存控制器

它负责管理数据从缓存到闪存的读取和写入。

Die/LUN是闪存通信的最小基本管理单元。

2.6 全闪存阵列AFA

闪存阵列由若干个Die构成。

文章介绍了SSD的主要组成部分,包括主控和闪存介质,强调了主控在性能、寿命和可靠性上的关键作用。主控包括前端(主机接口如SATA、SAS、PCIe)和后端(闪存控制器及ECC)。ECC用于数据校验和纠错,确保数据的完整性。SSD的系统架构还涉及CPU、RAM、总线等模块,以及全闪存阵列AFA的概念。

文章介绍了SSD的主要组成部分,包括主控和闪存介质,强调了主控在性能、寿命和可靠性上的关键作用。主控包括前端(主机接口如SATA、SAS、PCIe)和后端(闪存控制器及ECC)。ECC用于数据校验和纠错,确保数据的完整性。SSD的系统架构还涉及CPU、RAM、总线等模块,以及全闪存阵列AFA的概念。

1261

1261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?