门控时钟参考:

https://blog.csdn.net/bleauchat/article/details/96502907

竞争与冒险:参考https://blog.csdn.net/bleauchat/article/details/85288345

触发器与锁存器参考:https://blog.csdn.net/bleauchat/article/details/89214405

https://blog.csdn.net/surgeddd/article/details/4683657

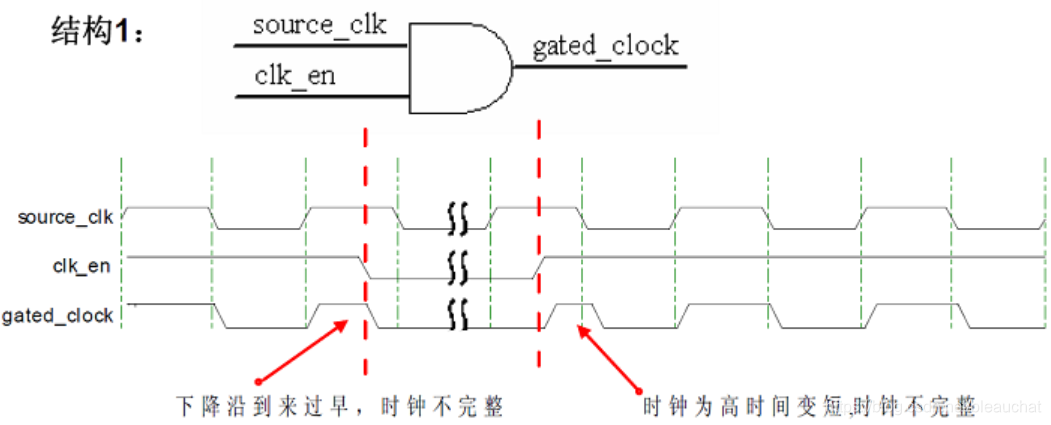

结构-1

这种系统时钟门控的机制算然简单,但是容易使门控后的时钟不完整,甚至产生毛刺

结构-2

这种门控方法避免了门控时钟的不完整性,也可以避免避免毛刺的产生,但门控后的时钟可能会产生亚稳态

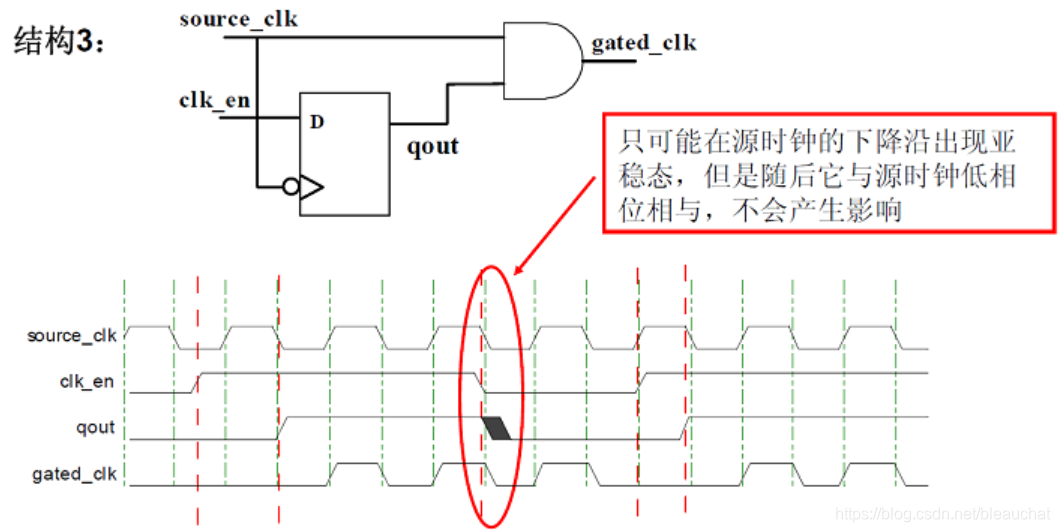

结构-3

这种结构解决了结构-2的亚稳态问题

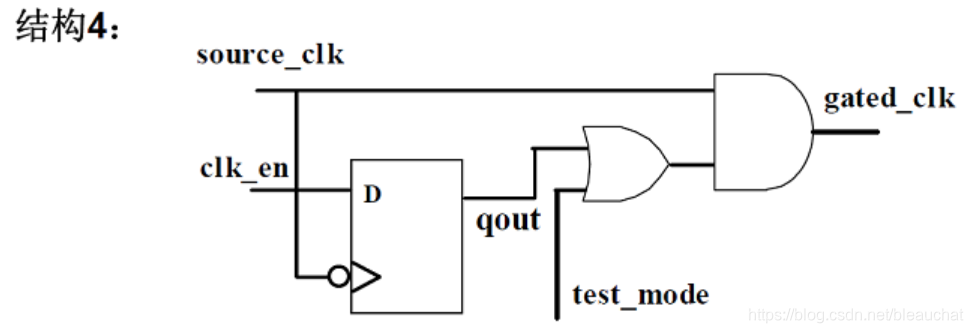

结构-4

这种带测试模式的结构可以在测试时让时钟一直开着

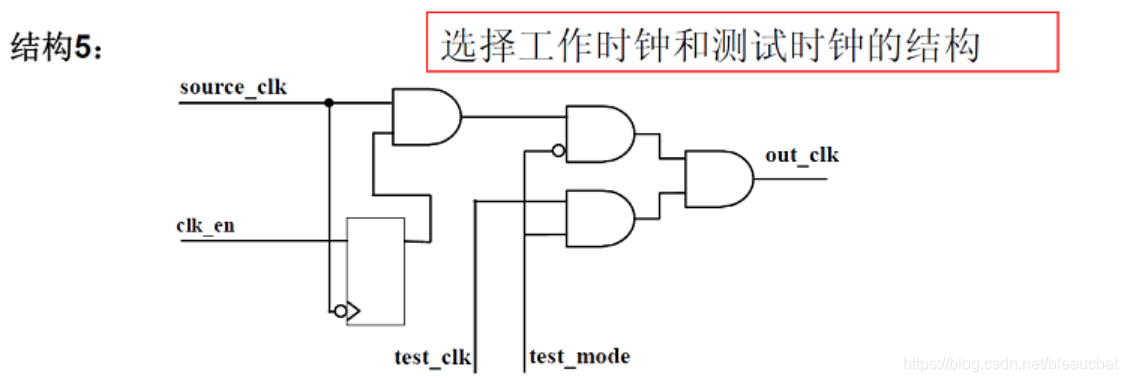

结构-5

在ASIC进行后端测试的时候,有时候可能会将不同时钟域的逻辑和寄存器连起来进行扫描链插入,此时可能某个模块的时钟来源可能不是通过它原来的时钟路径,而是整个芯片统一的测试时钟,就此时需要对时钟进行选择

双稳态电路

SR锁存器

D锁存器

触发器的电路结构和工作原理

触发器的逻辑功能

产生原因

竞争与冒险的定义

竞争:当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象;

冒险:两个输入端的信号取值的变化方向是相反时,如门电路输出端的逻辑表达式简化成两个互补信号相乘或者相加, 由竞争而可能产生输出干扰脉冲的现象;

有冒险一定存在竞争,有竞争不一定存在冒险!

更现实一点,对于一个与门:

解决方法

(1)修改逻辑设计:增加冗余项或消掉互补变量,将卡诺图中相切的两项用一个多余的圈连接起来

(2)加滤波电容

在电路输出端对地加小电容的方法,一般容量为4~20pF之间。利用电容的积分效应,足以把尖峰脉冲的幅度削弱到门电路的阈值以下。这种方法简单易行,缺点是导致了输出波形的边沿变坏,因此只适用于低速逻辑电路中。

(3) 引入选通脉冲

以上两种方法对FPGA来说并不适用,真正设计中常用的方法是选通法;其基本思路是通过选通脉冲对输出门加以控制,令选通脉冲在电路稳定后出现,则可使输出避开险象脉冲,送出稳定输出信号

(4)利用D触发器打一拍

对于D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且不满足数据的建立和保持时间,就不会对系统造成危害,因此可认为D触发器的D输入端对毛刺不敏感。根据这个特性,应当在系统中尽可能采用同步电路,因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害

8548

8548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?