5.3.1感性负载的共源极

1.感性负载的引入

首先,我们在5.2里研究的阻性负载的共源极有很多不足之处:①无法提供好的匹配;②输出节点的时间常数恶化了高频性能;③增益和供电电压之间的trade-off,因为供电电压会随着工艺进步而降低,这会让增益更低。(因为VRD会受限于VDD)

为了避免增益和供电电压之间的trade-off,我们将阻性负载换为感性负载(理想电感不消耗直流电压)

2.分析

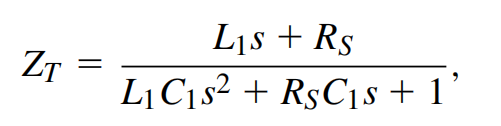

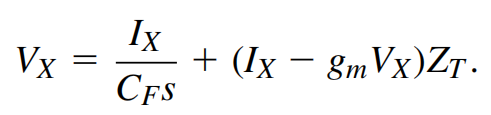

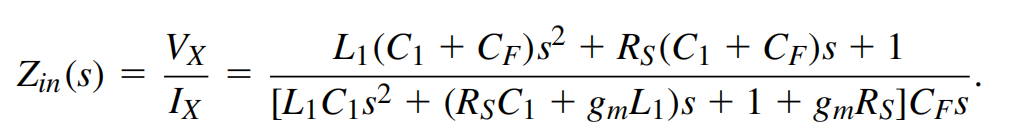

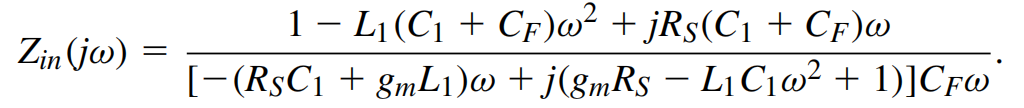

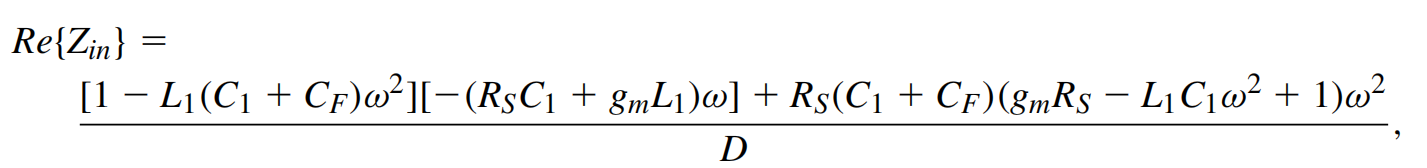

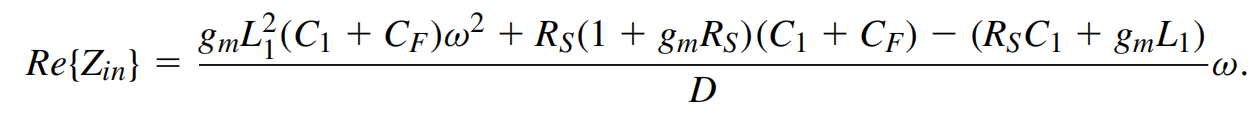

求Zin:

可以利用这个式子,在某些频率下使得输入阻抗为50Ω。但是在另一些频率下,输入阻抗可能会变成负的。一开始我是不认同这个说法的,因为观察上面这个式子,可以看到CF是使得RE(Zin)为正的。但是后来想想,要是CF为0,那输入阻抗是无穷大啊,哪来这么一堆(这一堆还确实有可能会为负值)

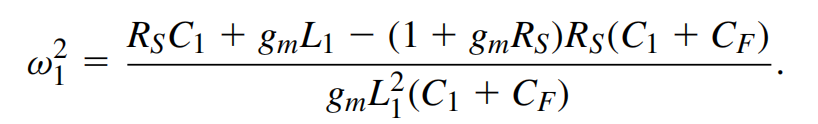

因为Zin的实部的分子,在w1时会变为0。这就意味着,当w跨越w1后,zin的实部的符号会改变。

3.改进

改进CF

可以在CF上并联一个电感,利用并联谐振。(这样谐振了不就相当于断了吗,zin就变成无穷大了啊,莫非目的只是不让zin变成负的?可以这样理解,LC并联谐振的极限是无穷大的阻抗,相当于没有引入反馈。所以L的引入是减小C的反馈,因为负阻抗是C的反馈带来的呀,减小了C的负反馈就可以减轻负阻抗现象。)

但是这个方法有缺点。因为CF很小,几个or几十个fF。谐振频率不能很高,所以L要很大才行。但是很大的L会在输入、输出、输入输出之间引入寄生电容,影响电路性能。

所以这种结构在RF设计中也几乎不用。

5.3.2阻性反馈的共源级

1.电路结构

首先看一下电路

2.输入电阻

先计算输入电阻

所以阻抗匹配要做到:

5.3.1感性负载的共源极1.感性负载的引入首先,我们在5.2里研究的阻性负载的共源极有很多不足之处:①无法提供好的匹配;②输出节点的时间常数恶化了高频性能;③增益和供电电压之间的trade-off,因为供电电压会随着工艺进步而降低,这会让增益更低。(因为VRD会受限于VDD)为了避免增益和供电电压之间的trade-off,我们将阻性负载换为感性负载(理想电感不消耗直流电压)2.分析求Zin:可以利用这个式子,在某些频率下使得输入阻抗为50Ω。但是在另一些频率下,输入阻抗可能会变

5.3.1感性负载的共源极1.感性负载的引入首先,我们在5.2里研究的阻性负载的共源极有很多不足之处:①无法提供好的匹配;②输出节点的时间常数恶化了高频性能;③增益和供电电压之间的trade-off,因为供电电压会随着工艺进步而降低,这会让增益更低。(因为VRD会受限于VDD)为了避免增益和供电电压之间的trade-off,我们将阻性负载换为感性负载(理想电感不消耗直流电压)2.分析求Zin:可以利用这个式子,在某些频率下使得输入阻抗为50Ω。但是在另一些频率下,输入阻抗可能会变

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1291

1291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?