本系列文章详细介绍了半导体后端工艺,涵盖了从不同类型的半导体封装、封装工艺及材料等各个方面。作为本系列的收篇之作,本文将介绍半导体的可靠性测试及标准。除了详细介绍如何评估和制定相关标准以外,还将介绍针对半导体封装预期寿命、半导体封装在不同外部环境中的可靠性,及机械可靠性等评估方法。

什么是产品可靠性?

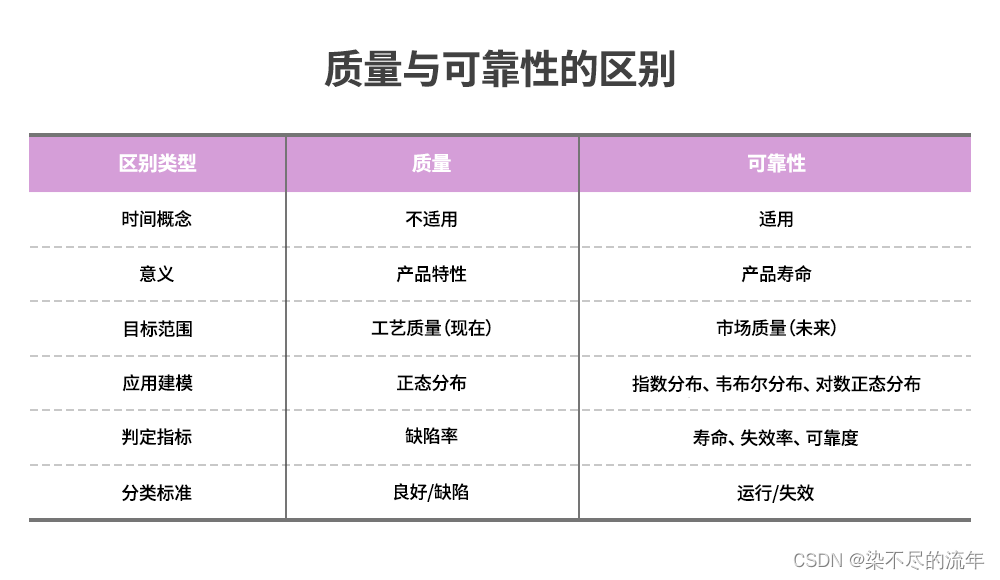

半导体产品的质量取决于其是否可以充分满足指定的标准及特性;而半导体产品的可靠性,是指在一定时间内无故障运行,从而提高客户满意度和复购率的能力。以此为前提,失效是指在产品使用过程中发生的故障,而缺陷是指在产品制造或检验过程中发生的错误。因此,产品缺陷属于质量问题,而产品在保修期内频繁出现故障则属于可靠性问题。

▲ 图1:质量与可靠性的区别(ⓒ HANOL出版社)

▲ 图1:质量与可靠性的区别(ⓒ HANOL出版社)

图1列举了质量及可靠性在含义和特性方面的区别。具体来讲,可靠性是指系统、零件或材料在特定的时间、距离或使用频次下,保持初始质量和性能的能力。要满足这一点,就必须要求产品在指定条件下,如规定使用方式或特定的环境因素中保持无故障运行状态。因此,半导体企业在产品量产前,必须先评估产品的质量和可靠性是否达到行业标准。此外,在产品量产期间,企业也应定期检查产品的质量和可靠性。

评估产品可靠性最为重要的一步,是事先明确可靠性评估标准。举例来说,如果一家企业准备出货100件产品,那么该企业则需要考虑以下问题:这些产品中有多少件在三年后依然可以正常使用?产品使用期间的运行模式?能否保证90%的产品在五年后仍可正常使用? 95%的产品可以正常使用多长时间?

验证这些标准需进行测试。理想情况下,产品需接受三年期、五年期甚至更长期限的测试,以确保其在不同时间范围内的可靠性。但如果将大量时间花费在产品评估上,会使产品量产时间大幅度推迟。因此,企业通常会采用加速测试和统计技术来评估可靠性,此外,还可以通过可靠性函数、产品寿命分布、及平均寿命等计算方式,在较短时间内完成可靠性验证。

国际半导体标准化组织(JEDEC)标准

半导体设计和制造企业可以自行评估旗下产品的可靠性,并将评估结果提供给客户,客户可根据评估结果来判定产品是否满足其需求,或自行开展可靠性评估测试。但如果半导体企业和客户采用的评估标准存在差异,那么双方就不得不对标准进行统一,而这是一项非常耗时的工作。作为解决方案,半导体企业通常会采纳“国际半导体标准化组织旗下固态技术协会1”(简称JEDEC)规定的标准,来同时满足企业及客户的需求。

1JEDEC旗下固态技术协会(JEDEC Solid State Technology Association):为微电子行业制定统一标准和出版物的领导机构。

JEDEC的主要职责是帮助制造商和相关组织,共同审查和制定如集成电路(Integrated Circuit)等电子设备的统一标准。随着其所制定的标准被广泛视为国际标准,JEDEC已成为实际意义上的全球半导体行业标准制定机构。

该组织董事会(Board of Directors, BoD)负责决定政策和程序,并拥有JEDEC标准的最终审批权。此外,JEDEC下设众多委员会(JEDEC Committee, JC),为各自擅长的专业领域制定标准。其中,部分重要的服务半导体行业的委员会及其职责为:JC-14固态产品质量与可靠性委员会,负责为固态产品制定相关标准;JC-11机械标准化委员会,负责制定模块及半导体封装外观标准;JC-42固态存储器委员会,负责制定DRAM标准;JC-63多芯片封装委员会,负责制定移动多芯片封装标准。

如果某企业想要为旗下产品制定标准,首先可以提交标准提案,由相应的委员会成员进行投票表决。无论规模大小,每家企业均有一票投票权。委员会投票通过后,标准提案还需经由董事会投票再次表决,两轮投票通过后,提案将被确立为JEDEC标准,并向各行业公示。

评估产品寿命的可靠性测试

除国际评估标准外,还有许多用于评估产品可靠性的指标,包括评估半导体产品寿命的指标。

早期失效率

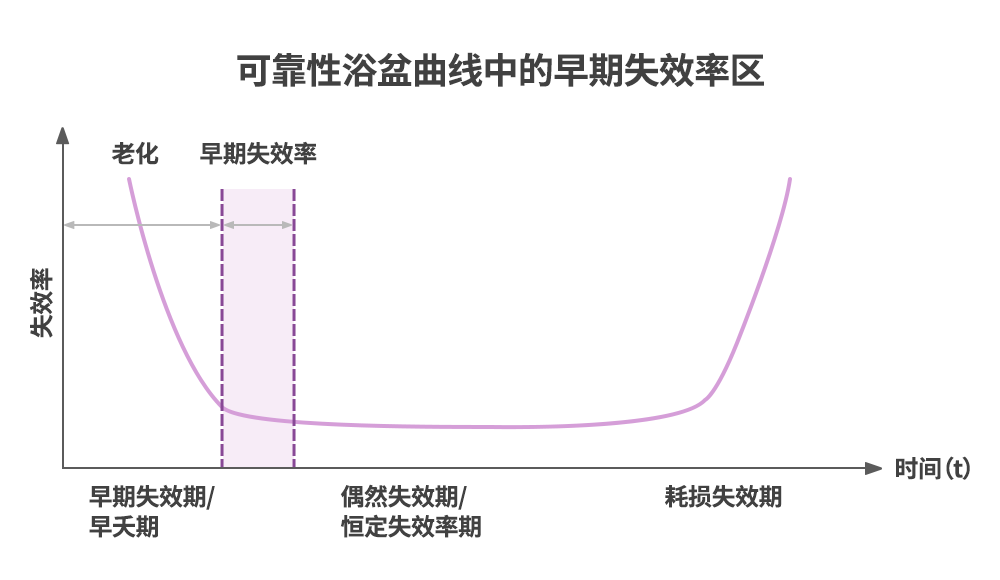

早期失效率(Early Failure Rate, EFR)用于估算产品在用户使用环境下,一年内发生的设备故障次数。对于某些产品而言,由于系统寿命不同,或要求更高标准的产品可靠性,这一期限可短至六个月或延长至一年以上。如图2所示,老化测试(Burn-in)2用于筛查可能在短期内失效的产品,而早期失效率用于验证筛查后产品的潜在失效率是否保持在可接受的水平。测试条件根据相关半导体产品的温度及电压加速因子进行设定和评估。

2老化测试(Burn-in):是指对产品施加电压和温度应力,以便在早期阶段消除产品潜在缺陷的测试。封装后执行的老化测试被称为“老化中测试(TBDI)”。

▲ 图2:浴盆曲线中的早期失效率(EFR)区,及产品失效率随时间发生变化的三个阶段(ⓒ HANOL出版社)

高低温工作寿命测试

高温工作寿命(High Temperature Operating Life Test, HTOL)测试是最常见的产品寿命评估类型之一,旨在评估产品在使用期间由温度和电压应力引起的问题。高温工作寿命测试是相对全面的测试方式,它不仅可以评估早期失效,同时可以识别由事故或损耗造成的失效问题。同样,低温工作寿命(Low Temperature Operating Life Test, LTOL)测试可用于评估因受到热载流子(Hot Carrier)3影响而发生失效的概率,但由于施加了电压和温度,也存在导致产品失效的其它情况发生。

3热载流子(Hot Carrier):晶体管尺寸缩小并导致通道变短后,电场会被增强。热载流子是在此现象发生后,所产生的极度活跃的移动电子。一般来说,这种短通道效应发生在半导体晶体管中。

高温存储寿命测试

高温存储寿命(High Temperature Storage Life, HTSL)测试用于评估产品在高温储存条件下的可靠性。受扩散、氧化、金属间化合物形成、及封装材料化学降解等因素影响,高温储存条件可能会对产品寿命产生影响。

耐久性和数据保留性能测试

耐久性测试用于评估NAND闪存等产品可以承受的编程/擦除(Program/Erase, P/E)周期的次数。对于NAND产品而言,一个关键的可靠性评估指标是数据保留能力。该指标衡量的是,在无电源供应情况下的一定时间内,数据在存储单元中可保留的时长。

各种外部环境条件下的可靠性测试

导致半导体产品失效的外部环境条件诱因有许多。因此,产品在被运往目的地之前,需接受特定环境条件下的可靠性测试,以确保其能够经受住不同环境条件的考验。

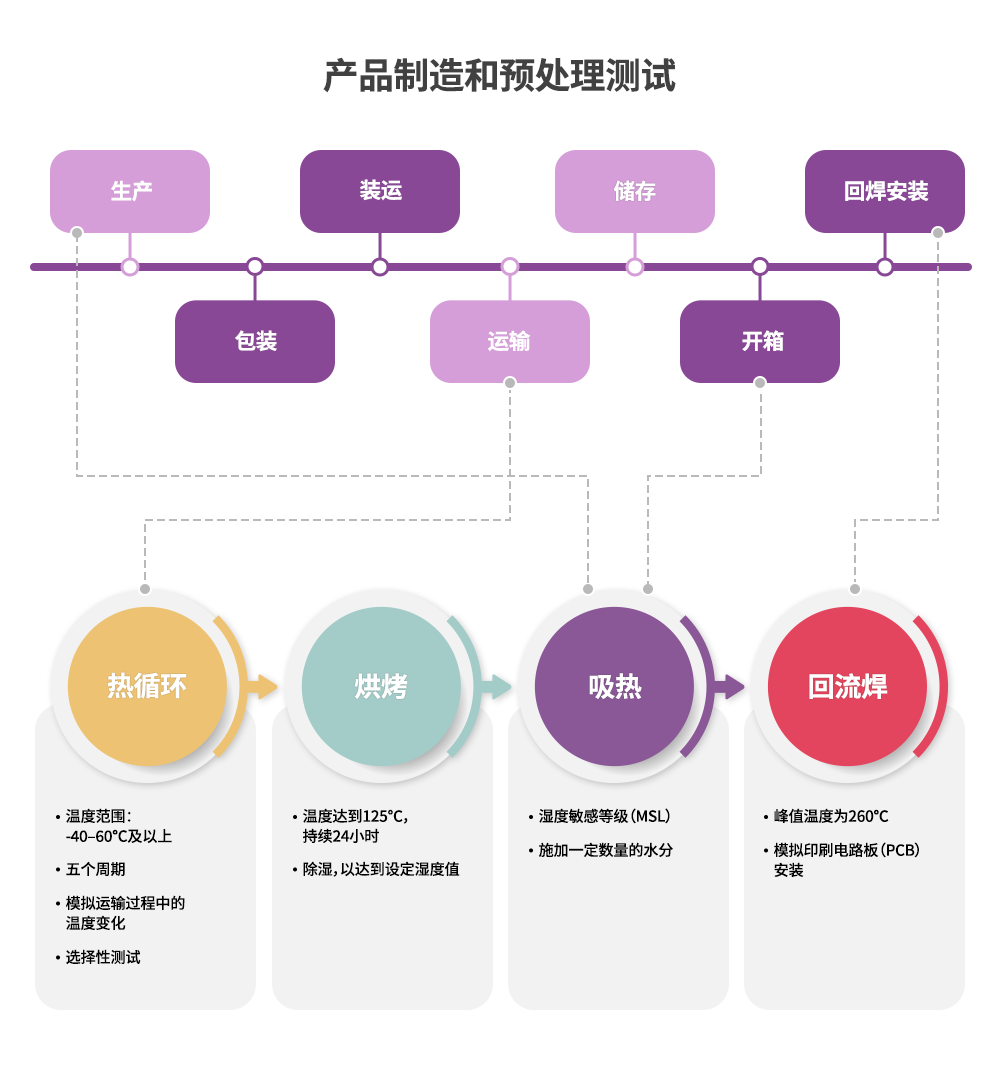

预处理测试

完成产品装运和储存后,可通过预处理测试来评估客户使用过程中可能出现的问题,如吸湿性(Hygroscopic)4和热应力等影响产品可靠性的因素。预处理通过模拟产品在出售、运送给客户的过程中、打开真空包装,及系统安装等各个环节的状态,评估其在潮湿条件下的可靠性。预处理是环境条件可靠性测试的先决条件,包括温湿度偏压(Temperature Humidity Bias, THB)测试、高加速应力(Highly Accelerated Stress Test, HAST)测试及热循环(Thermal Cycle, TC)测试。

4吸湿性(Hygroscopic):从空气中吸收水分的现象。在半导体行业内,此现象会导致半导体器件失效。

评估顺序依次为热循环、烘烤、吸热、回流焊。图3展示了将预处理测试应用于封装、运输和系统安装环节等的流程。

▲ 图3: 生产、运输和使用与预处理测试条件的关系(ⓒ HANOL出版社)

热循环测试

热循环(TC)测试是评估产品在不同的用户环境中,可能出现的瞬时温度变化时产品的耐受性。半导体封装和模块由不同材料组成,而不同材料的热膨胀系数(Coefficient of Thermal Expansion, CTE)5各不相同,这会导致由于应力作用而引起的疲劳失效,这种应力一般是在热变化发生后,因膨胀和收缩所产生的。

5热膨胀系数(Coefficient of Thermal Expansion):一种材料性能,用于表示材料在受热情况下膨胀的程度。

热循环测试的主要目的是测量温度变化时,半导体封装承受应力的能力,但高温和低温应力也可能导致许多其它失效问题。长时间的热冲击可用于验证半导体各种封装材料因应力和热膨胀因素,造成的界面分层(Interfacial Delamination)6、内外封装裂纹、芯片裂纹的可能性。此外,由于绿色产品法规对铅等有害物质使用的限制,以及便携式移动设备等应用领域的扩展,焊点的重要性与日俱增,而热循环也是评估焊点可靠性的一种有效测试方法。

6界面分层(Interfacial Delamination):指半导体封装中,界面相互分离。

温湿度贮存测试和温湿度偏压测试

温湿度贮存(Temperature Humidity Storage, THS)测试用于评估半导体产品承受高温和高湿条件下的耐受性。为了确定合适的曝露时间,建议通过测量打开防潮包装后的吸湿量以模拟实际的使用环境。同时,温湿度偏压(THB)测试通过向产品施加电偏压(Electrical Bias)7的方法来评估其防潮性能。尽管大多数失效原因是由铝腐蚀引起的,但温度应力也会造成其它潜在问题。 该测试还可以用于检测其它封装可靠性问题,例如湿气渗入引线间细小空隙或模塑孔而引发的焊盘金属腐蚀问题,以及湿气透过保护膜空隙渗入而导致的失效问题等。

7电偏压(Electrical Bias):在两点之间施加直流电(DC)以控制电路。

高压炉测试

高压炉测试(Pressure Cooker Test, PCT)是一种早期评估耐湿性的理想方式,其测试标准相较于温湿度贮存测试和温湿度偏压测试更为严格。高压炉测试又名蒸压器(Autoclave)8测试,该测试是在100%相对湿度和高压的情况下,通过湿气渗透来评估模塑材料的耐湿性以及模塑结构的可靠性。此外,该测试还可以用于检测由引线及模塑通孔间湿气渗透所导致的产品失效。

8蒸压器(Autoclave):一种高压器具。在高压容器处于高温密封的情况下加入水,水会蒸发,从而增加压力和湿度,为高压容器内的样品创造必要条件。

类似于温湿度储存测试,高压炉测试曾是用于厚半导体封装可靠性测试的重要方法。然而,从目前JEDEC的评估结果及最新的国际趋势来看,高压炉测试对于当前的封装来说,应力幅度过大。因此,这项测试方法需根据封装类型有选择性地使用。高压炉测试主要用于引线框架产品,而无偏压高加速应力测试(UHAST)主要应用于基板产品。

无偏压的高加速应力测试、高加速应力测试和高加速寿命测试

无偏压高加速应力测试(UHAST)是通过对薄封装的基底类型产品,如细间距球栅阵列封装(FBGA)产品施加与高压炉测试相似的应力,来评估产品可靠性。这两项测试在识别和发现产品失效类型方面也有相同之处,高压炉测试采用饱和湿度或100%相对湿度来施加应力;而无偏压高加速应力测试,则采用与用户环境相似的相对湿度为85%的非饱和湿度条件。该测试方法主要采用电偶腐蚀(Galvanic Corrosion)9或直接化学腐蚀。

9电偶腐蚀(Galvanic Corrosion):一种当较活泼的阳极金属与较耐腐蚀的阴极金属在电解质溶液中接触时,较活泼的金属易被腐蚀的电化学过程。

另一项评估是高加速应力测试(HAST),用于评估非密封封装在潮湿环境下的可靠性。 这项测试采用与温湿度偏压测试相同的方法, 引脚在静态偏压的状态下,继续向其施加温度、湿 湿度及压力应力。最后是高加速寿命测试(HALT),这是一种快速应力测试,有助于在产品设计阶段识别和纠正设计缺陷。

机械因素可靠性测试

半导体产品在搬运、储存、运输和运行过程中,会受到机械、气候和电气因素造成的环境压力,这些负荷会严重影响产品的设计可靠性。因此,有必要对开发中或批量生产的产品进行评估,以监测此类异常情况。在评估过程中,制造商可对产品施加振动、冲击或跌落等物理应力。

冲击测试

冲击测试通过模拟产品在搬运和运输中可能受到的冲击,来评估产品的抗冲击力。典型的冲击测试包括锤击测试和跌落测试。锤击测试时将测试样品固定在适当位置,然后用锤子敲击;跌落测试是指让产品自由向下跌落。锤击测试用于评估产品可承受的锤击力和脉冲承受能力,以及冲击次数。而跌落测试中,测试样品需要在1-1.2米的高度自由向下跌落,以模拟用户的实际工作环境。

振动、弯曲和扭转测试

振动测试是用于产品在运输期间可能发生振动的抵抗力评估,通常采用符合JEDEC标准的正弦振动(Sine Vibration)10实验方式。

10正弦振动(Sine Vibration):频率随时间而变化的振动。

其它测试还包括弯曲测试和扭转测试。弯曲测试用于评估因印刷电路板(PBC)翘曲或弯曲造成的焊点缺陷;扭转测试也被称为扭曲或扭矩测试,用于评估受到扭转应力时,产品的焊点问题和翘曲承受力。

确保提供可靠的半导体产品

本篇文章所介绍的可靠性测试及标准,是确保这些重要元件符合当今科技世界严苛标准的根基。从环境条件测试、机械因素测试,到产品寿命测试等各项评估方法,皆体现了半导体行业致力于生产可靠、耐用产品的决心。值得一提的是,SK海力士不遗余力的坚持旗下产品始终采用最高可靠性标准,并不断超越客户预期。未来,公司将紧随不断发展的技术趋势,继续完善和审查可靠性测试。

657

657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?