前情提要

- 由於 參考資料 [1] 雖然內容完整,但是使用的是中芯製程;而 參考資料 [2] 雖然內容不完整,但是使用的是台積電製程,故產生這份研究筆記

- 注意 : 此份研究筆記並沒有考慮到任何 PVT variation 以及 layout 寄生效應!

- 注意 : 此份研究筆記僅為作者個人理解,並不保證正確,且有些地方作者個人也尚未理解透徹,歡迎留言指正,再次感謝!

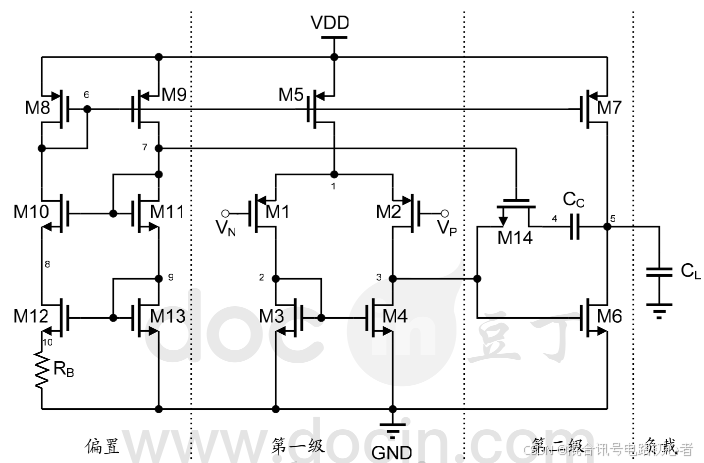

電路

- two stages (5 transistors OTA & CS)

- double input

- single output

- miller compensation with nulling resistor

- 沒有 CMFB 電路

- 有 bias 電路,但沒有 start up 電路

( 圖片來源 : 參考資料 [1] )

規格

| area | - |

| loading capacitor | 10 pF |

| input common mode voltage (ICMR) | (VDD + VSS) / 2 |

| output voltage range |

0.1*(VDD-VSS) ~ 0.9*(VDD-VSS) |

| static power loss | < 2 mW |

| open loop gain | - |

| unit gain bandwidth | 5 MHz |

| phase margin | > 60 degree |

| slew rate | > 10 V/(us) |

| CMRR | - |

| PSRR | - |

| equivalent input noise | - |

( 表格來源 : 參考資料 [2] )

製程參數

| nmos3v | |

| Kn | 184.4 u |

| Vth,n | 436.873 mV |

| pmos3v | |

| Kp | 37.6443u |

| | Vth,p | | 696.395 mV |

( 表格來源 : 參考資料 [2] )

| nmos2v Wmin. | 2 um |

| nmos2v Lmin. | 180 nm |

| nmos3v Wmin. | 2 um |

| nmos3v Lmin. | 350 nm |

| pmos2v Wmin. | 2 um |

| pmos2v Lmin. | 180 nm |

| pmos3v Wmin. | 2 um |

| pmos3v Lmin. | 350 nm |

- 使用 pmos3v 與 nmos3v

- 先進製程考慮到二階效應,需要用別的方法獲取製程參數,參見

- Vd, Vdsat, Vov 在舊製程與新製程有不同的關係,參見

設計原則

- 從最後一級逆推回去

- over drive voltage 不能太大 (具體來說多大算是太大?),否則 channel length modulation 會造成 output voltage range 受限

-

最後考量 (只和 L 有關)

手算設計

STEP 1

- 根據 參考資料 [2]

- 規格

,保有 20 % 彈性,故

(注意 : 要再乘以 2*pi 把單位轉成 radian)

- 規格

,根據

原則 (大於等於 0.22),得

- 根據 GBW 公式,得

- 規格

- 參見 參考資料 [3] (6.2-22)

- 沒有 nulling resistor

- 假設主極點在原點

- 假設 open loop gain 無窮大

- 假設 RHP 零點在 10*GBW

- 得次極點大於等於 2.2*GBW

- 根據 二级放大器设计

- RHP 零點在 10*GBW 避免影響

- 根據 二级运放设计

- 若不考慮 RHP 則次極點大於等於 1.73*GBW

STEP 2

- 根據 參考資料 [2]

- 規格 power < 1 mW,且 TSMC 0.18 um RF VDD = 3.3 V ,故總共可分配的電流為 300 uA

- 規格

,令

- 根據

公式得

,保有 20 % 彈性,故

(

)

- 根據

公式得

- 由於第一級增加 5 uA ,第二級為了維持原來的 SR ,也增加 5 uA ,得 140 uA

- 由

得

- (此為作者個人猜想,尚未驗證是否正確)

- 根據

- 根據 CSDN : two stages Op Amp design with gm / id - version 2

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

510

510

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?