一、模块简介

CPU的时钟频率和CPU的算力有很大关联,同一种类的芯片的时钟频率越高,算力越高,当然硬件上的功耗也会越严重,所以实际开发过程中,对于时钟频率的选择有一定的考究。时钟频率也是我们所说的主频,TC3XX系列MCU的主频最高支持300MHz。

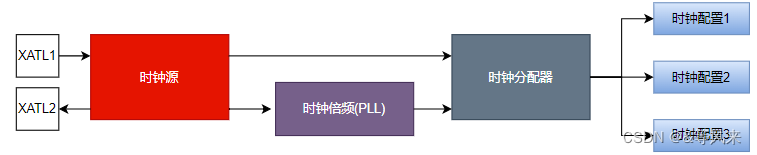

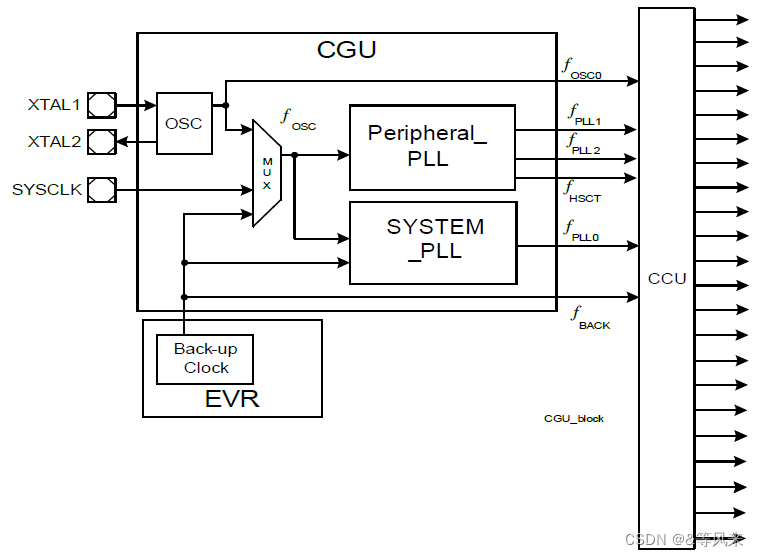

TC3XX时钟系统主要由时钟源、时钟倍频(PLL)、时钟分配器组成。

二、功能介绍

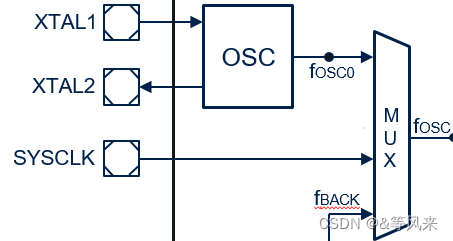

2.1 时钟源

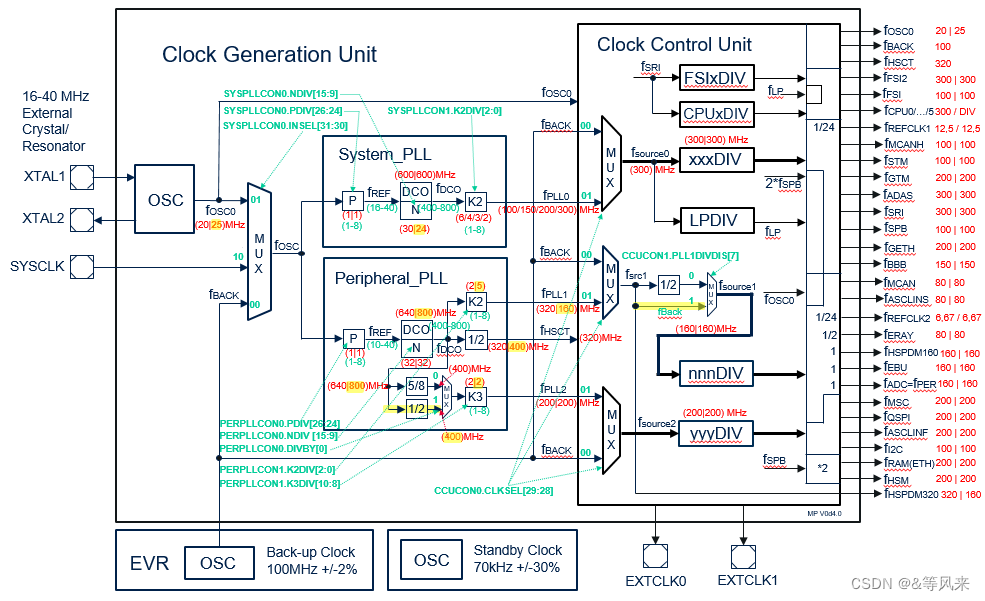

TC3XX有两种外部时钟源:一种是外部直接时钟源;另一种是采用石英或陶瓷晶振,再通过电路连接实现。软件层面,我们只需关注外部时钟源的频率fOSC。此外,TC3XX还提供了一种内置备用时钟,可以在主时钟异常时使用,但是精度相对不高。

2.2 时钟倍频(PLL)

时钟源一般为20MHz,怎么达到最高的300MHz的主频?这是通过PLL来实现的。

时钟系统中有两个PLL模块,一个是系统锁相环,产生的时钟提供给CPU,存储等模块使用;一个是外设锁相环,产生的时钟供GTM,ADC,CAN等外设模块使用。

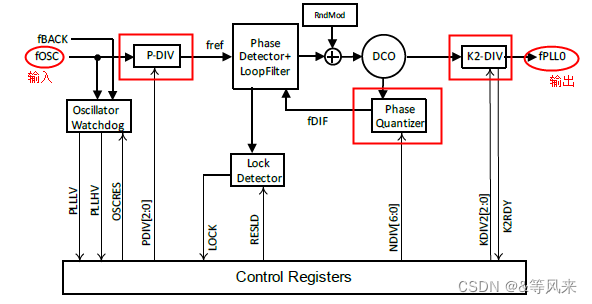

2.2.1 系统锁相环

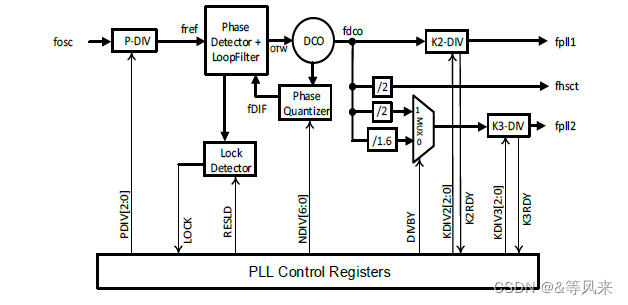

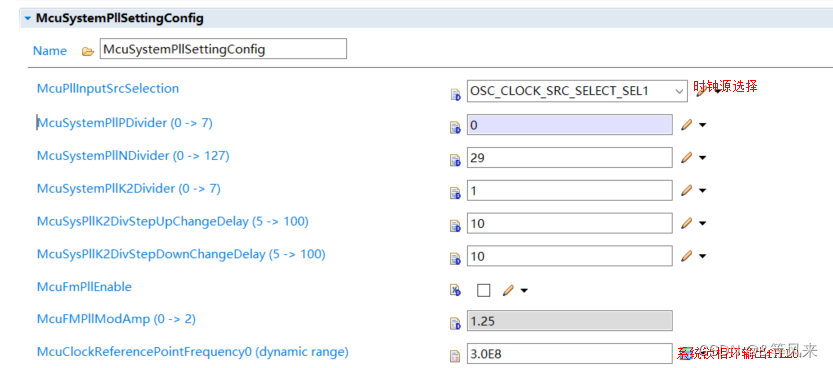

如上图所示,输出频率fPLL0 = fOSC * N/ (P * K2)

- P:预分频值P-DIV+1

- N:反馈分频值NDIV+1

- K2:输出分频值K2-DIV+1

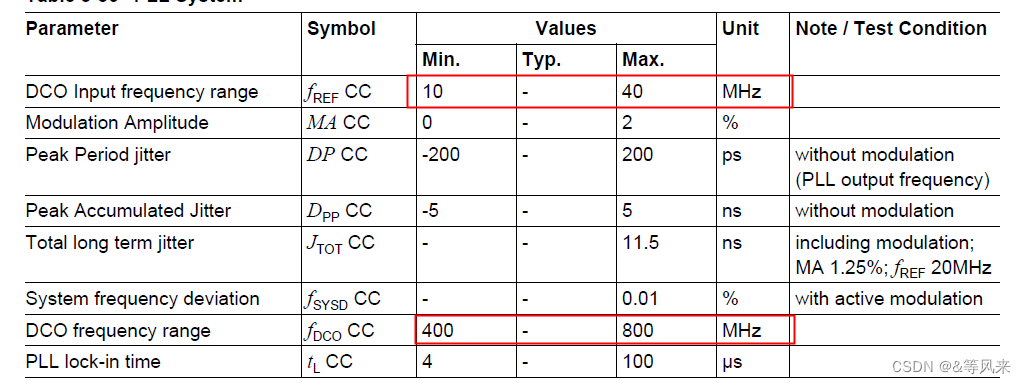

根据datasheet中DCO的输入范围[10,40MHz],且fDCO输入 fREF= fOSC/P,此时定P=1,则fREF = 20MHz。fDCO输出范围[400,800MHz],想要fLL0 = 300MHz,则fDCO = 600MHz,那么fDCO = fREF*N/K2,即600 = 20*N/K2,此时可以定N = 30,K2 = 1。

从系统锁相环的图中可以看出还有个振荡器看门狗,可以通过SYSPLLCON0.INSEL = 01B选择OSC时钟源作为看门狗输入,该特性用于检测外部晶体/陶瓷谐振器的严重故障。可以检测时钟输入的丢失或输入频率过高,结合系统锁相环实现监控功能。注意:当设置锁相环时,应关闭SMU中的锁相环监控,否则会误报TICK丢失故障。

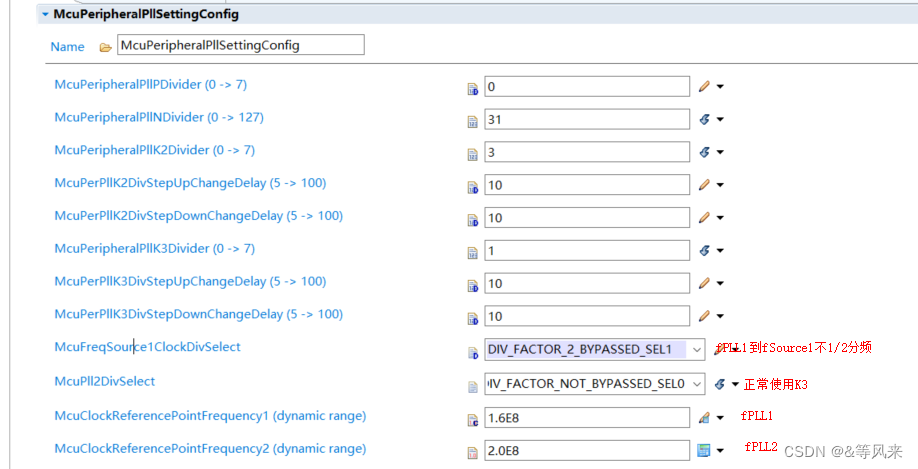

2.2.2 外设锁相环

fPLL1 = fOSC * N / (P * K2)

fPLL2 = fOSC * N/ (P * K3 * 1.6)(DIVBY = 0时)

fPLL2 = fOSC * N/ (P * K3 * 2)(DIVBY = 1时)

fHSCT = fOSC * N / (P * 2) (专供HSSL使用)

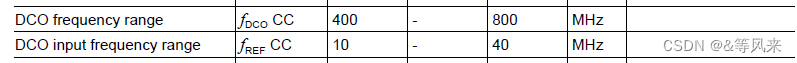

根据datasheet,外设DOC的输入输出频率范围如下:

考虑EMC问题,外设时钟频率要尽量与系统 时钟保持非倍数关系,一般PLL1设置为160MHz,PLL2设置为200MHz,类比系统PLL,这里系数P也设置为1,N=32,K2=4,K3=2,DIVBY=0。

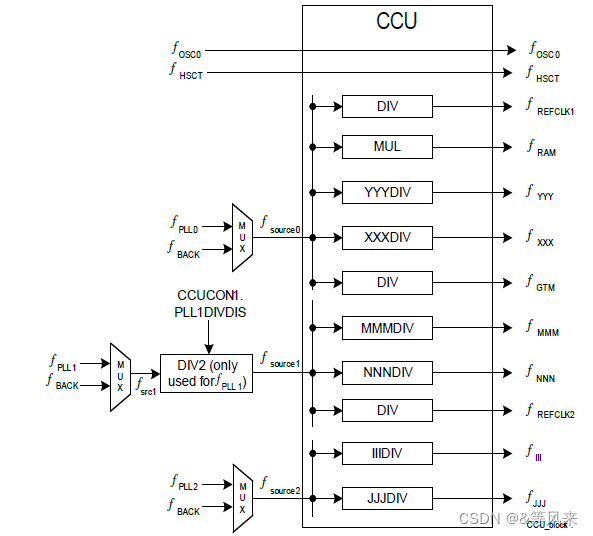

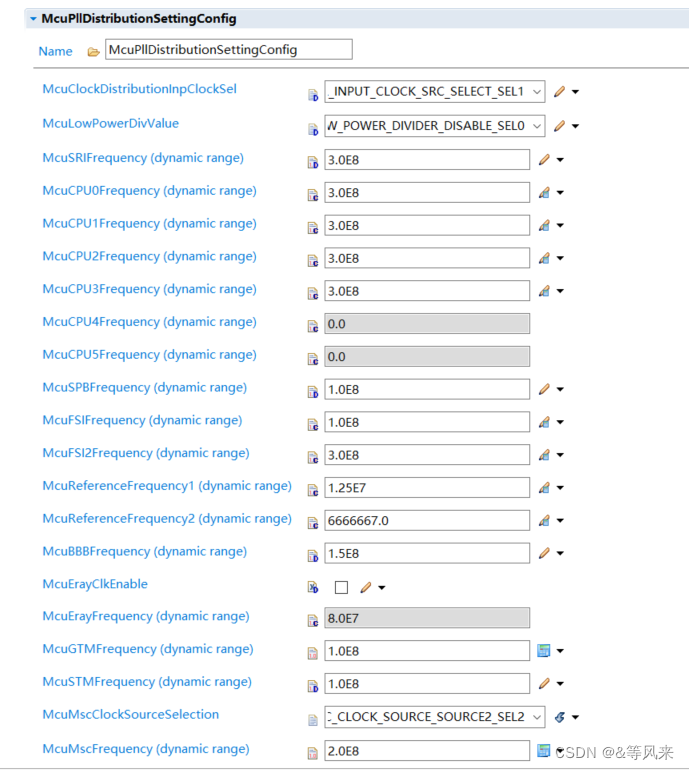

2.3 时钟分配单元(CCU)

CCU的输入源为两个锁相环(fPLL0和fPLL1/2),备用时钟fBACK以及fOSC0,框图如下:

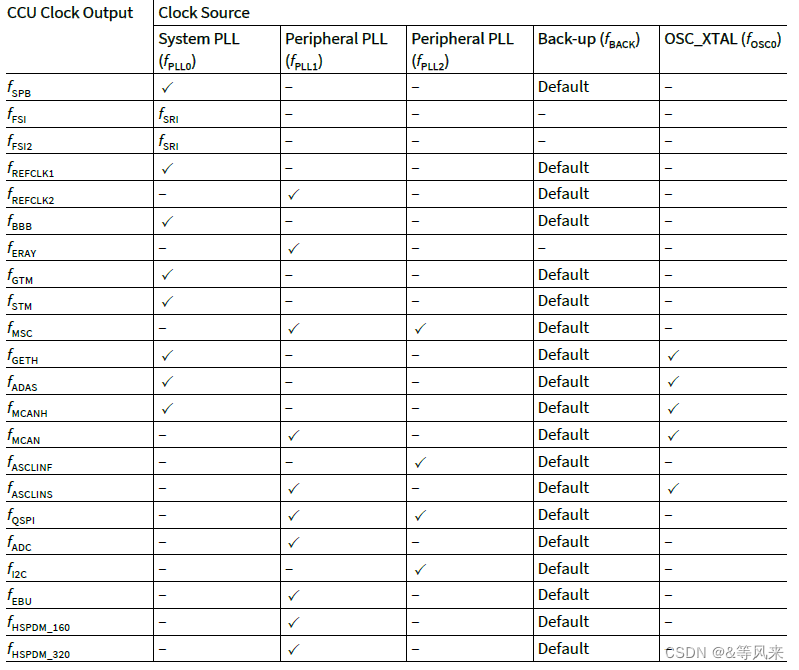

各模块的时钟源分配如下图:

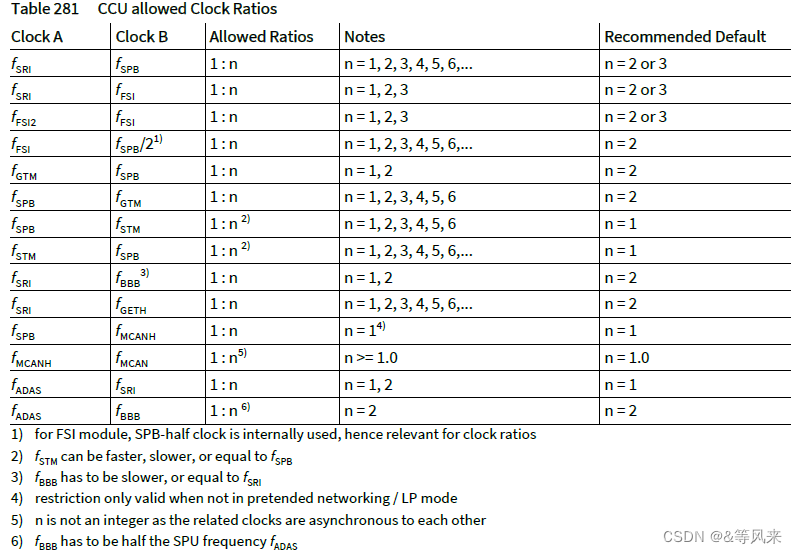

时钟分频还存在如下图所示的限制

2.4 时钟产生单元

当外部时钟输入源为20MHz|25MHz时,时钟系统图如下:

三、实战演练

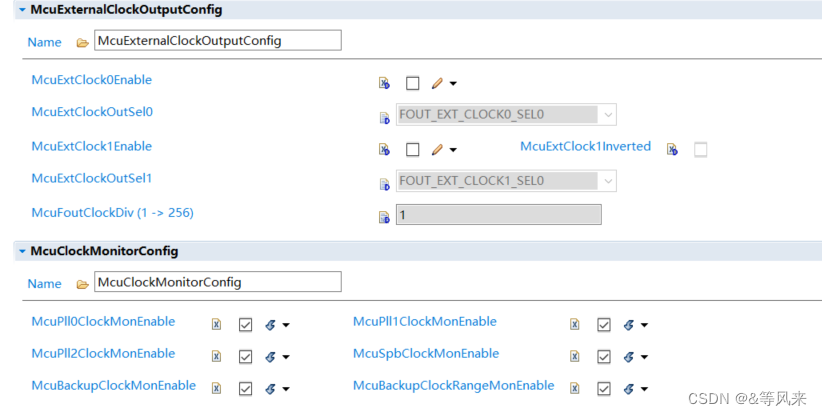

3.1 MCAL配置

3.2 代码编写

时钟的初始化一般在EcuM_AL_DriverInitOne中调用,但要注意,需要等到锁相环稳定后再进行时钟配置。

#define Mcu_InitClock() Mcu_InitClock(0);\

while(MCU_PLL_LOCKED != Mcu_GetPllStatus());\

Mcu_DistributePllClock()

Mcu_InitClock();

本文详细介绍了TC3XX系列MCU的时钟系统构成,包括时钟源、PLL倍频、时钟分配器和实战演练。重点讲解了如何通过PLL实现高主频,以及如何配置锁相环和CCU以优化外设时钟。

本文详细介绍了TC3XX系列MCU的时钟系统构成,包括时钟源、PLL倍频、时钟分配器和实战演练。重点讲解了如何通过PLL实现高主频,以及如何配置锁相环和CCU以优化外设时钟。

1839

1839

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?