- vcs -help

- lists compile options,run-time options,environment variables

命令行选项(常用)Command line options(commonly used)

- Mupdate(增量编译)

- Incremental compilation(only changed files are compiled)

如果只修改了一个代码,那就只进行修改的代码的编译,与其他文件重新做连接即可。

- Incremental compilation(only changed files are compiled)

- R

- run after compilation(编译完立即执行)

- gui

- starts the DVE gui at runtime(打开DVE的图形界面)

- l

- Set log file name(创建log文件)

- sverilog

- Enable System Verilog language support (支持SV语言)

- +v2k

- Compile with support for Verilog 2001 extensions(支持Verilog 2001标准)

- Compile-time options to access Verilog library files

-v lib fileSearch for unresolved module reference in file

lib file,如果在RTL代码里出现了厂商的工艺库,就可以通过-v+ 工艺库的名字,告诉vcs,如果你在RTL里发现了一个黑盒,你就到这个工艺库里面去找。-y lib dir| Search for unresolved module reference in files residing in directorylib dir这就是告诉VCS,你到哪里去找。+libext+lib ext| Use file extensionlib extwhen searching for files in library directorylib dir通过扩展名的方式,除了告诉VCS,这个库在哪里,还告诉这个库是以什么为后缀,是以.h为后缀,还是以.vh为后缀。+incdir+ inc dir| Searchinc dirdirectory forincludefiles 在源文件里如果用到了include的某一个文件, eg:

include "header .vh"

module

...

endmodule

告诉VCS,这个路径在哪里去找。

-

Access Verilog files and options via a file

-f file| File containing a list of absolute pathnames for thesource filesand a subset of VCS options (把所有的源代码进行整合,整合到一个filelist的文件里去)

-

User selected simulation binary name

-o fooGreate executablefooinstead ofsimv(默认条件下编译之后会产生一个叫simv的可执行文件,如果修改它,就会产生一个foo的文件)

-

Define a macro

+define +<macro_name> =<value>

VCS Simulation Command Format(VCS 仿真命令格式-动态开关)

- run_time_options(optional)

- Control how VCS executes the simulation binary

- Simulation result reported via

- Verilog system task calls

- User defined PLI routines

这些动态开关可加可不加,根据具体工程需要。

Run-time options example

-

Stop simulation at time 0

-sStop simulation at time 0

-

$plusargs() switches

+userswitch User defined run-time switch

-

Compline-time option status

-E echo| Display compile-time options used for the creation of the current simv executable

-

Log file control

-l logfileWrite output to logfile

Using DesignWare Library with VCS(这个库都是RTL代码)

- Instantiating DesignWare components in verilog

- Format

Dwpart #(parameters)u1(.porta(a),.portb(b)); - DesignWare multiplier example:

DW02_mult #(inst_A_width, inst_B_width);

u1(.A(inst_A),.B(inst_B),.TC(inst_TC),.PRODUT(inst_PRODUT));

- Format

- Accessing DesignWare simulation library

-y $SYNOPSYS/dw/sim ver+libext+.v+(是以.v文件作为后缀的)

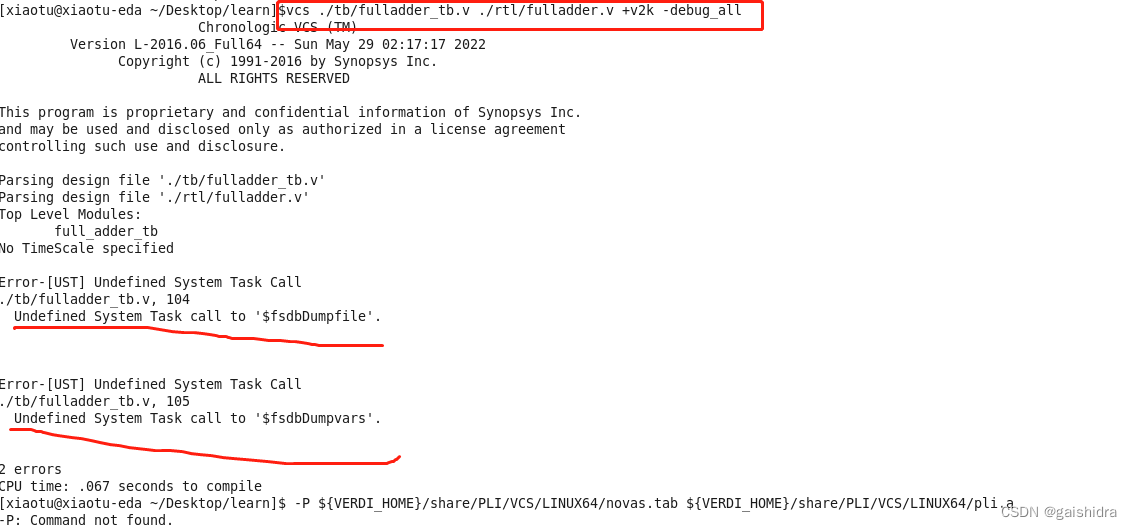

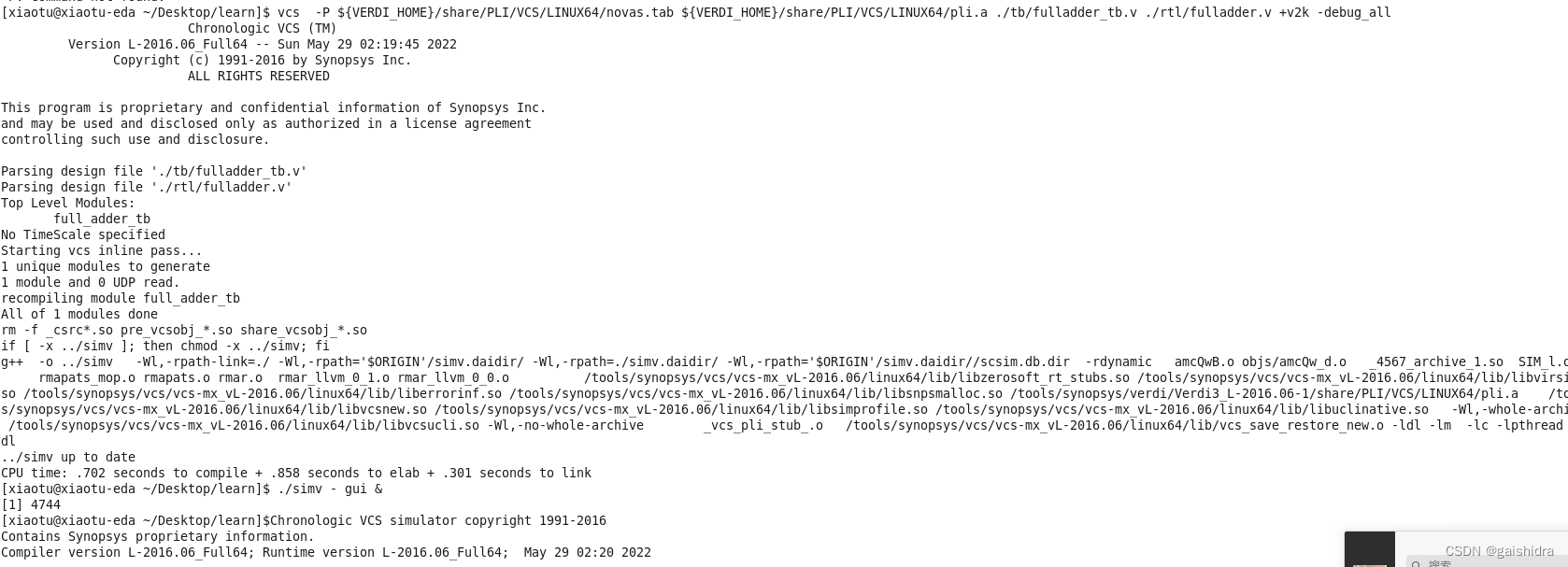

关于fsdbDumpvars/fsdbDumpfile Undefined的问题解决办法

上图可以看出,当我们在命令行中输入

VCS ./tb/fulladder_tb.v ./rtl/fulladder.v +v2k -debug_all

会报出如标题的错误;

这时候的解决办法是在命令行中加上这句代码:

-P ${VERDI_HOME}/share/PLI/VCS/LINUX64/novas.tab ${VERDI_HOME}/share/PLI/VCS/LINUX64/pli.a

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?