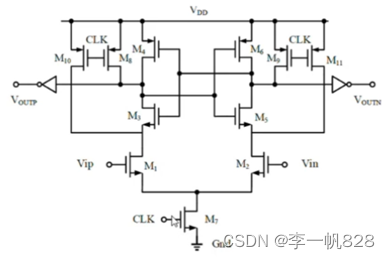

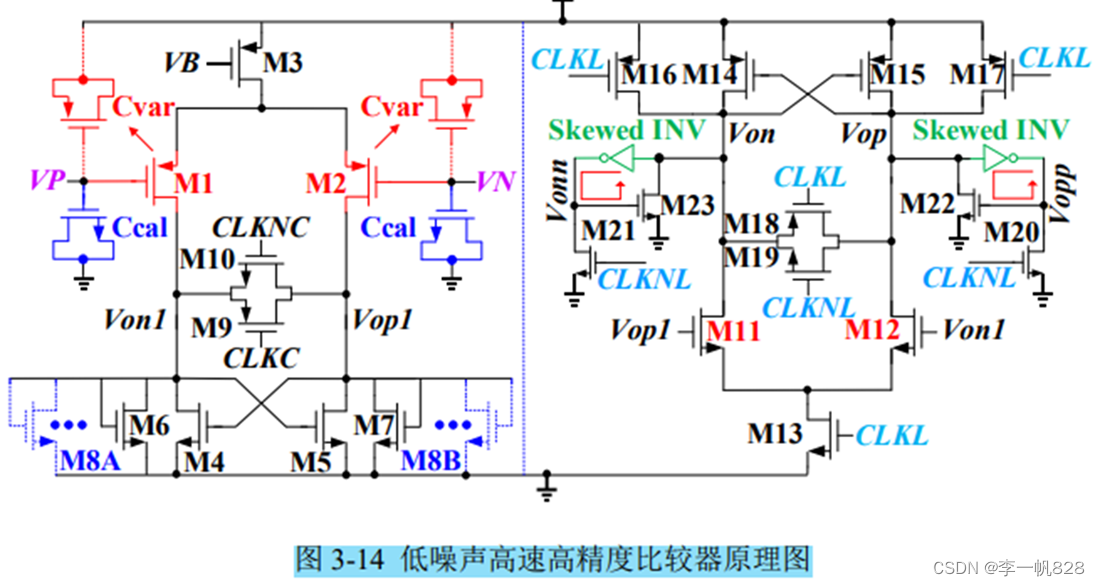

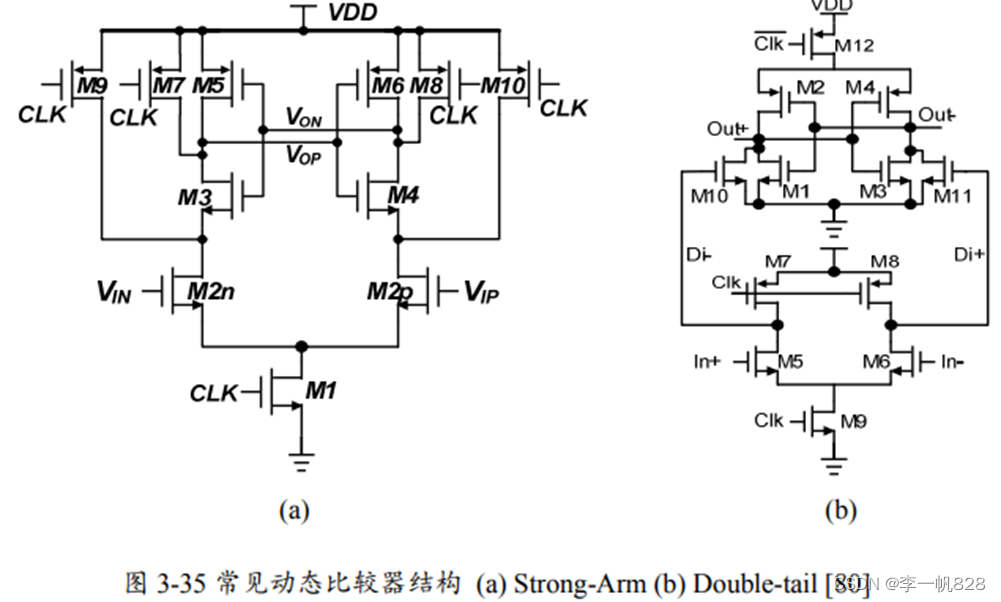

应用在SAR ADC中的比较器结构多为StrongArm结构【拉扎维 】或Pre-AMP LATCH结构。这两个结构各有优劣和适用范围。左图的StrongArm结构速度上不是很快,且从电源到地有4层MOS管,对于电源电压较低的工艺并不适用。右图Pre-AMP LATCH组合,静态运放的时域响应和动态LATCH的时域响应刚好互补,Pre-AMP放大小信号较快,LATCH放大大信号较快,两者结合,Pre-AMP先将一个小信号放大到Vx,然后由LATCH接管正反馈迅速放大,速度大大加快。

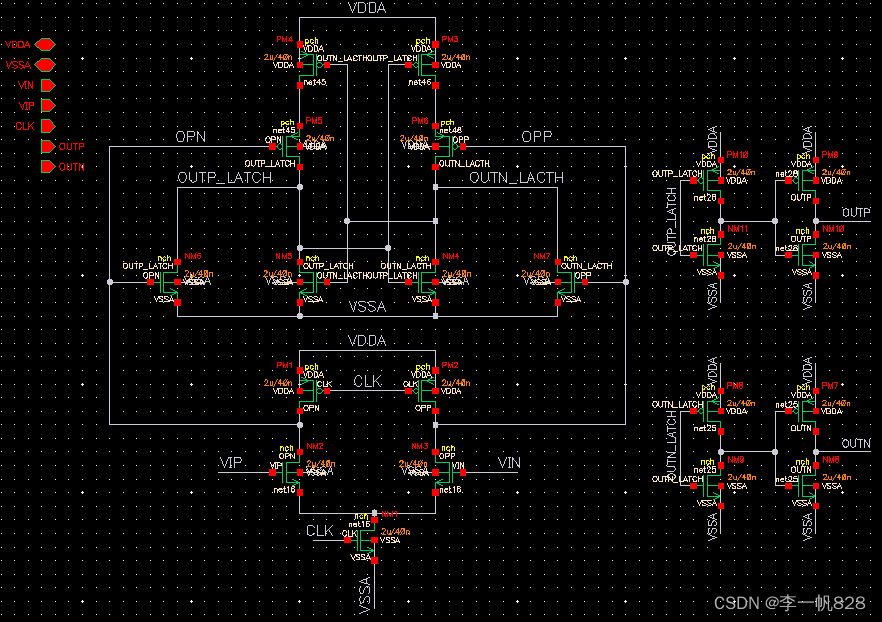

本文要仿真的电路如下图图(b)所示,输入增益级、输出锁存器组成的双尾电流型动态锁存比较器,它能在较宽共模电平范围内保持较稳定的失调电压,同时也能工作在较低的电源电压下。

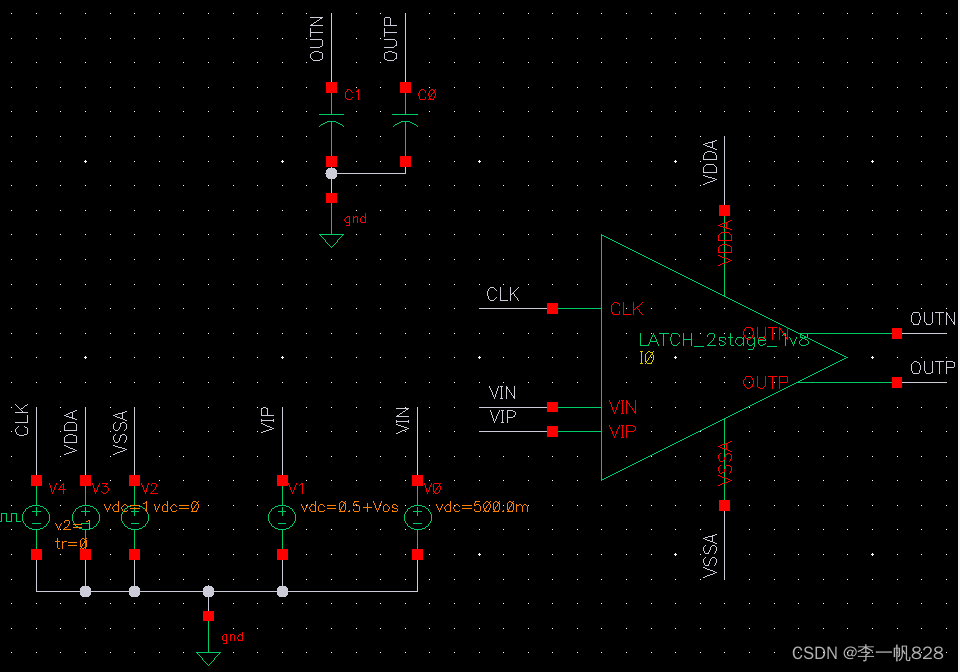

搭建双尾电流型动态锁存比较器电路图和仿真电路图,其中PM1-10:2/0.04μm,NM1-11:1/0.04μm,TSMC40nm工艺。

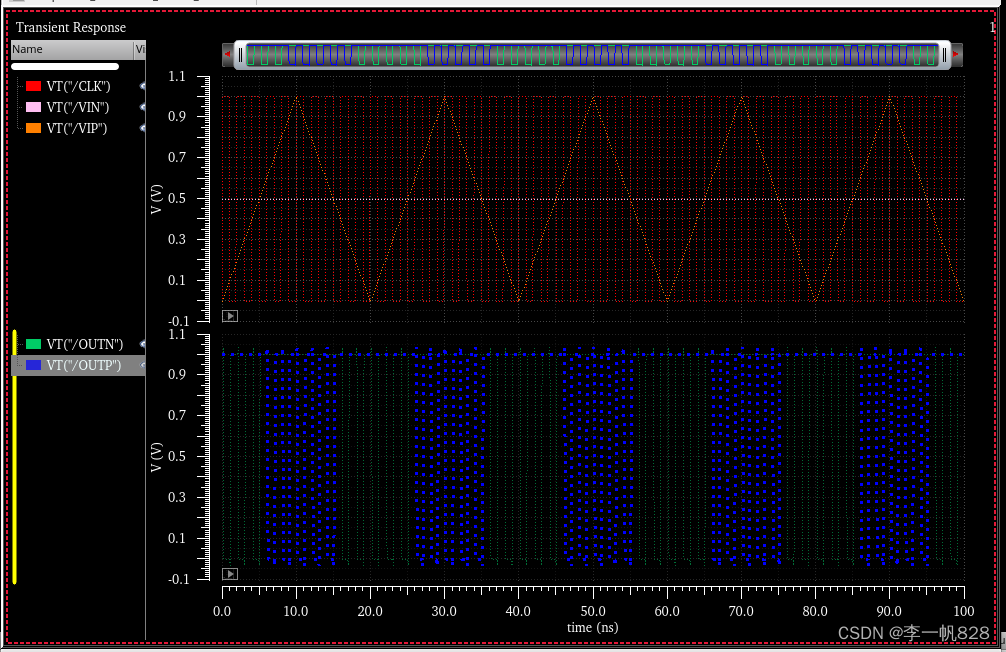

接下来需要设置仿真电路图中的各个激励源。其中:VIN:vdc=500mv;VIP:vpulse=0-1V,三角波,T=20NS;VSSA=0V;VDDA=1V;clk:voltage1=0v,voltage2=1v,period=2ns, pulse width=1ns;C2-3=1pF。本次仿真结果见下图。【cadence中激励信号的设置可参考cadence virtuoso 激励信号源_vpwl信号源-CSDN博客】

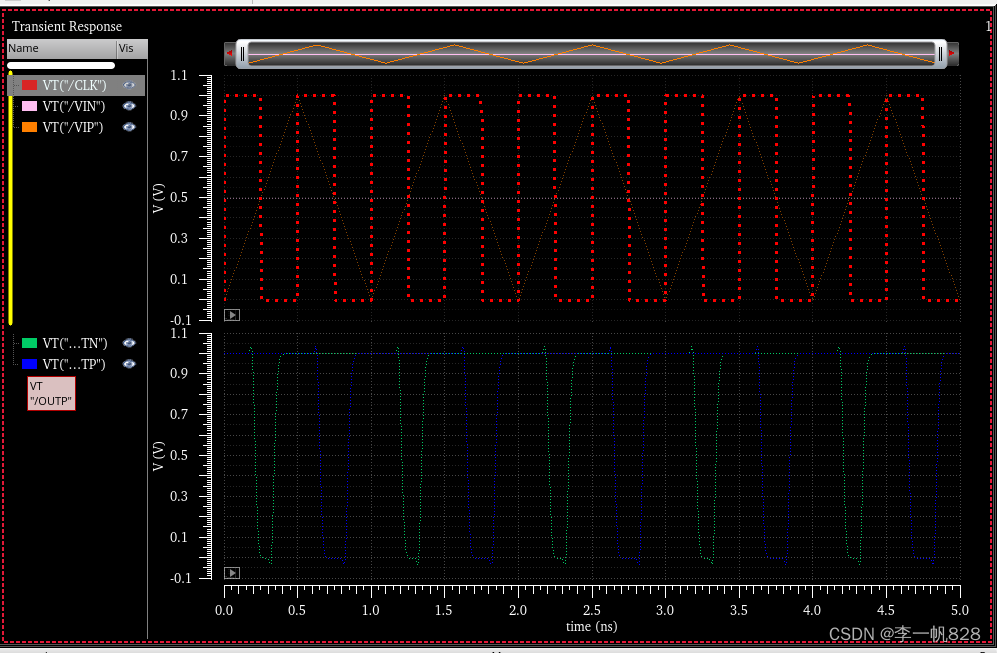

继续对这个双尾电流动态比较器仿真,查看最高clk频率能到多少。设置clk:voltage1=0v,voltage2=1v,period=500ps, pulse width=250ps;VIP:vpulse=0-1V,三角波,T=1ns;其余激励源不变。仿真结果见下图。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?