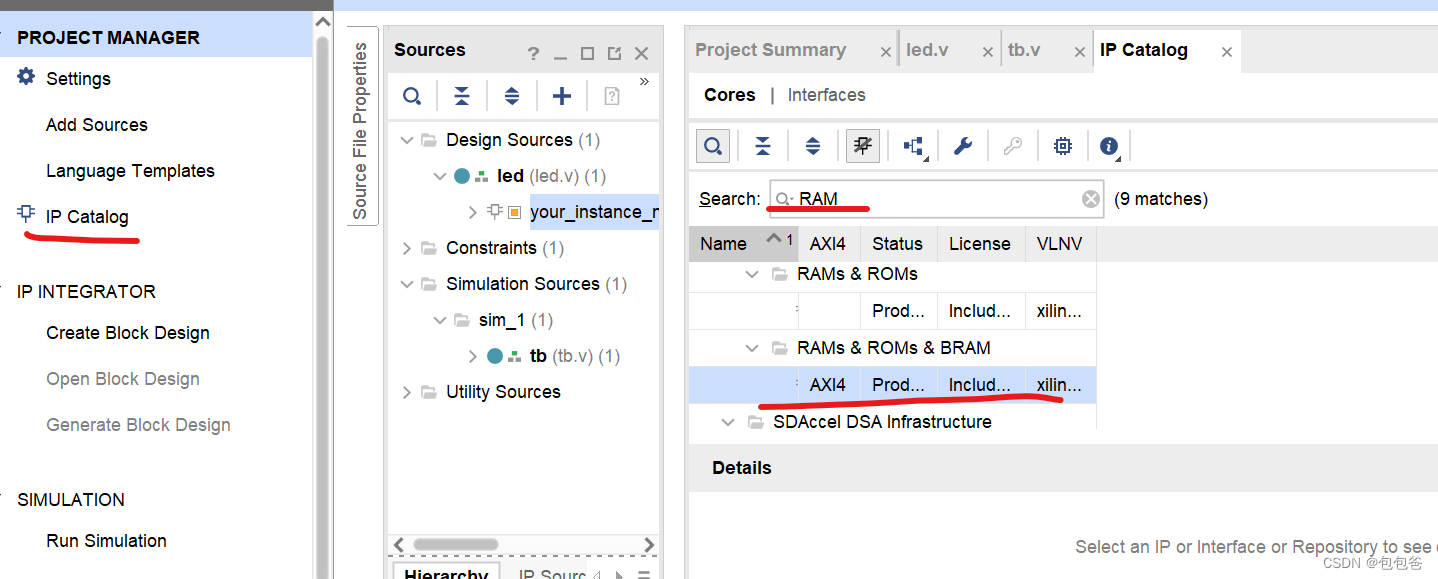

现在vivado里选择IP->BRAM

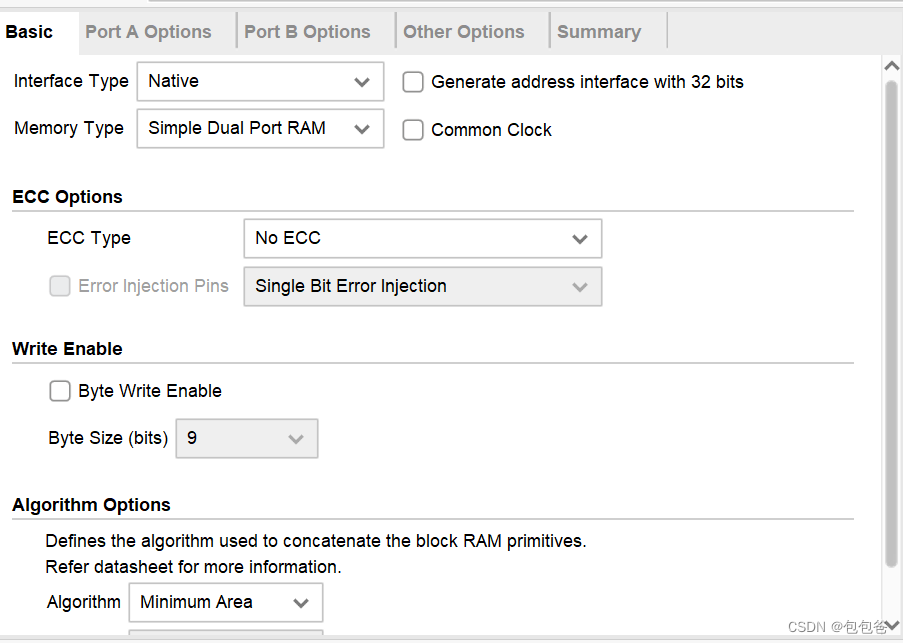

相应的设置如下,这里使用的simple dual port

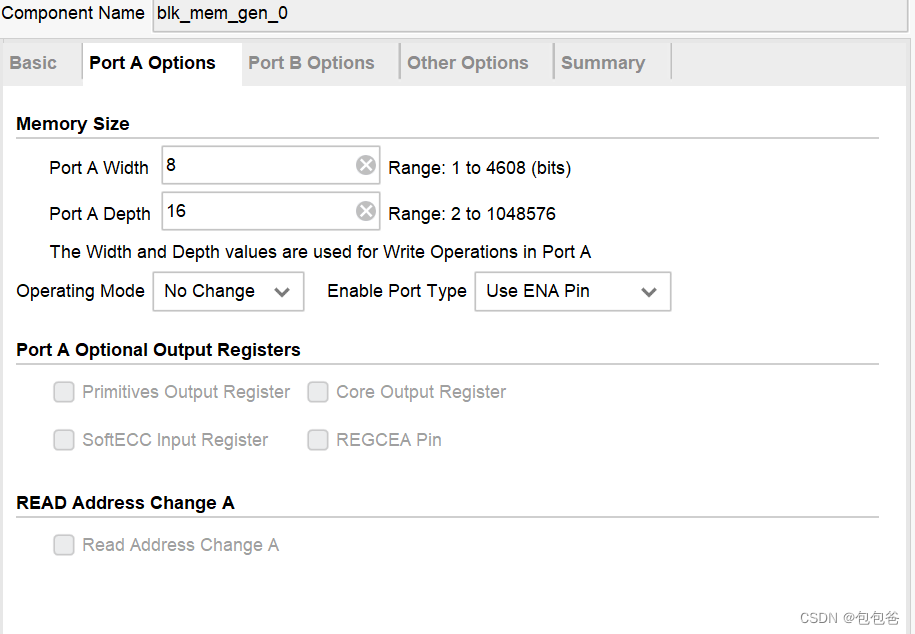

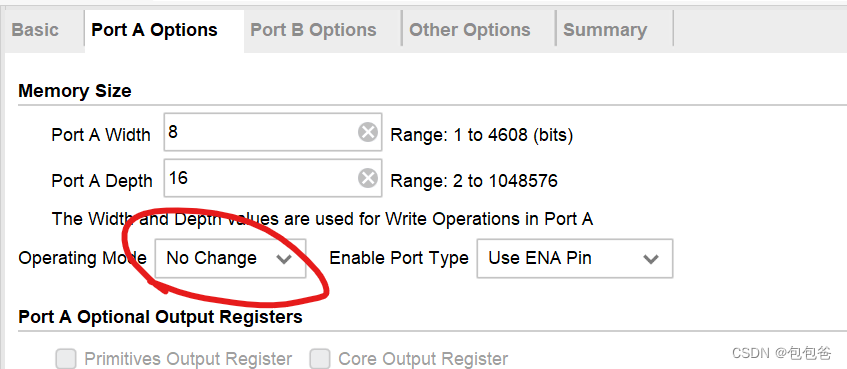

PORT A设置

PORT A设置

PORT B设置

测试用代码如下

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/02 15:30:56

// Design Name:

// Module Name: led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led(

input clk,

input rst_n,

output reg[1:0]led

);

reg ena;

reg wea;

reg [3:0]addra;

reg [7:0]dina;

reg enb;

reg [3:0]addrb;

wire [7:0]doutb;

reg [7:0]cnt;

//write

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else begin

if(cnt == 20)begin

cnt <= 0;

end

else begin

cnt <= cnt + 1'b1;

end

end

end

//write

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

ena <= 0;

wea <= 0;

addra <= 0;

dina <= 0;

addrb <= 0;

enb <= 0;

end

else begin

if(cnt == 1)begin

ena <= 1;

wea <= 1;

end

else if(cnt > 1 && cnt < 8)begin

addra <= addra + 1'b1;

dina <= dina + 1'b1;

end

else if (cnt == 8)begin

ena <= 0;

wea <= 0;

end

else if (cnt == 9)begin

enb <= 1;

end

else if(cnt > 9 && cnt < 16)begin

addrb <= addrb + 1'b1;

end

else if (cnt == 17)begin

wea <= 0;

enb <= 0;

end

end

end

blk_mem_gen_0 your_instance_name (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [3 : 0] addra

.dina(dina), // input wire [7 : 0] dina

.clkb(clk), // input wire clkb

.enb(enb), // input wire enb

.addrb(addrb), // input wire [3 : 0] addrb

.doutb(doutb) // output wire [7 : 0] doutb

);

endmodule

Testbench如下

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/11/23 13:17:00

// Design Name:

// Module Name: tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb(

);

reg clk;

reg rst_n;

wire [1:0] led;

led u1(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

initial

begin

clk = 0;

rst_n = 0;

#200

rst_n = 1;

#1000_000

$stop;

end

always #10 clk = ~clk;

endmodule

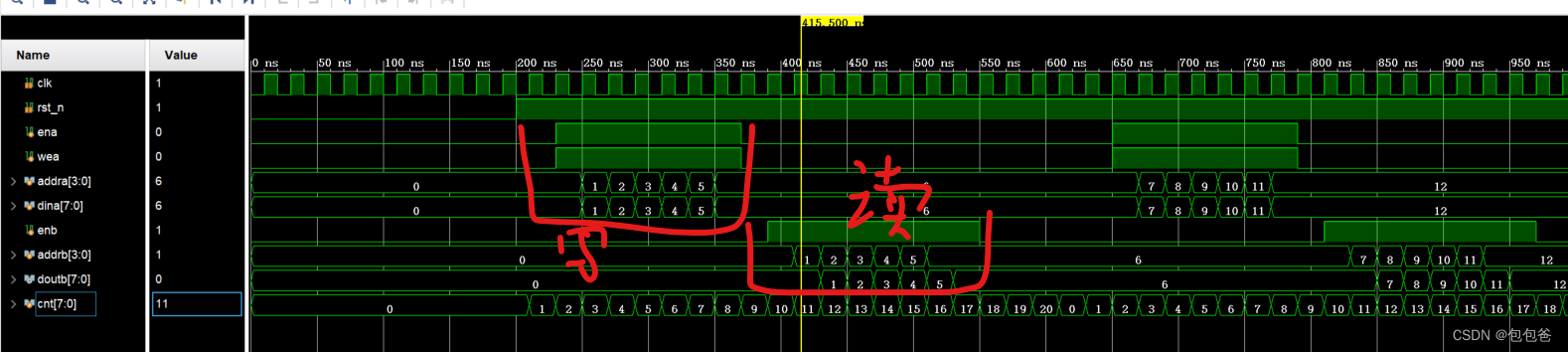

仿真波形如下,可以看到portA写入的数据,可以从portb读出。

以上用的是No change模式,接下来试下其他的模式,试了下write first,波形没有变化。

write first的意思是在写入的同时,会同时输出的out上。在这个模式没有变化,可能是因为不存在冲突吧。

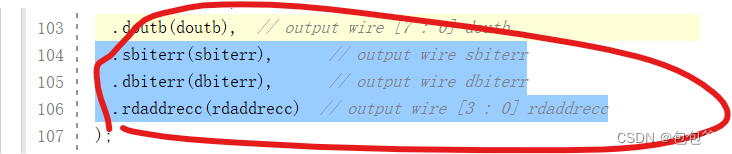

接下来试下ECC功能,勾选以后多了biterr位

后面再试试如何使用,

待续

2715

2715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?