I2C通信协议详解(二) --- I2C时序及规格指引

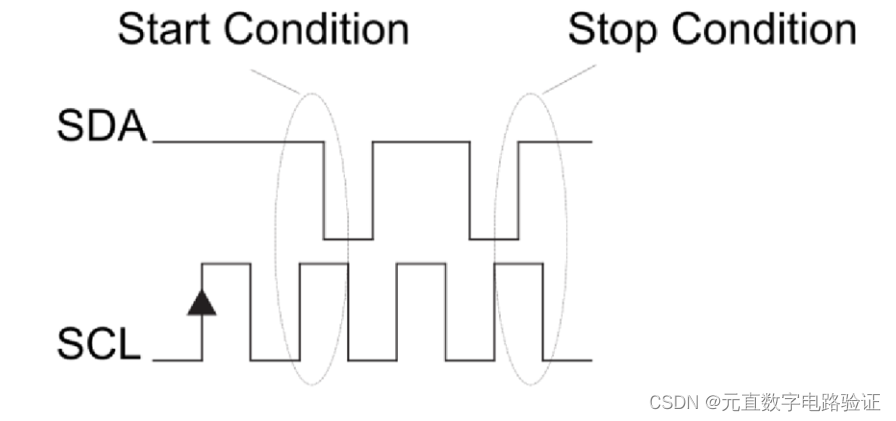

前言:在这篇博文中,我们将讨论 I2C 时序规范以及制造商有时提供这些规范的各种方式。有关 I2C 及其协议的入门知识,请参阅I2C通信协议详解(一)。下面是I2C的读写时序:

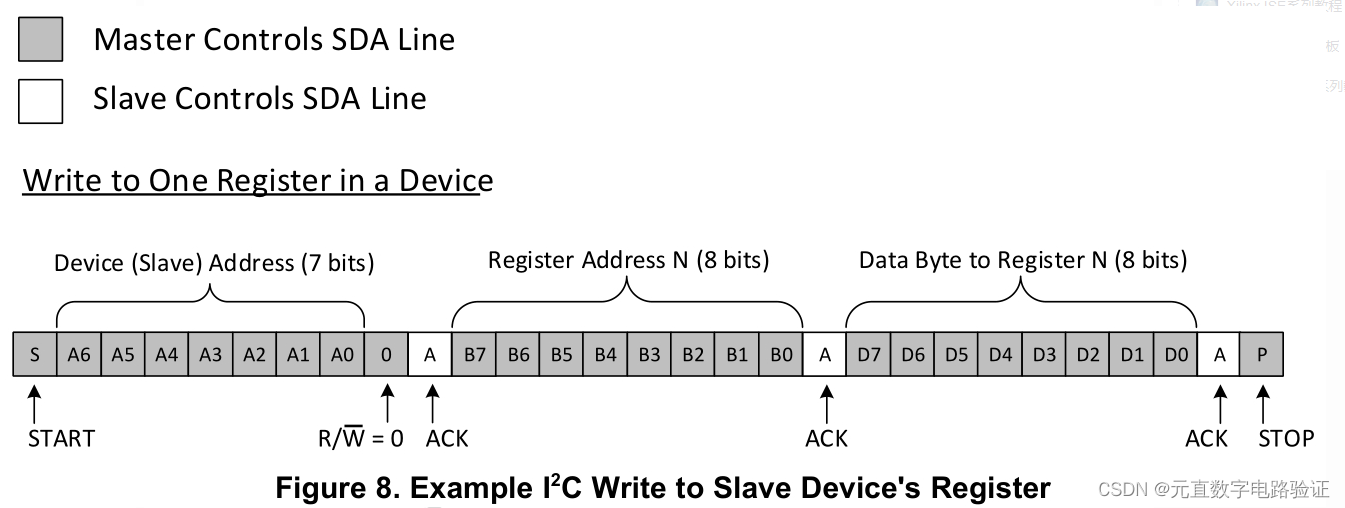

- 向指定寄存器地址写入指定数据操作时序:

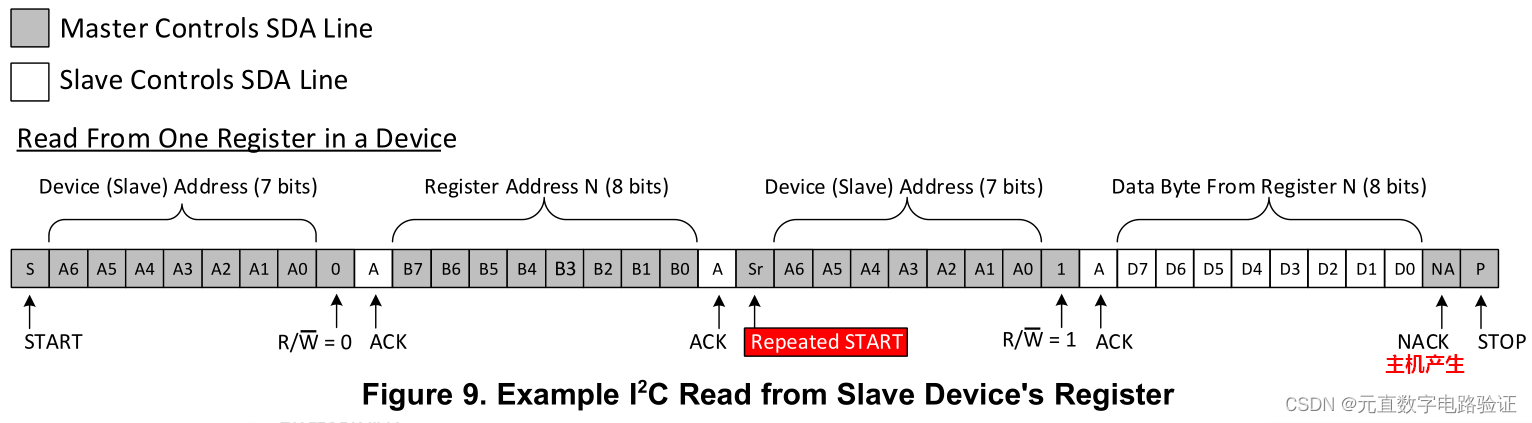

- 从指定寄存器地址读取数据操作时序:

I2C 数据传输通过物理两线接口进行,该接口由单向串行时钟 (SCL) 和双向数据 (SDA) 线组成。这些传输可以在标准模式下 100kbits/s、快速模式下 400kbits/s、Fast Mode Plus 下 1Mbits/s 以及高速模式下高达 3.4Mbits/s 的速度下发生。每个数据速率都有自己的时序规范,主机和从机必须遵守这些规范才能正确传输数据。 I2C 兼容设备必须能够以自己的最大比特率跟踪传输,即能够以选定的数据速率发送或接收数据。有一些细微差别,例如在给定数据速率下正确数据传输的建立和保持时间。我们将在这篇博文中讨论这些规范。

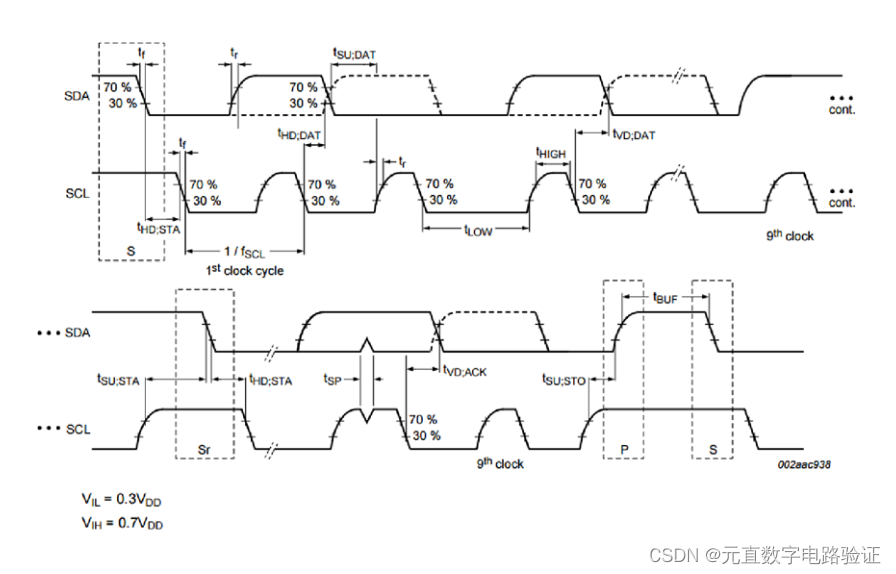

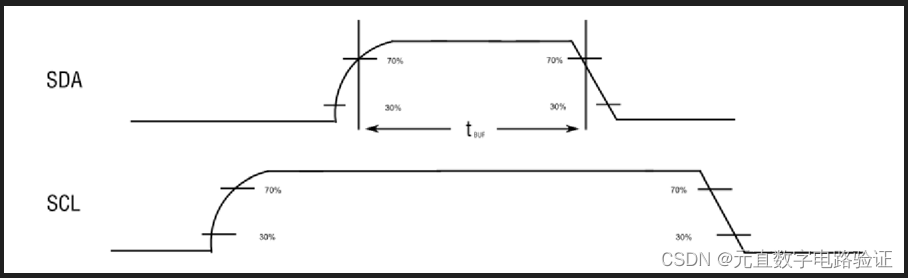

图 1 取自恩智浦“I2C 总线规范和用户手册”,描绘了一个时序图,它提供了 I2C 总线上快速模式设备的各种时序规范的定义。我们将仅使用快速模式时序图进行讨论,因为大多数 LTC I2C 部件都支持这种模式。然而,所讨论的定义也适用于其他速度模式。我们还将仅讨论这些规范如何应用于从设备,因为凌力尔特 I2C 兼容设备通常是从设备。

一、Rise (tr) and Fall (tf) Times

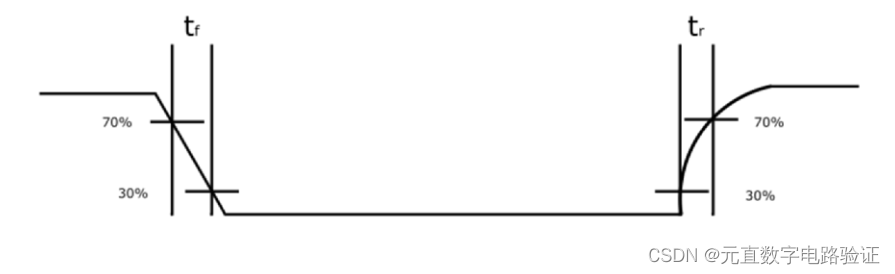

tr 定义为 SDA 和 SCL 的上升沿从 30% 幅度达到 70% 幅度所用的时间量,而 tf 定义为下降沿从幅度达到 30% 幅度所用的时间量 70%。

二、Setup and Hold Times

建立时间定义为数据在采样之前必须保持稳定的时间量。 该时间间隔通常在SCL上升沿和 SDA改变状态之间。 另一方面,保持时间定义为采样开始后的时间间隔。 该时间间隔通常在 SCL 下降沿和 SDA 改变状态之间。 在这些时间间隔内保持数据稳定很重要,否则会导致数据采样不正确。

在 I2C 标准中,这些间隔所需的最小时间量(因工作速度模式而异)被指定用于 START 和 STOP 条件以及数据位。 在这些参数中指定 I2C 兼容从设备以识别传入数据。

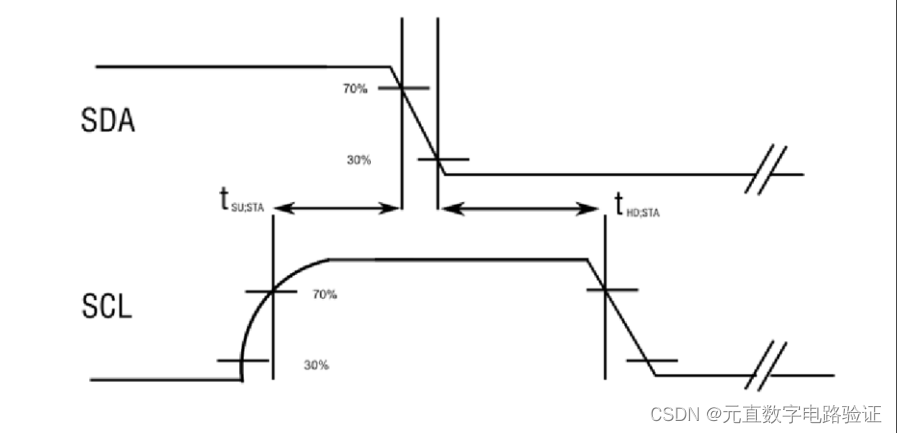

三、Setup and Hold Time for Start Condition

回想一下,开始条件定义为当 SDA 线在 SCL 转换为低电平之前变为低电平时,即当 SCL 线为高电平时,SDA 转换为低电平状态。

开始条件的保持时间 (tHD;STA):是在 SCL 变低之前数据应该变低的最短时间。 它被测量为从 SDA 的 30% 幅度从高到低转换到 SCL 幅度从高到低转换的 70% 所用的时间。

启动条件的建立时间 (tSU;STA):是仅在重复启动条件期间考虑的时序规范。 这是在开始重复启动之前 SDA 线需要保持高电平的最短时间。 这被测量为 SCL 从 LOW 到 HIGH 转换的 70% 幅度和 SDA 从 HIGH 到 LOW 转换的 70% 幅度之间的时间间隔。

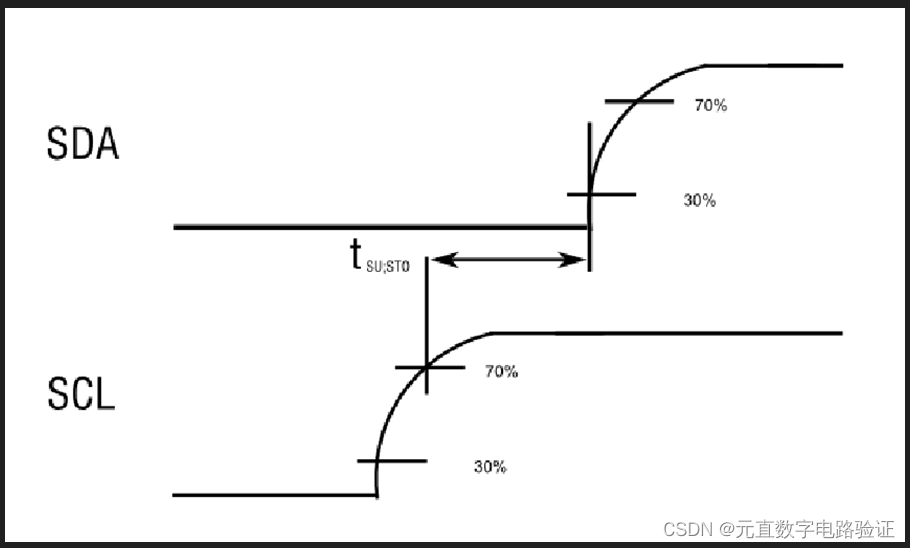

四、停止时间设置

在停止条件下,SCL 转换为高电平后,SDA 转换为高电平状态。 请参见图 3。停止条件没有保持时间要求,但仍需要最短建立时间。

停止条件的建立时间 (tSU;STO) 测量为在停止条件期间 SCL 上升沿的 70% 幅度和 SDA 上升信号幅度的 30% 之间的时间。

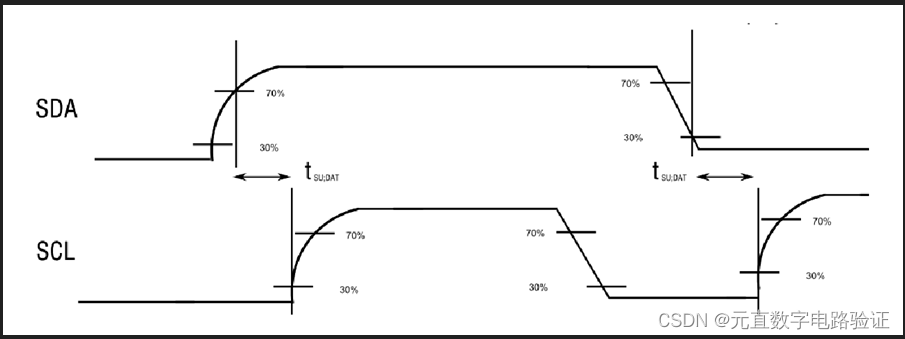

五、Setup Time for Data (tSU;DAT)

同样,数据也有一个建立时间,定义为在 SCL 转换发生之前 SDA 达到稳定电平所需的最短时间。 这是在下降沿期间 SDA 的 30% 幅度或上升沿期间 SDA 的 70% 幅度和上升沿期间 SCL 的 30% 幅度之间测量的。

六、Data Valid Time (tDV;DAT)

在每次数据和时钟转换时测量数据的有效性。 I2C 规范规定了不同速度下允许的最大数据有效时间。 数据有效时间 tDV;DAT 是在 SDA 的 30% 的下降沿或 SDA 的 70% 幅度的上升沿之间测量,参考 SCL 下降沿的 30%。 还有一个单独的确认有效时间规范 tDV;ACK,其测量类似于数据有效时间,不同之处在于它仅在第 8 个时钟位的下降沿测量。 请参见图 1。

七、Buffer time (tBUFF)

缓冲时间指定停止和启动条件之间的总线空闲时间。 该时间段允许总线上的其他设备检测空闲总线并尝试传输数据。 从设备通常将此指定为所需的最小总线空闲时间。 如果主设备(之前与另一个设备通信)尝试寻址从设备,但不让其停止和启动条件之间经过缓冲时间,则从设备可能无法将新的启动条件区分为单独的事务,并且可能不会 回应。

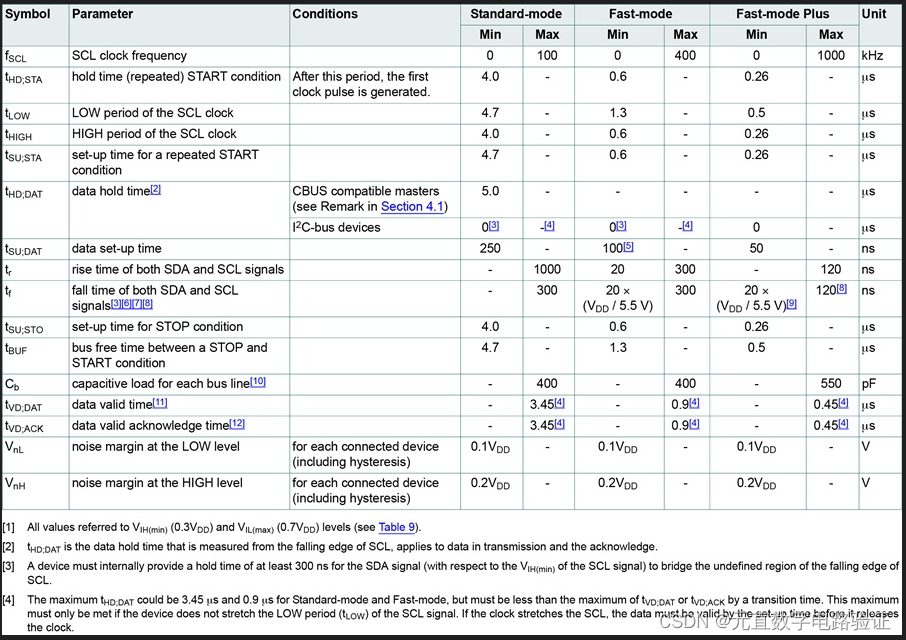

现在我们已经定义了各种时序规范,让我们看看 I2C 规范是如何指定它们的。 参见 NXP I2C 用户手册中的图 8。

I2C 规格表定义了其参数,以允许 IC 设计人员设计其 IC 以与总线要求兼容。 例如,与快速模式 I2C 兼容的 IC 将被设计为识别至少 0.6µs 的启动条件保持时间。 它可以设计为识别更快的保持时间,但至少它应该识别高达 0.6µs 的时间。

采用此规范,制造商以两种方式定义其 IC 的 I2C 兼容性。 下面提供了其中的示例。

八、Slave I2C Timing Specifications: Two Perspectives

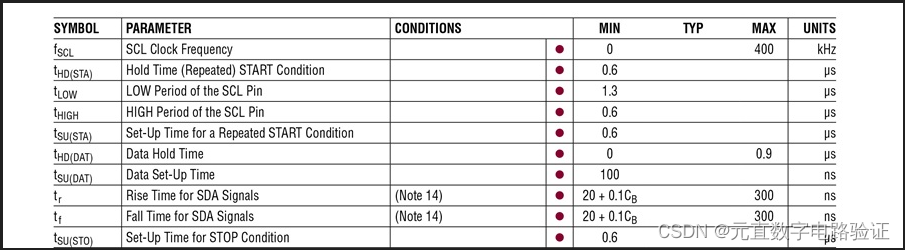

- LTC2493是一个24位Delta Sigma ADC,它的I2C时序如下:

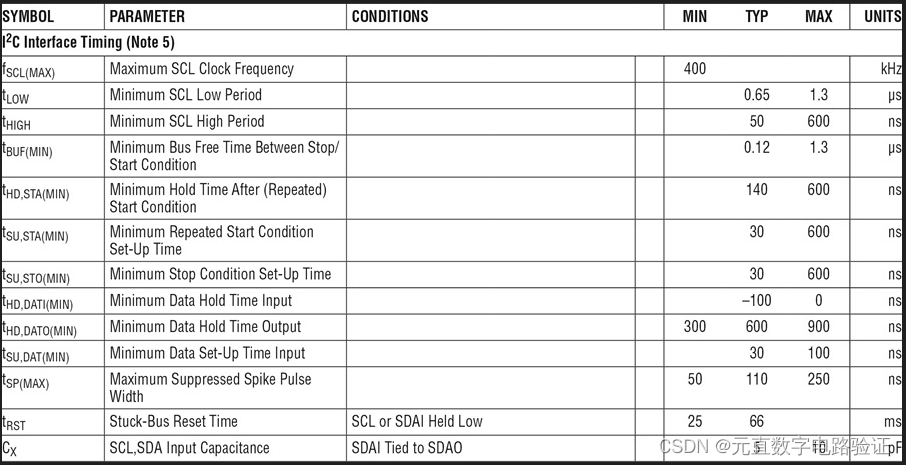

- 而作为 48V 热插拔控制器的 LTC4261 指定时序如下所示:

注意到差异了吗?两种设备具有相同的规格,但以不同的方式呈现,虽然这可能会造成混淆,但很容易解释。

LTC2493 时序规格表从固件设计人员的角度代表数据,准确地告诉设计人员要做什么。例如,重复启动条件的建立时间被指定为至少 600ns,这意味着主机需要提供一个建立时间至少为 600ns 的脉冲。这是 I2C 规范的副本,用于指导固件工程师信号的时序应该是什么。

另一方面,LTC4261 从 IC 本身的角度表示数据,告诉固件设计人员 IC 本身的能力。例如,重复启动条件的最小建立时间定义为典型值 30ns 和最大值 600n,这意味着 LTC4261 保证最小建立时间不超过 600ns(因此它满足 600ns 所需的最小值规范),实际上它可以识别低至 30ns 的设置时间间隔,从而允许更大的时序余量。

因此,即使它们描述了相同的数据,时序规范也可以以不同的方式呈现。在上述两个示例的情况下,两个部分都符合 I2C 标准并遵守 I2C 时序要求。

本文详细介绍了I2C通信协议的时序规范,包括上升沿和下降沿时间、数据的建立和保持时间、开始和停止条件的时序要求。还探讨了不同I2C速度模式下的数据传输速率和兼容设备必须遵循的时序。以LTC2493和LTC4261为例,展示了设备制造商如何以不同方式表述I2C时序规格,强调了理解这些规范对于确保正确通信的重要性。

本文详细介绍了I2C通信协议的时序规范,包括上升沿和下降沿时间、数据的建立和保持时间、开始和停止条件的时序要求。还探讨了不同I2C速度模式下的数据传输速率和兼容设备必须遵循的时序。以LTC2493和LTC4261为例,展示了设备制造商如何以不同方式表述I2C时序规格,强调了理解这些规范对于确保正确通信的重要性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?