引言:本文详细介绍7 Series Intergrated Block for PCI ExpressPCIe硬核IP接口功能描述

及PCIe配置空间相关内容。

1. 概述

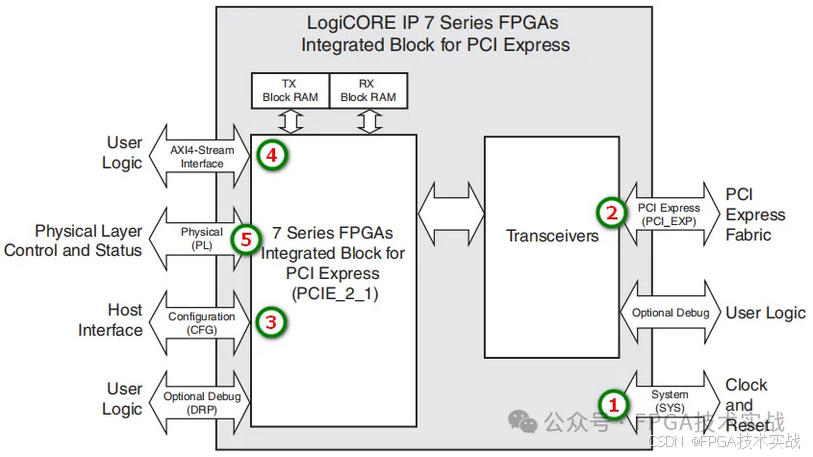

图1:7 Series Intergrated Block for PCI Express核框图

图1显示了PCIe硬核的顶层接口:

①系统(SYS)接口;

②PCI Express(PCI_EXP)接口;

③配置(CFG)接口;

④事务层接口(AXI4流);

⑤物理层控制和状态(PL)接口。

2.PCIe硬核接口

2.1 系统(SYS)接口信号

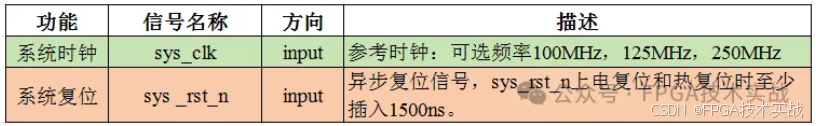

系统(SYS)接口由系统复位信号(sys_rst_n)和系统时钟信(sys_clk)组成,如表1所示。sys_rst_n的断言会导致整个内核的硬重置。系统复位信号为3.3V信号,系统输入时钟必须为100 MHz、125 MHz或250 MHz。

表1:系统接口描述

2.2 PCIe ( PCI_EXP)接口信号

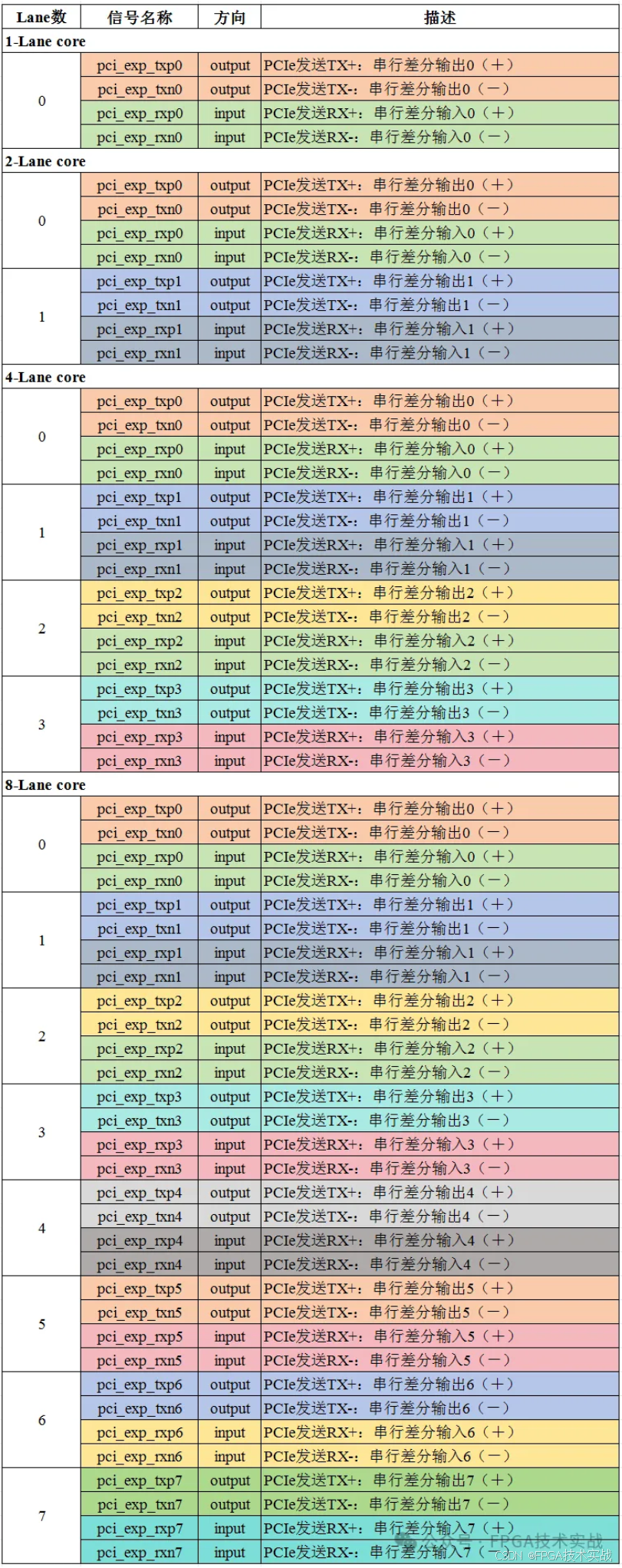

PCIe接口由多通道差分发送和接收对组成。一个PCIe通道(lane)由一对发送差分信号(pci_exp_txp,pci_exp_txn)和一对接收差分信号组成。1-lane core仅支持Lane0,2-lane core仅支持Lane0~1,4-lane core仅支持Lane0~3 ,8-lane core仅支持Lane0~7。PCI_EXP接口的发送和接收信号如表2所示。

表2:PCI EXP接口的发送和接收信号描述

2.3 事务(Transaction)接口

事务接口为用户设计提供了一种生成和使用事务层数据包(TLP)的机制。该接口的信号

名称和信号描述如表3、5、6所示。

2.3.1 公共接口

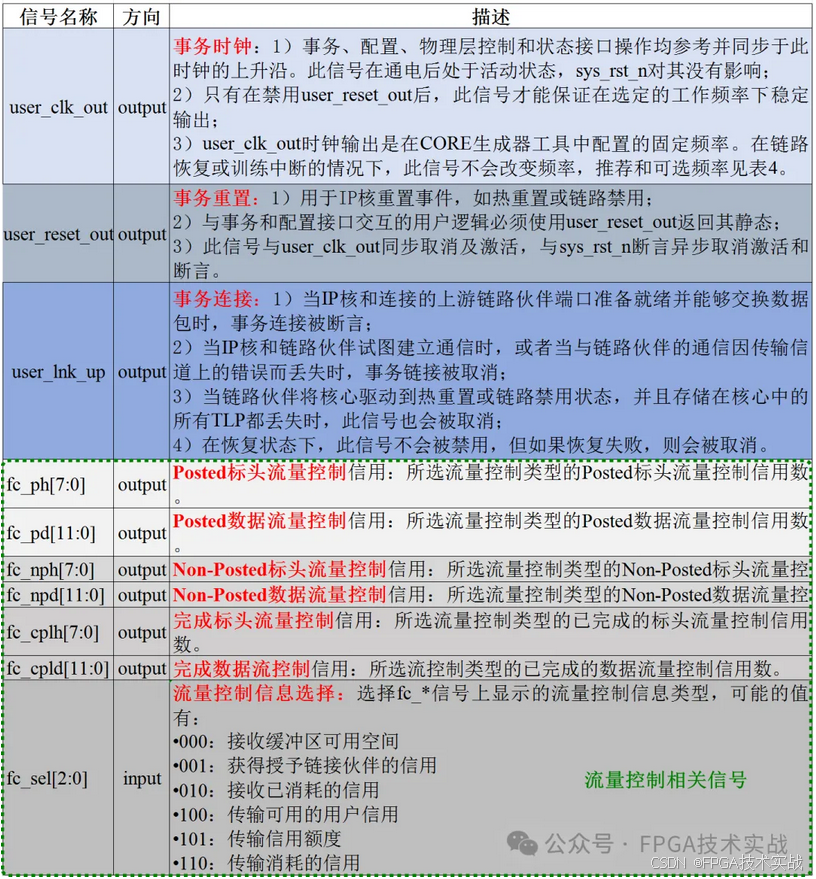

公共信号接口描述如表3所示。

表3:公共信号接口描述

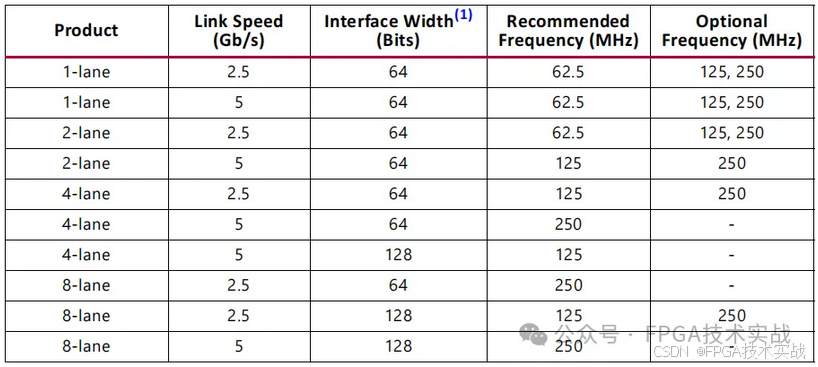

表4:推荐的和可选的事务时钟user_clk_out频率

注意:

1.接口宽度是静态选择,不会随着动态链路速度的变化而变化。

2.对于XC7Z015、XC7Z015I和XC7Z012S器件,250MHz的选项已被删除,因为它不符合时序要求。

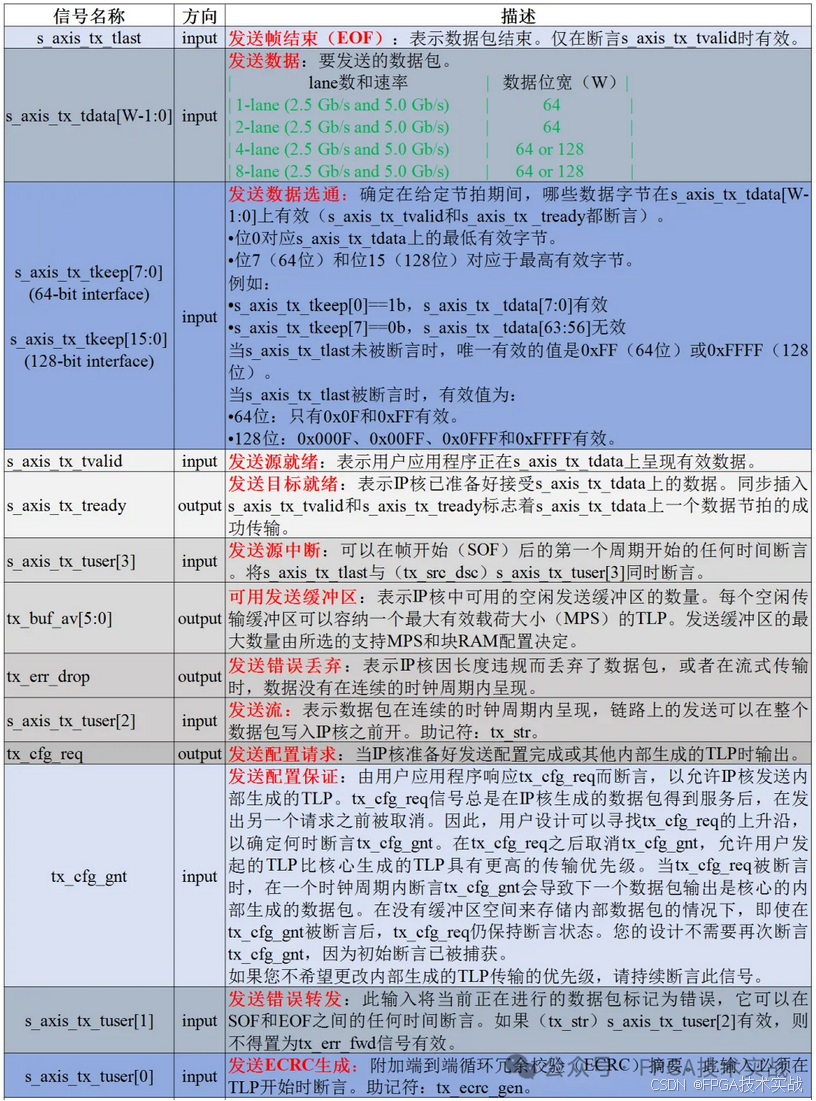

2.3.2 发送(TX) 接口信号

表5定义了发送(TX)接口信号。总线s_axis_tx_tuser由无关的信号组成。本文档中使用了助记符和TSUSER 信号。例如,发送源中断信号被 引用为:( tsrc_dsc) s_axis_tx_tuser[3]。

表5:发送接口信号

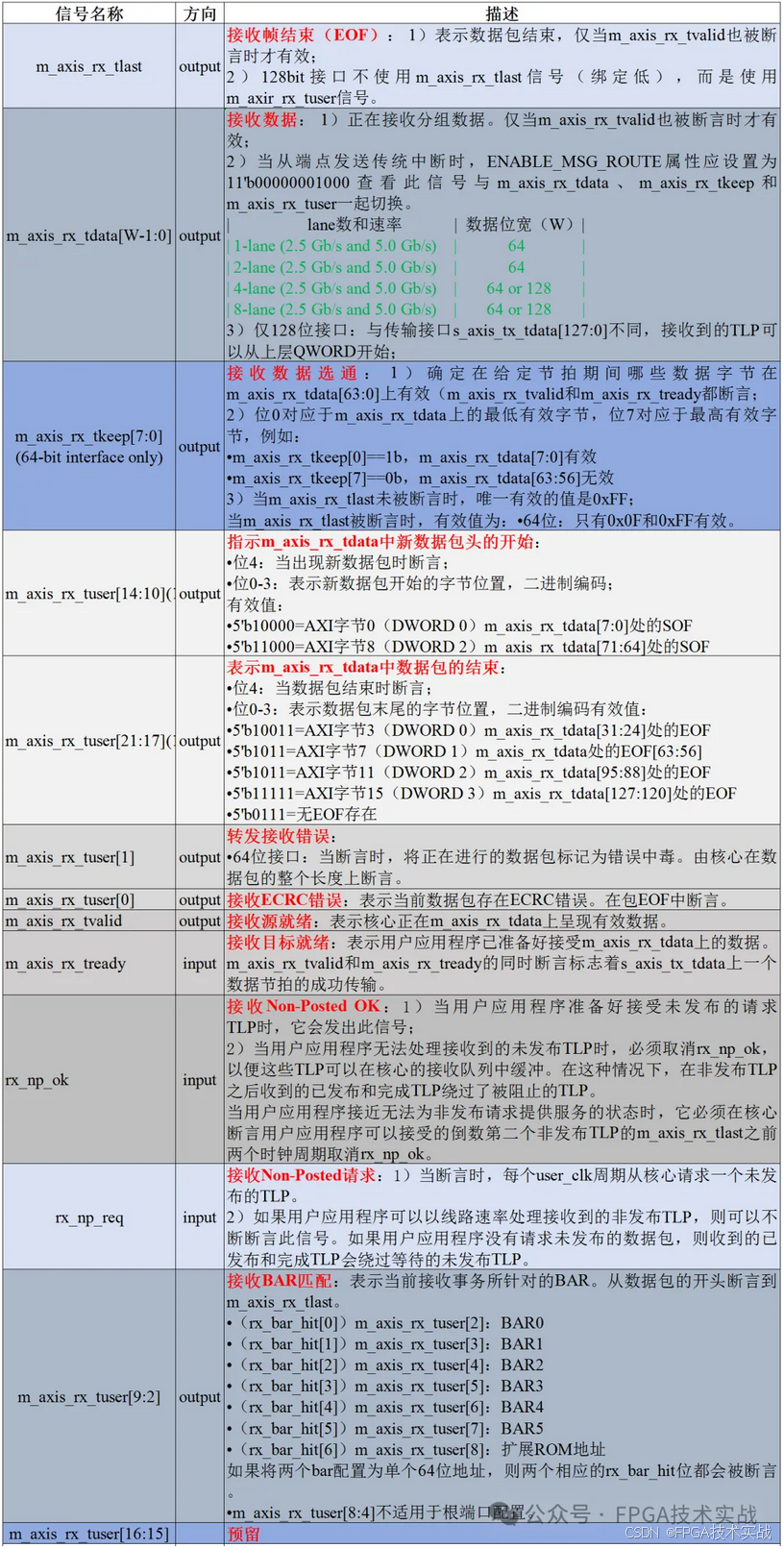

2.3.3 发送(RX)接口信号

表6定义了接收(RX)接口信号。总线m_axis_rx_tuser由不相关的信号组成。本文档中使用这些信号的助记符来代替TUSER信号名称。

表6:接收接口信号

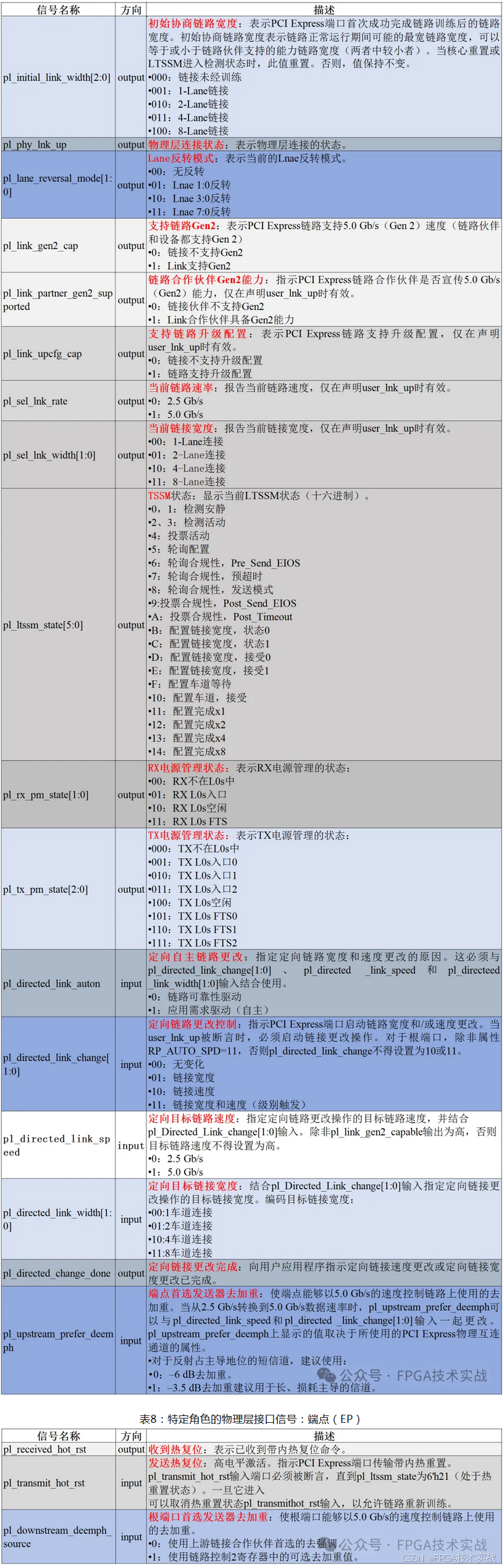

2.3.4 物理层接口信号

物理层(PL)界面使用户设计能够检查链路和链路伙伴的状态并控制链路状态。表7描述了PL接口的信号。

表7:物理层接口信号

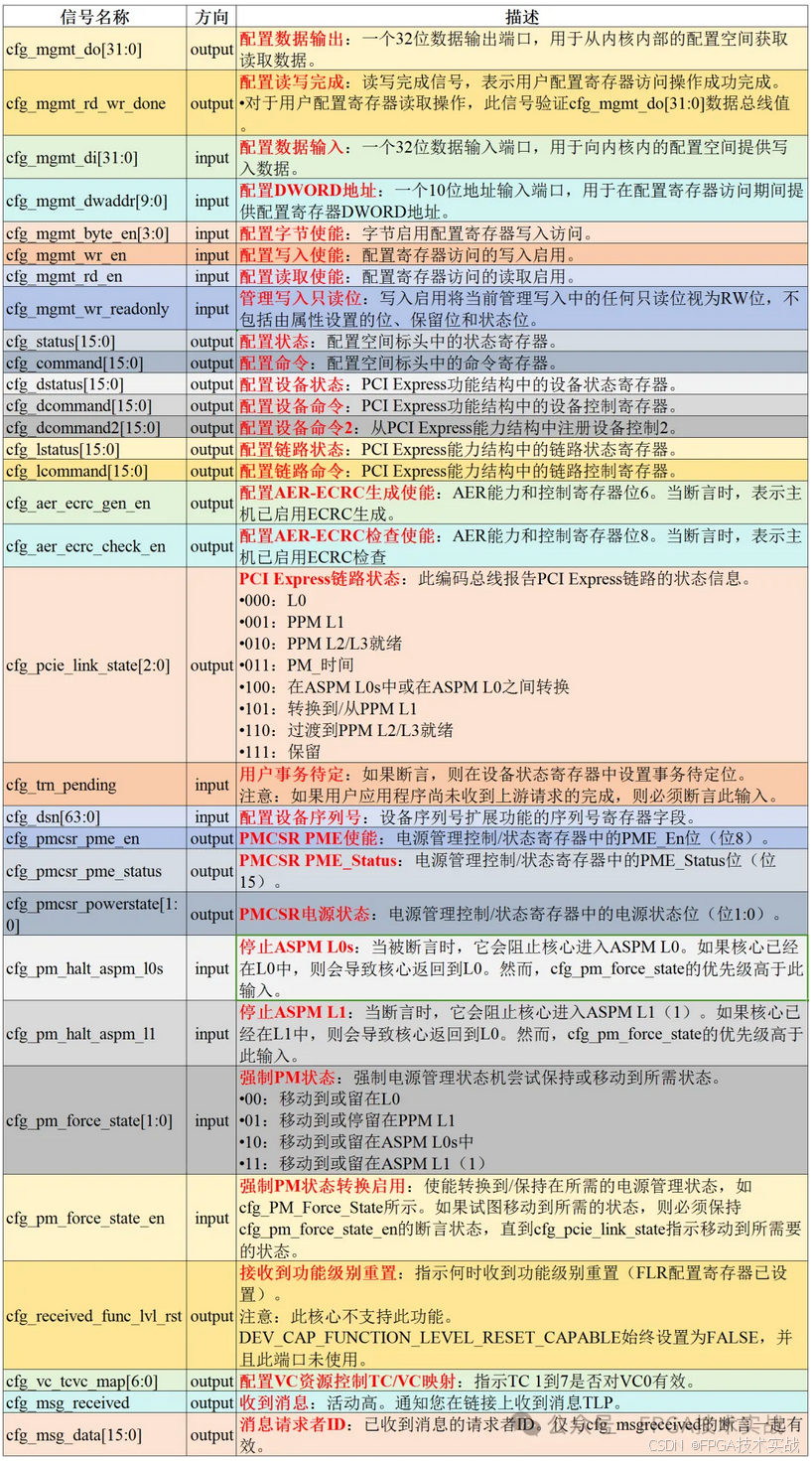

2.3.5 配置接口信号

配置(CFG ) 接口使用户设计能够检查PCIe配置空间端点的状态。用户设计提供了一个10位配置地址,用于选择1024个配置空间双字(DWORD)寄存器中的一个。端点通过32位数据输出端口返回所选寄存器的状态。表9定义了配置接口信号。

表9:配置接口信号

表10:角色特定配置接口信号:根端口

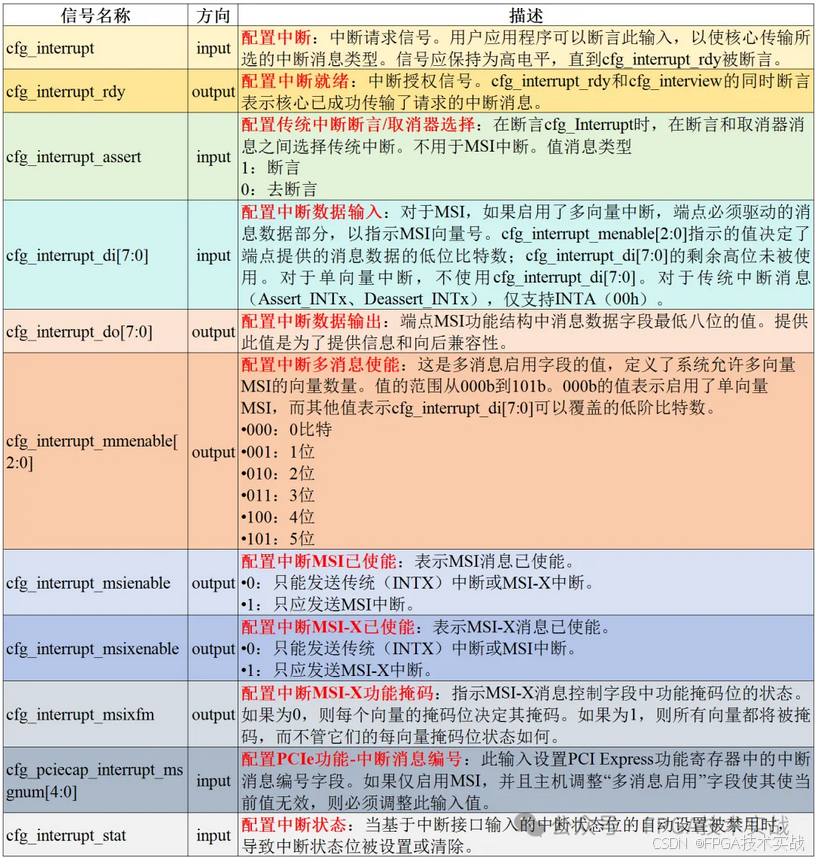

2.3.6 中断接口信号

表11:配置接口信号:中断接口-仅限端点

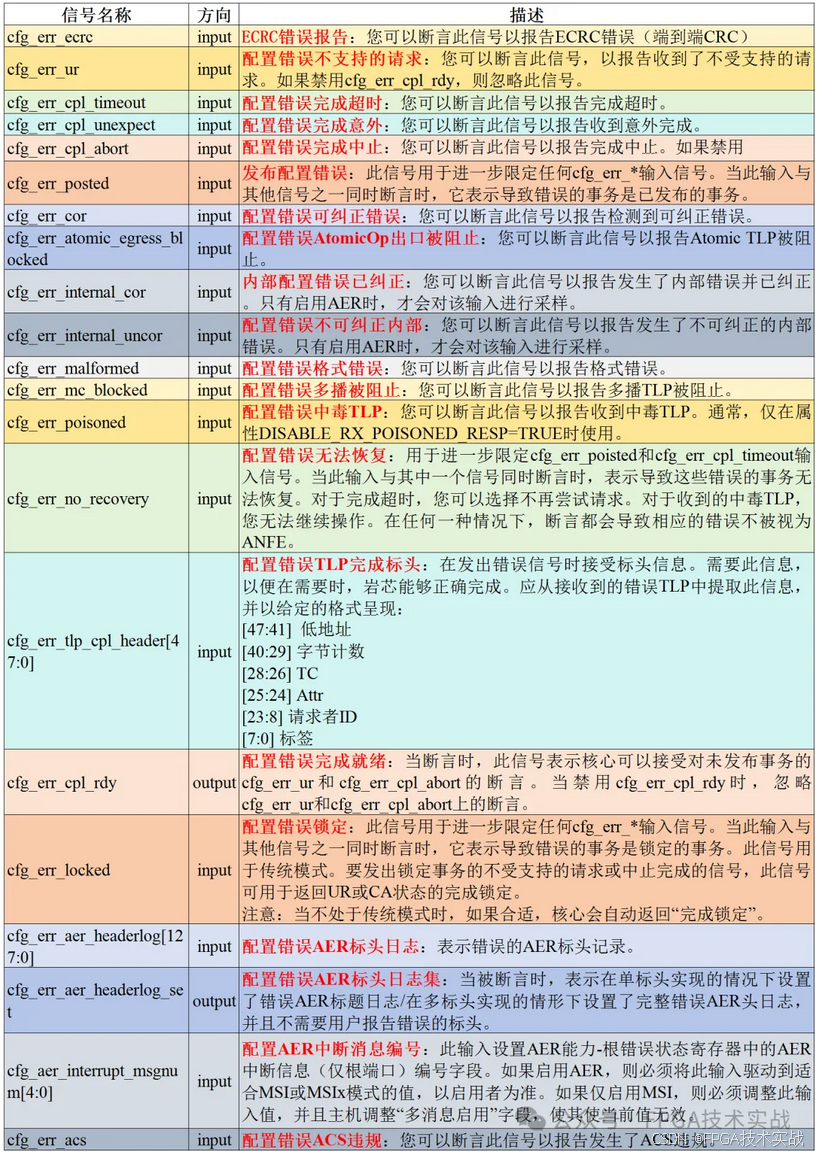

2.3.7 错误报告信号

表12:用户应用程序错误报告信号

表13定义了配置为根端口时PCIe IP核的错误和高级错误报告状态。

表13:错误报告界面-仅根端口

2.3.8 动态重新配置端口接口

动态重新配置端口(DRP)接口允许动态更改PCIe核心FPGA配置存储位。这些配置位表示为PCIE_2_1库原语的属性,该库原语作为此核心的一部分被实例化。表14定义了DRP接口信号。

表14:动态重新配置接口

2.3.9 内部接口

表15显示了IP核内部接口信号。

表15:内部端口接口信号

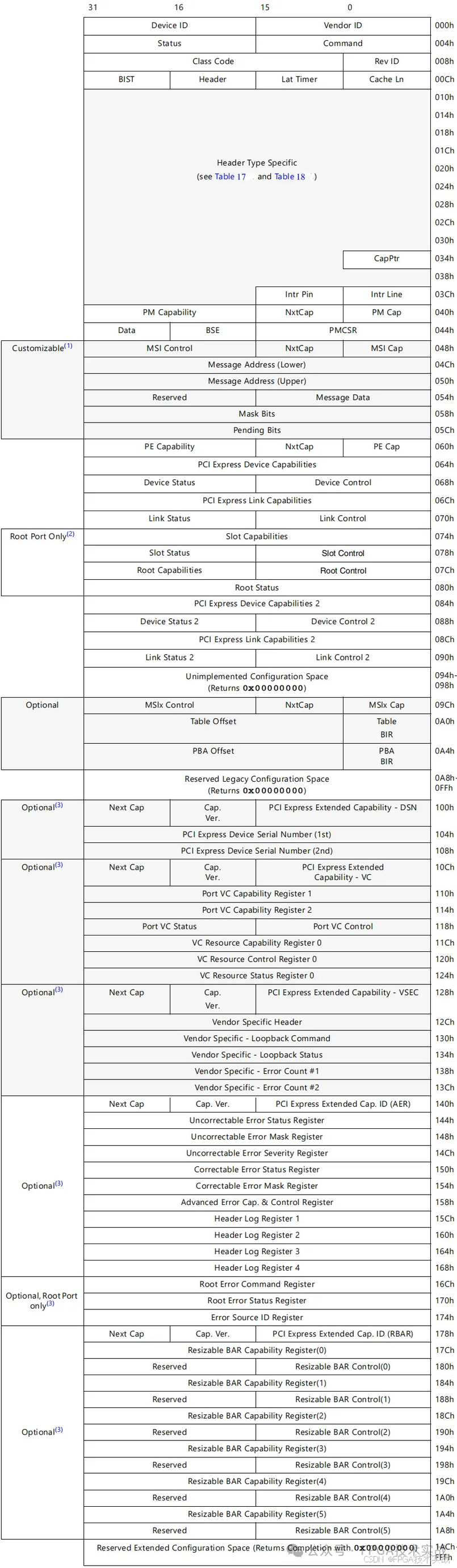

3. PCI配置空间

PCI配置空间由三个主要部分组成,如表16所示。

表16:通用PCI配置空间标头

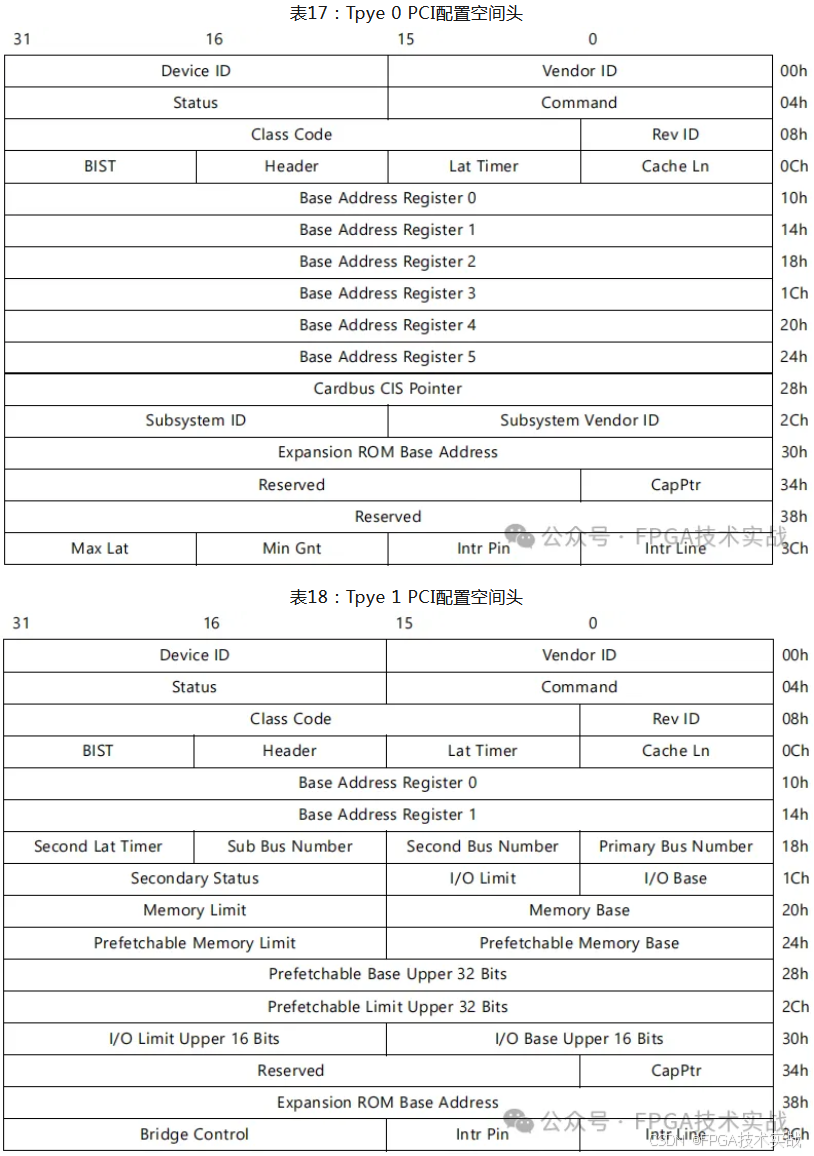

●传统PCIv3.0 Tpye 0/1配置空间标头

o 端点应用程序使用的Tpye 0配置空间标头(见表17)

o 根端口应用程序使用的Tpye 1配置空间标头(见表18)

●传统扩展功能项

o PCIe功能项

o 电源管理能力

o 消息信号中断(MSI)

o MSI-X能力项(可选)

●PCIe扩展功能

o 设备序列号扩展功能(可选)

o 虚拟通道扩展能力(可选)

o 供应商特定的扩展能力(可选)

o 高级错误报告扩展功能(可选)

o 可调整大小的BAR扩展能力(可选)

表17:Tpye 0 PCI配置空间头

IP核实现了四个传统扩展功能项。从地址0xA8到0xFF的剩余传统扩展功能空间是保留的或用户可定义的(仅限端点配置)。此外,保留了未实现的任何可选功能结构的位置。如果不使用此空间,则读取此地址范围时,IP核将返回0x00000000。如果在0xA8到0xFF范围内的用户可定义位置内实现寄存器,则必须在用户应用程序中实现此空间。您还负责为此范围内未在用户应用程序中实现的任何地址返回0x00000000。

重要提示:内核可选择实现多达三个PCIe扩展功能。剩余的PCI Express扩展功能空间可供实施。

可用空间的起始地址取决于实现了五个可选PCIe扩展功能中的哪一个(如果有的话)。如果在此空间中实现寄存器,则可以选择此空间的起始位置,并且此空间必须在用户应用程序中实现。

1045

1045

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?