问题起因:

在设计完ZYNQ(XCZU9CG)后,拿到板子进行测试时ibert时发现测试过程中的PLL没有lock住。

排查过程:

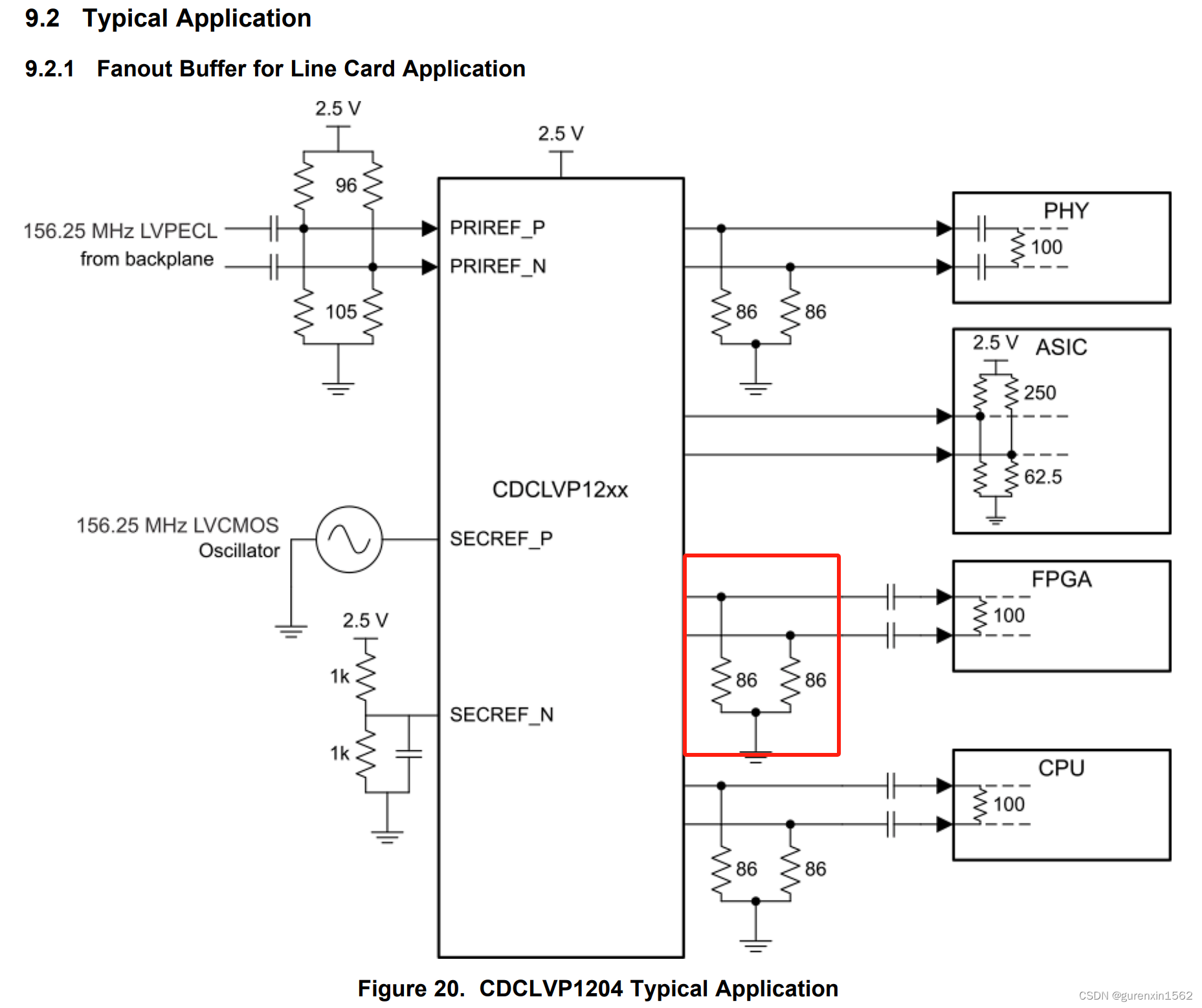

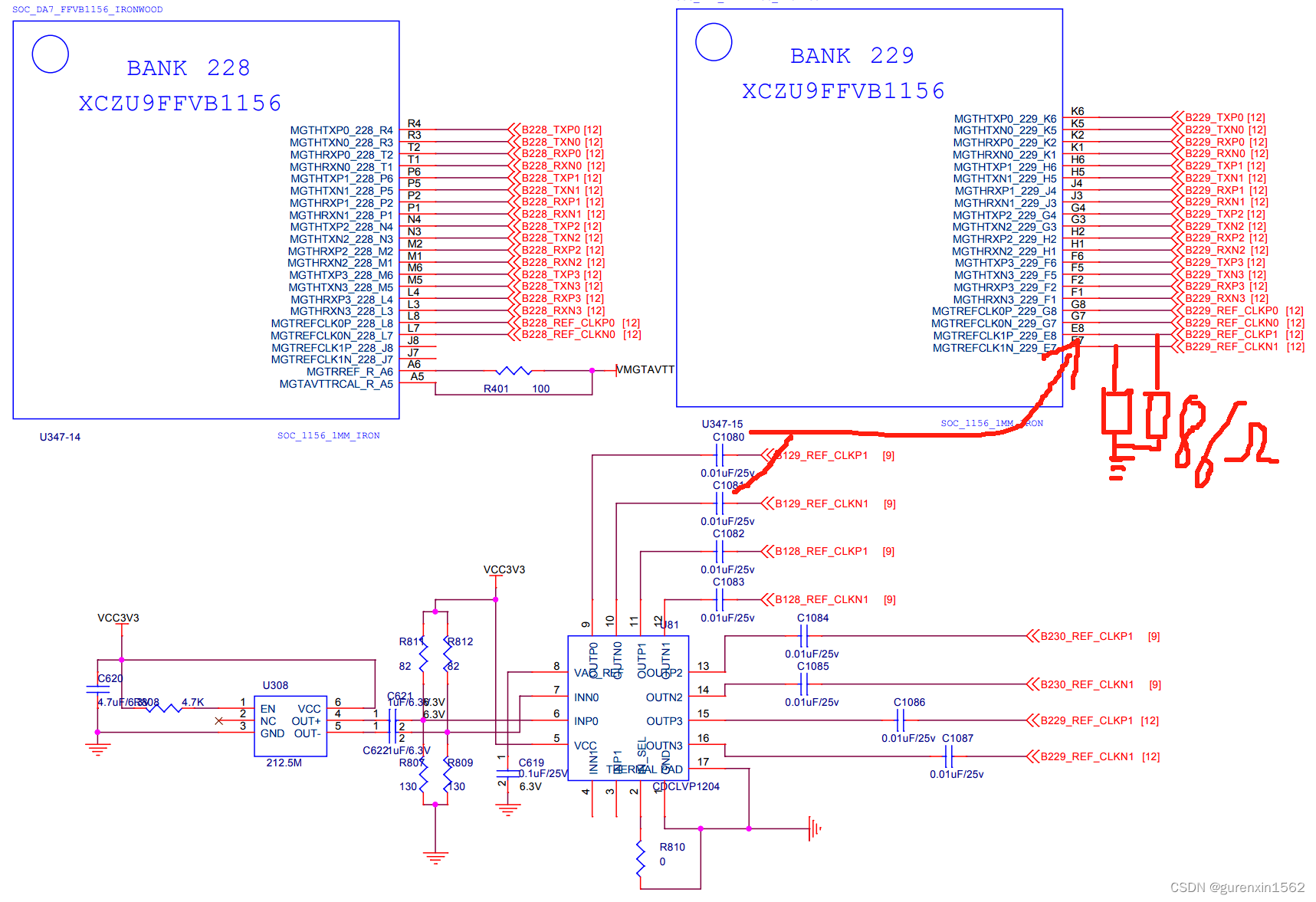

先排查晶振本身问题,经过示波器查看波形后发现晶振并未起振,检查晶振的电压没有问题,在更换芯片后再次测试晶振起振波形正常(幅度有点低)。随后再次测试ibert还是同样的问题,继续排查,时钟经过时钟分路器(缓冲器)后AC耦合接到FPGA中GTH端,在电容端测试发现四路输出无波形,看了眼器件手册,发现在FPGA端本应加的下拉电阻并没有接上。随后在电容一侧到地之间飞了两颗电阻解决问题,ibert测试正常。

问题总结 :

所以我们还需要再理解一下手册与原理。

之前打开器件手册发现差分晶振有这么几种信号类型。

查找关于这几类信号的知识,原文链接如下:

差分晶振_LVDS/LVPECL/HCSL/CML模式-CSDN博客![]() https://blog.csdn.net/dobypig/article/details/120694338?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522169951551716800182716261%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=169951551716800182716261&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~sobaiduend~default-1-120694338-null-null.142^v96^pc_search_result_base4&utm_term=%E5%B7%AE%E5%88%86%E6%99%B6%E6%8C%AF&spm=1018.2226.3001.4187(77 封私信 / 80 条消息) 什么是PECL电平 - 知乎 (zhihu.com)

https://blog.csdn.net/dobypig/article/details/120694338?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522169951551716800182716261%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=169951551716800182716261&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~sobaiduend~default-1-120694338-null-null.142^v96^pc_search_result_base4&utm_term=%E5%B7%AE%E5%88%86%E6%99%B6%E6%8C%AF&spm=1018.2226.3001.4187(77 封私信 / 80 条消息) 什么是PECL电平 - 知乎 (zhihu.com)![]() https://www.zhihu.com/zvideo/1428310610869813248?playTime=172.0

https://www.zhihu.com/zvideo/1428310610869813248?playTime=172.0

我就不全复制过来了,里面有解释关于差分晶振与PECL电平的详细内容,方便我们日后查看。

3966

3966

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?