Serdes系列总结——Xilinx ibert IP使用

最新推荐文章于 2024-08-13 17:26:54 发布

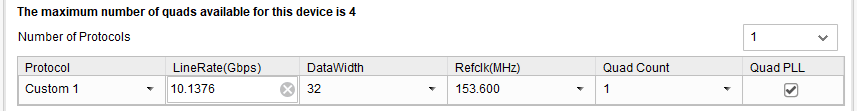

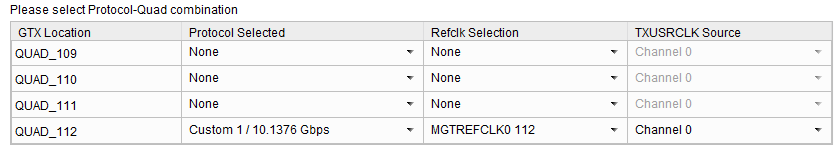

本文详细介绍了如何在FPGA中使用Xilinx Ibert IP进行配置,包括IP设置、测试界面操作和眼图质量评判标准。重点讲解了DataWidth、RXOUTCLK的设置,以及在不同场景下的测试步骤,确保串行通信的优化。同时,给出了眼图质量评估的关键指标,如眼高、眼宽和BER要求。

本文详细介绍了如何在FPGA中使用Xilinx Ibert IP进行配置,包括IP设置、测试界面操作和眼图质量评判标准。重点讲解了DataWidth、RXOUTCLK的设置,以及在不同场景下的测试步骤,确保串行通信的优化。同时,给出了眼图质量评估的关键指标,如眼高、眼宽和BER要求。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?