提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

下面记录一下modelsim功能仿真和时序仿真的操作步骤,学习新器件的第一步,当然是要知道怎么进行IP核的仿真了。下面就以高云IP库中 Gowin_Uart_to_Bus_RefDesign的参考设计来举例说明

下载地址:

http://www.gowinsemi.com.cn/enrollment_view.aspx?TypeId=67&Id=953&FId=t27:67:27

功能仿真

功能仿真包括综合前的用户RTL 设计功能仿真和综合后逻辑网表功能仿真,所需要的文件有:综合前用户设计RTL 文件、综合后网表文件(*.vg)、激励文件(testbench)*tb.v 以及功能仿真库文件prim_sim.v。

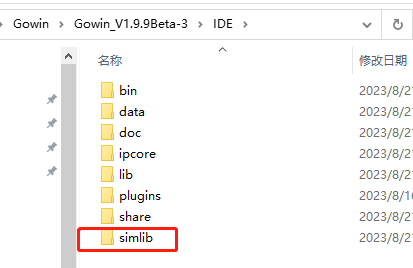

功能仿真prim_sim.v文件都在这个simlib文件夹里面了,根据使用的器件选择prim_sim.v就是。

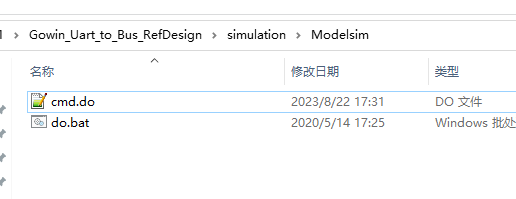

高云IP的参考设计都做得比较贴心,在参考设计中

直接点击do.bat就能自动调用modelsim进行功能仿真了

cmd.do中内容如下:

## part 1: new lib

vlib work

vmap work work

## part 2: load design

vlog -novopt -incr -work work "../../tb/prim_sim.v"

vlog -novopt -incr -work work "../../tb/tb_top.v"

vlog -novopt -incr -work work "../../project/src/top.v"

vlog -novopt -incr -work work "../../project/src/apb2local.v"

vlog -novopt -incr -work work "../../project/src/local2reg.v"

vlog -novopt -incr -work work "../../project/src/uart_to_bus/uart_to_bus.vo"

## part 3: sim design

vsim -novopt work.tb_top

## part 4: add signals

add wave -group "tb_top" {sim:/tb_top/*}

## part 5: show ui

view wave

view structure

view signals

## part 6: run

run 160000000ns

时序仿真(后仿真)

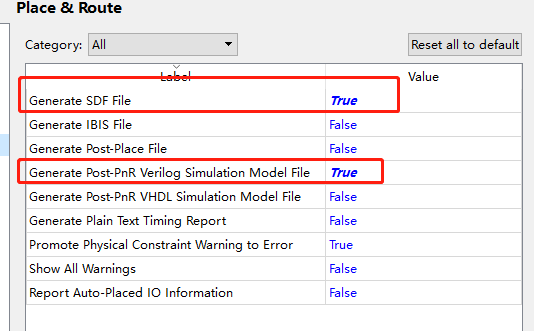

时序仿真需要的文件:软件产生的时序仿真逻辑网表文件*.vo、对应的延时文件*.sdf、对应的激励文件tb.v 以及时序仿真库prim_tsim.v。注意,这里是时序仿真库哦!!!这个库也在那个simlib文件夹里面。

时序仿真逻辑网表文件.vo 和延时文件*.sdf 可以通过云源界面运行工程生成

编译完成之后,project\impl\pnr文件夹中会有一个uart_to_bus_demo.vo 文件和uart_to_bus_demo.fs文件。

然后将do文件中脚本如下设置。因为现在的IDE,GW5AT还没有提供prim_tsim.v文件,这里先把器件改成了GW2A的。注意do文件中和上面功能仿真时do文件的差异。

## part 1: new lib

vlib work

vmap work work

## part 2: load design

#vlog -novopt -incr -work work "../../tb/simlib/gw2a/prim_sim.v"

vlog -novopt -incr -work work "../../tb/simlib/gw2a/prim_tsim.v"

vlog -novopt -incr -work work "../../tb/tb_top.v"

#vlog -novopt -incr -work work "../../project/src/top.v"

#vlog -novopt -incr -work work "../../project/src/apb2local.v"

#vlog -novopt -incr -work work "../../project/src/local2reg.v"

#vlog -novopt -incr -work work "../../project/src/uart_to_bus/uart_to_bus.vo"

vlog -novopt -incr -work work "../../project/impl/pnr/uart_to_bus_demo.vo"

## part 3: sim design

vsim -novopt -gui work.tb_top -sdfnoerror -sdfnowarn -sdftyp "tb_top/u_top=../../project/impl/pnr/uart_to_bus_demo.sdf"

## part 4: add signals

add wave -group "tb_top" {sim:/tb_top/u_top/*}

## part 5: show ui

view wave

view structure

view signals

## part 6: run

run 160000000ns

特别要注意这句话:

vsim -novopt -gui work.tb_top -sdfnoerror -sdfnowarn -sdftyp “tb_top/u_top=…/…/project/impl/pnr/uart_to_bus_demo.sdf”

这里tb_top/u_top都是代码中的例化名,而不是模块名或者文件名

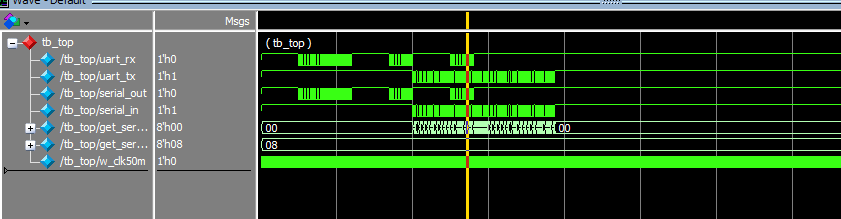

改完之后,点击do.bat。时序仿真明显变慢了很多

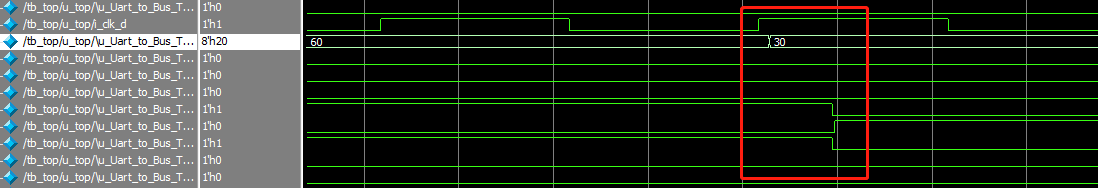

找一些内部信号来看,已经不和时钟上升沿对齐了,说明sdf中的延迟信息生效了

本文详细介绍了如何在GowinFPGA的modelsim中进行用户RTL设计的功能仿真和综合后的逻辑网表功能仿真,以及如何进行时序仿真,包括所需文件、仿真脚本和注意事项。

本文详细介绍了如何在GowinFPGA的modelsim中进行用户RTL设计的功能仿真和综合后的逻辑网表功能仿真,以及如何进行时序仿真,包括所需文件、仿真脚本和注意事项。

2123

2123

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?