本文基于MOOC课《芯动力——硬件加速设计方法》课程整理所得。如有需要,请前往MOOC观看

文章目录

重点提纲——本文核心内容

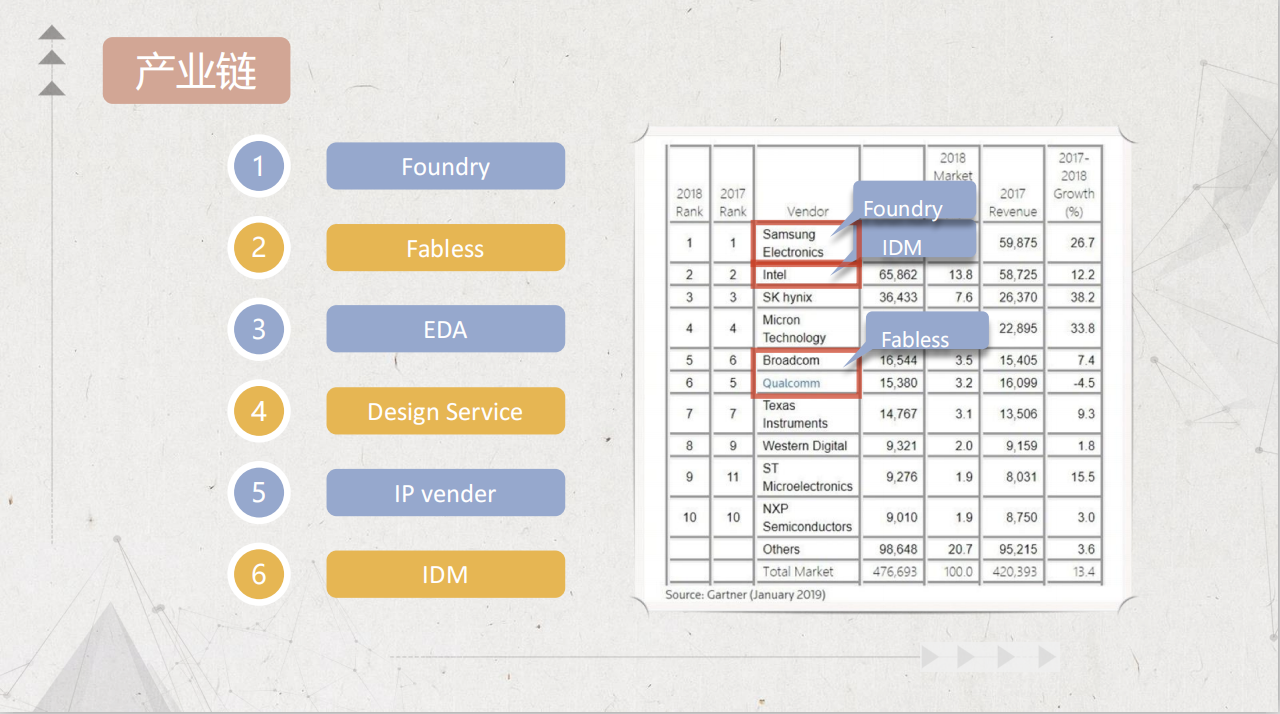

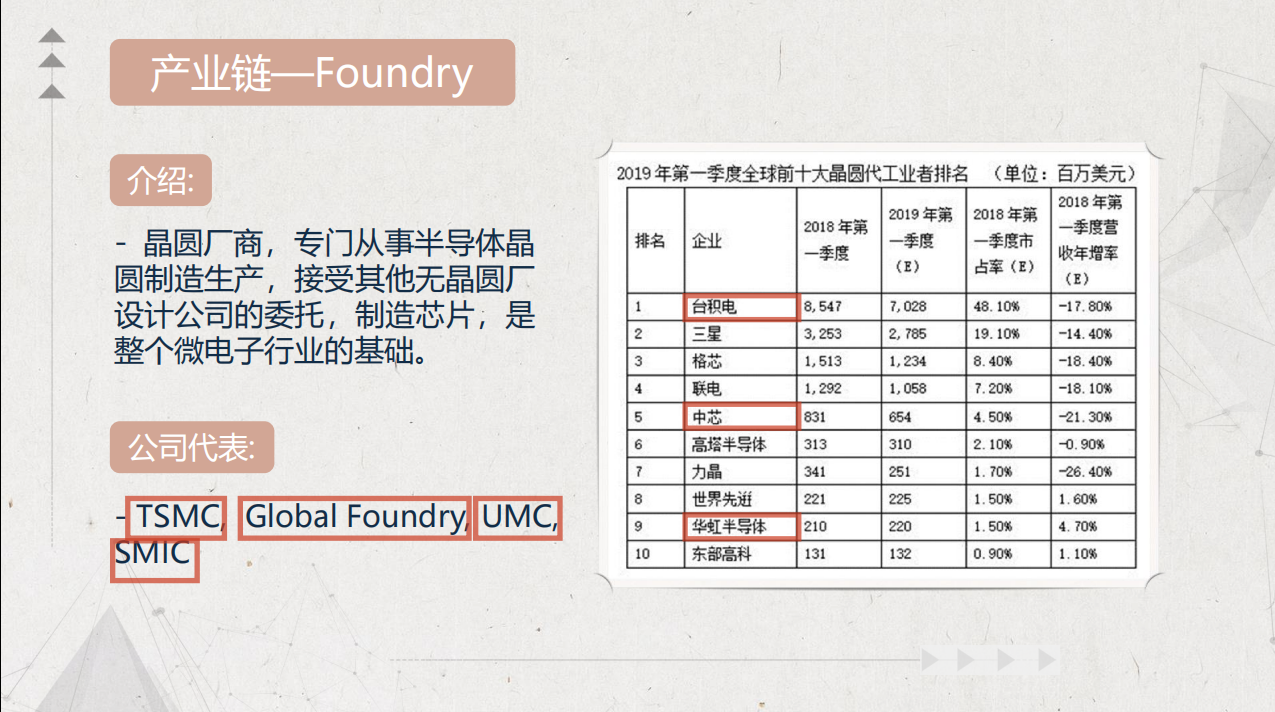

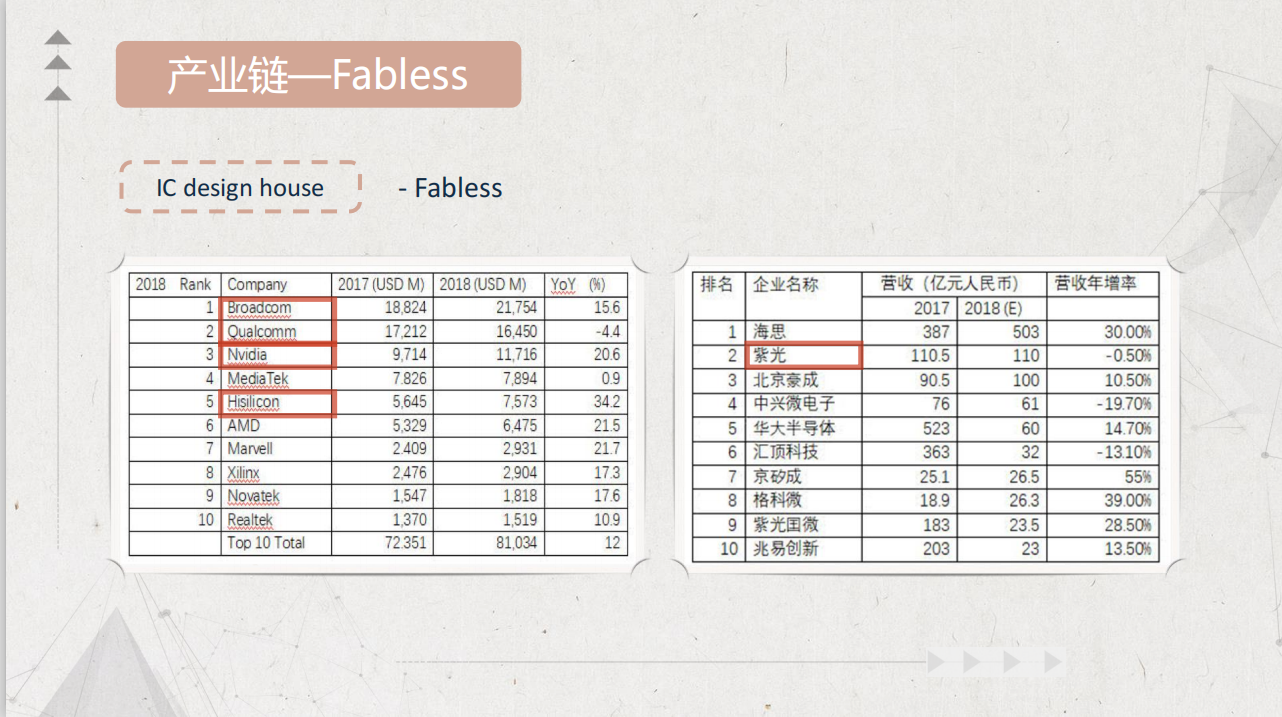

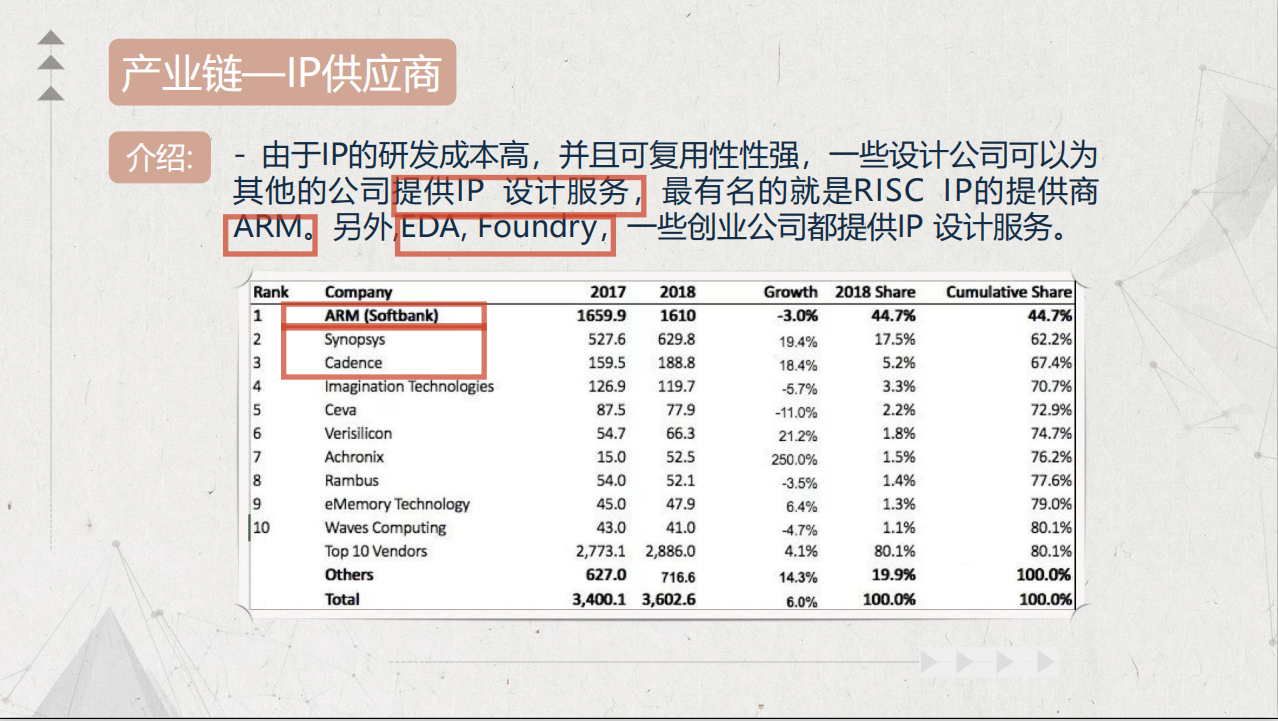

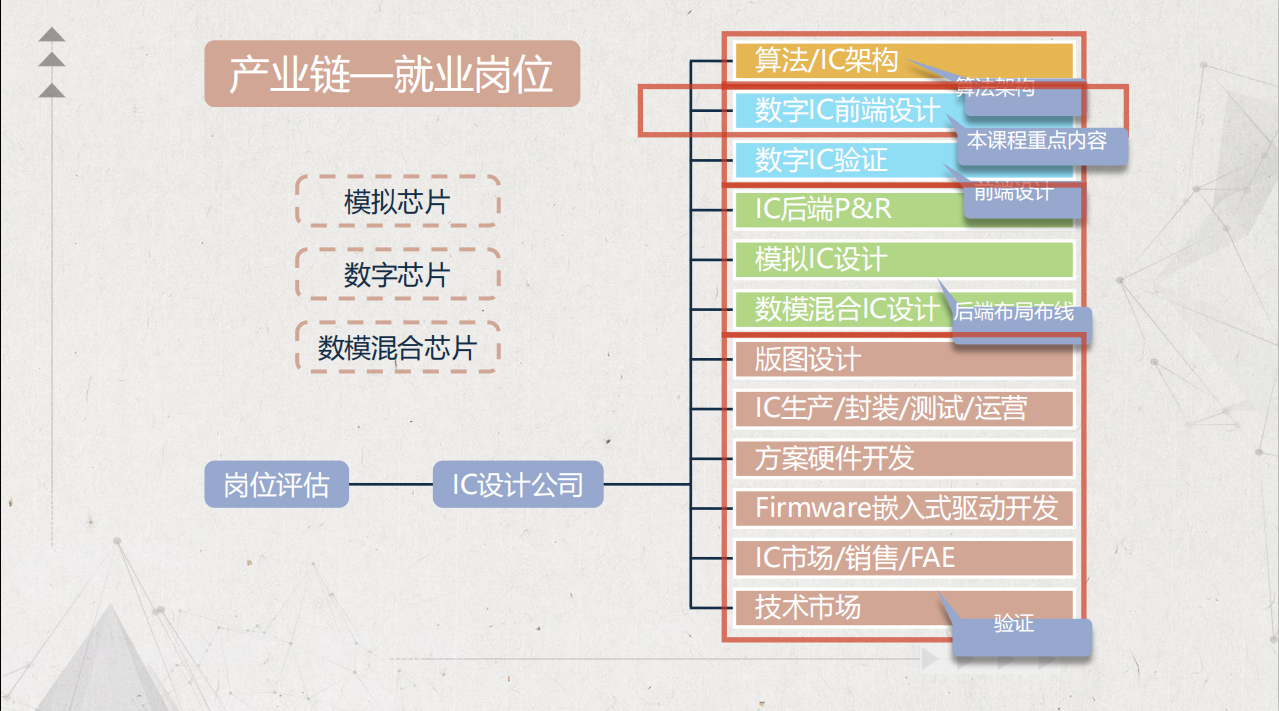

1:芯片设计的产业链主要包括五个环节。晶圆厂 Foundry,无晶圆设计公司 Fabless,EDA软件公司,设计服务公司,IP 供应商,集成设计与制造 IDM。五个环节的典型代表企业有哪些?

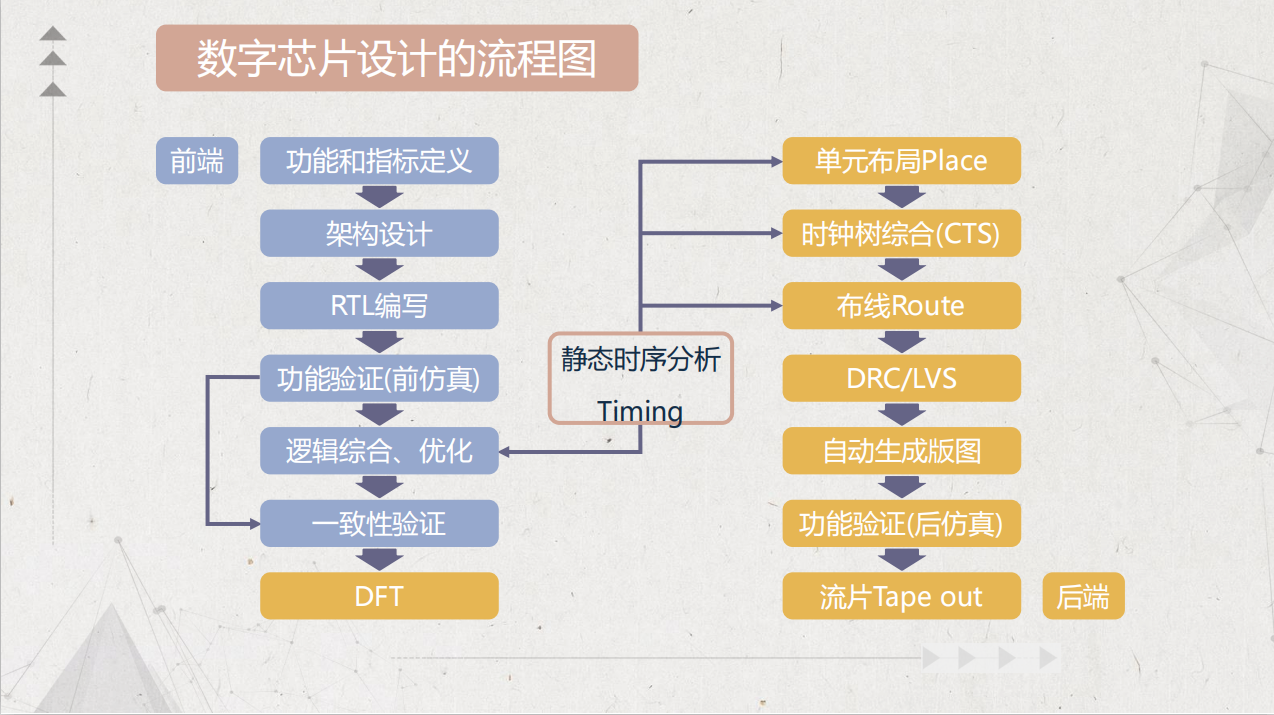

2:数字芯片设计的流程:

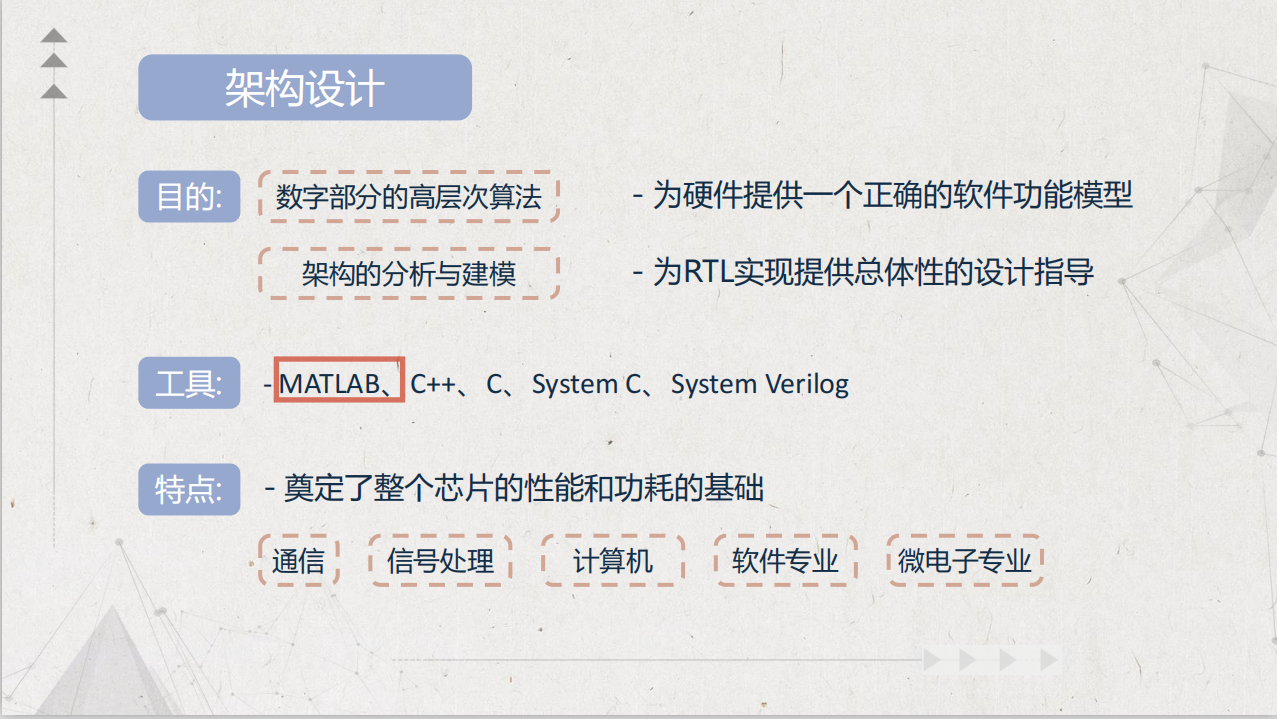

(1)算法或硬件架构设计与分析。

目的:完成芯片中数字部分的高层次算法或架构的分析与建模,为硬件提供一个正确的软件功能模型,更为重要的是,通过大量的高层次仿真和调试,为 RTL 实现提供总体性的设计指导。数字部分越复杂,这一点越重要。

工具:MATLAB、C++、C、System C、System Verilog 等。不同类型的芯片都不同的选择,如数字信号处理类芯片,偏好 MATLAB。

特点:这部分工作至关重要,基本上奠定了整个芯片的性能和功耗的基础。这部分工作主要由具有通信、信号处理、计算机、软件专业背景的工程师完成,也有很多微电子专业背景的工程师参与。

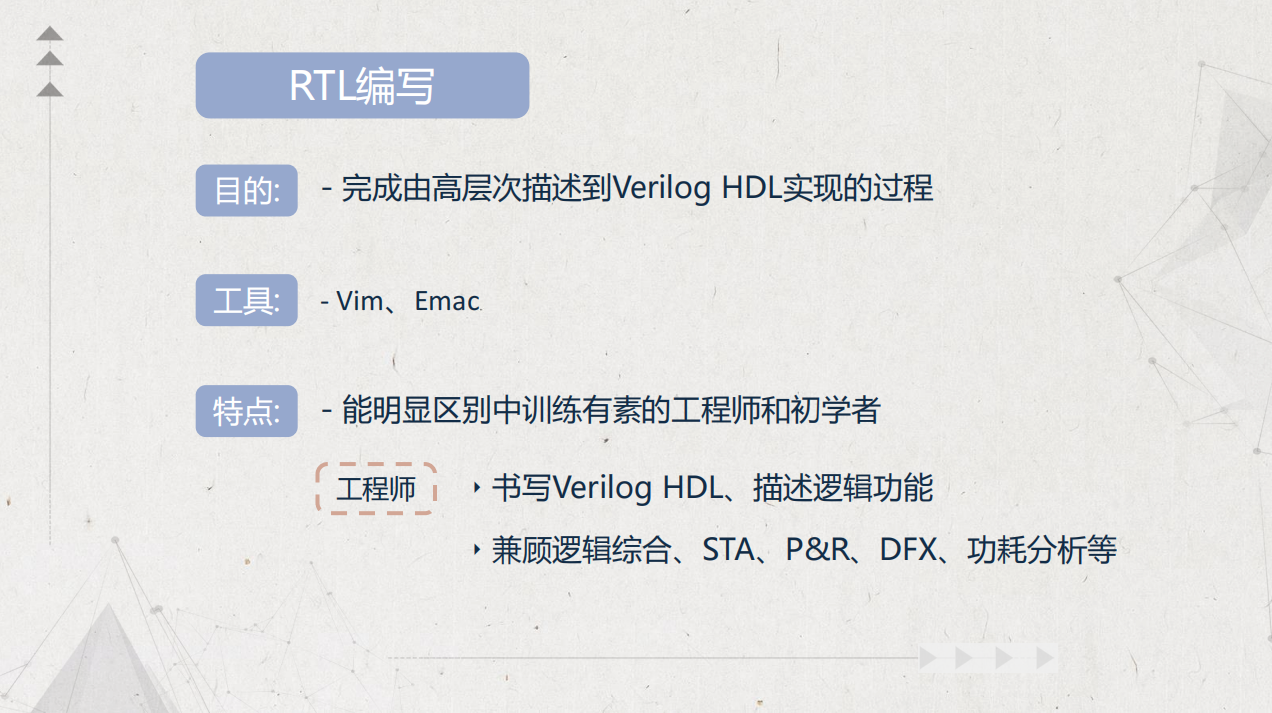

(2)RTL 实现

目的:依据第一步的结果,完成由高层次描述到 Verilog HDL 实现的过程。

工具:Vim、Emac(二者不分前后顺序哦)

特点:这一步能明显区别中训练有素的工程师和初学者。前者在写代码的过程中,具有极强的大局观,能够在书写 Verilog HDL、描述逻辑功能的同时,还能够兼顾逻辑综合、STA、P&R、DFX、功耗分析等多方面因素,最终提供一份另其他环节的工程师都赏心悦目的代码。

初学者则处处留地雷,一不小心就引爆。

(3)功能验证

目的:在无延迟的理想情况在,通过大量的仿真,发现电路设计过程中的人为或者非人为引起的 bug。主要指标是功能覆盖率。

工具:Modelsim、VCS、NC-Verilog

语言:C++、C、System C、System Verilog,基于 UVM 的方法学等。主要是 System Verilog,一般哪个方便用哪个。

特点:验证工程师近年来已经成为 IC 设计中需求量最大的岗位。这个阶段会占用大量的时间,数以月计

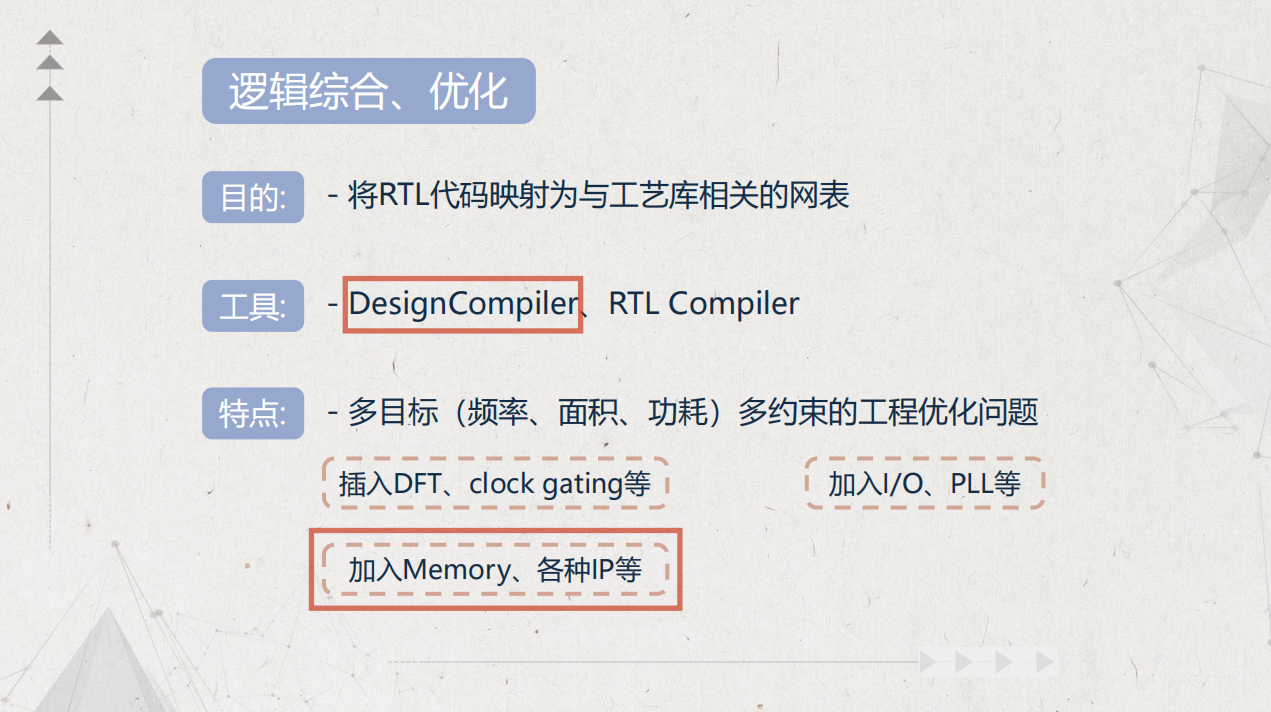

(4)逻辑综合

目的:将 RTL 代码映射为与工艺库相关的网表。

工具:DesignCompiler、RTL Compiler。DesignCompiler 在市场中占有垄断性地位,几乎成为逻辑综合的标准。

特点:从芯片生产的角度来看,在该步骤之前,所有的工作都可近似看做一个虚拟性的,与现实无关。而从逻辑综合起,后续所有的工作都将与工艺的物理特性、电特性等息息相关。逻辑综合工具的功能主要是将 VerilogHDL 格式的文本映射为网表格式的文本,因此,它的功能等同于文本编译器。那么转换的方式有很多种,工具如何选取呢?逻辑综合过程中,整个文本格式的编译过程是在给定的人为约束条件下进行的,通过这些约束和设定的目标来指导工具完成 Compiler 的工作。所以,逻辑综合过程可以看成一个多目标(频率、面积、功耗)多约束的工程优化问题。该步骤中,通常会插入 DFT、clock gating 等。该步骤中通常加入 Memory、各种 IP 等。为了在各种工艺库以及 FPGA 原型验证平台之间有一个更方便的移植,注意适当处理这些 Memory、IP 等的接口。该步骤中也可加入 I/O、PLL 等。

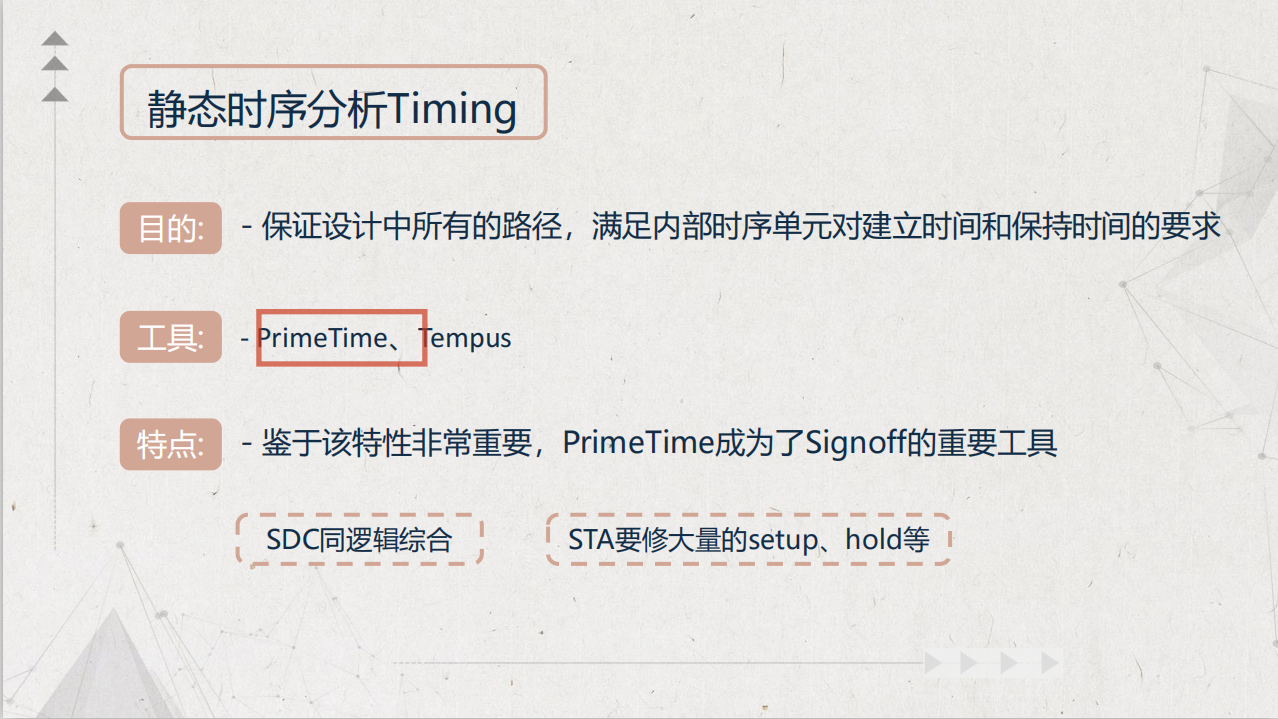

(5)静态时序分析

目的:相对动态仿真的类穷举式验证方法而言,从静态分析的角度,保证设计中所有的路径,满足内部时序单元对建立时间和保持时间的要求。即无论起点是什么,信号都可以被及时地传递到该路径的终点,并且在电路正常工作所必需的时间段内保持恒定。

工具:PrimeTime、Tempus。PrimeTime 在市场中占有垄断性地位,几乎成为 STA 的标准。

特点:从逻辑综合开始,基本上每做一步大的调整,都会完成一次 STA 分析,以保证每步都能实现时序收敛。鉴于该特性非常重要,PrimeTime 成为了 Signoff 的重要工具。所用到的SDC 同逻辑综合;通常设计中会存在大量的违例路径,STA 要修大量的 setup、hold 等,如何修这些违例,可以体现工作经验的重要性。此外,如果是前端修 timing 违例,一般会修的很快,但是会带来一个重大的问题,代码被前端修改后是否存在新的 bug,还需重新仿真确认,仿真会消耗掉数以月计的时间,所以除非万不得已,不会找前端修 timing。

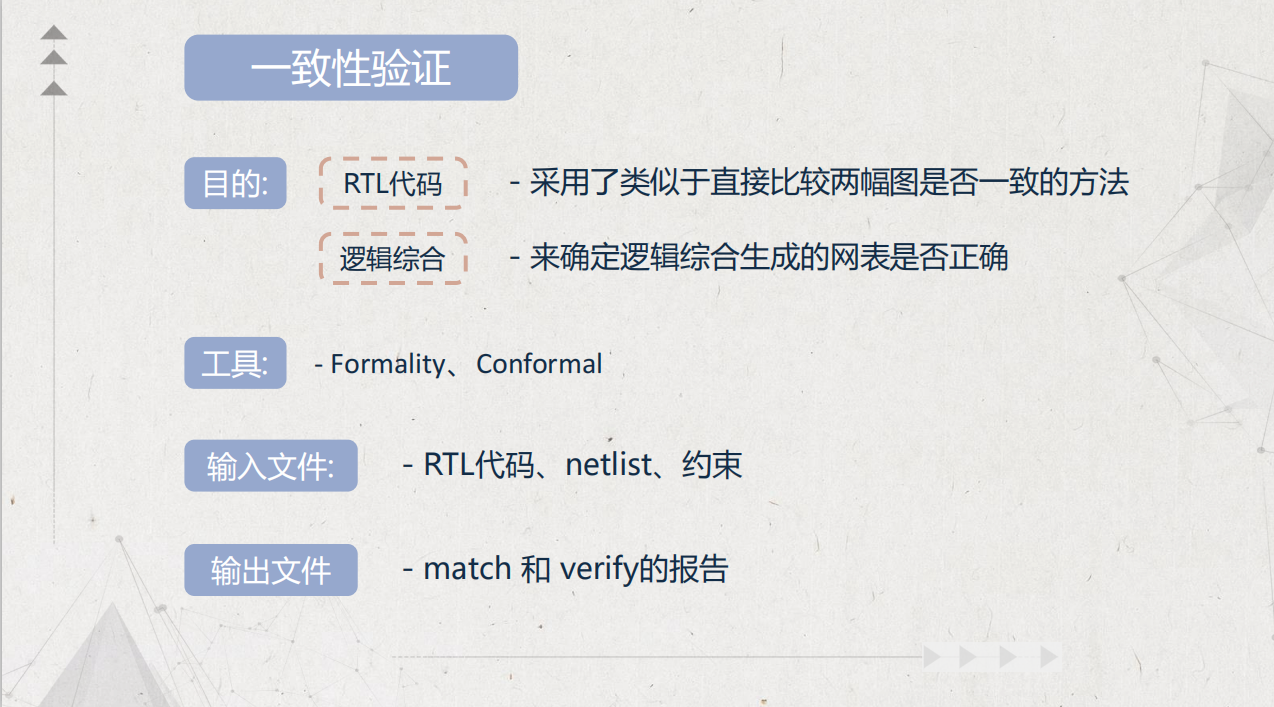

(6)一致性验证

目的:RTL 代码和逻辑综合后的网表都可以抽象为两幅由节点和边构成的图,一致性验证阶段采用了类似于直接比较两幅图是否一致的方法,来确定逻辑综合生成的网表是否正确。

工具:Formality、Conformal

输入文件:RTL 代码、netlist(逻辑综合输出)、约束

输出文件:match(两张图节点是否一致)和 verify(计算得出两张图功能是否一致)的报告。

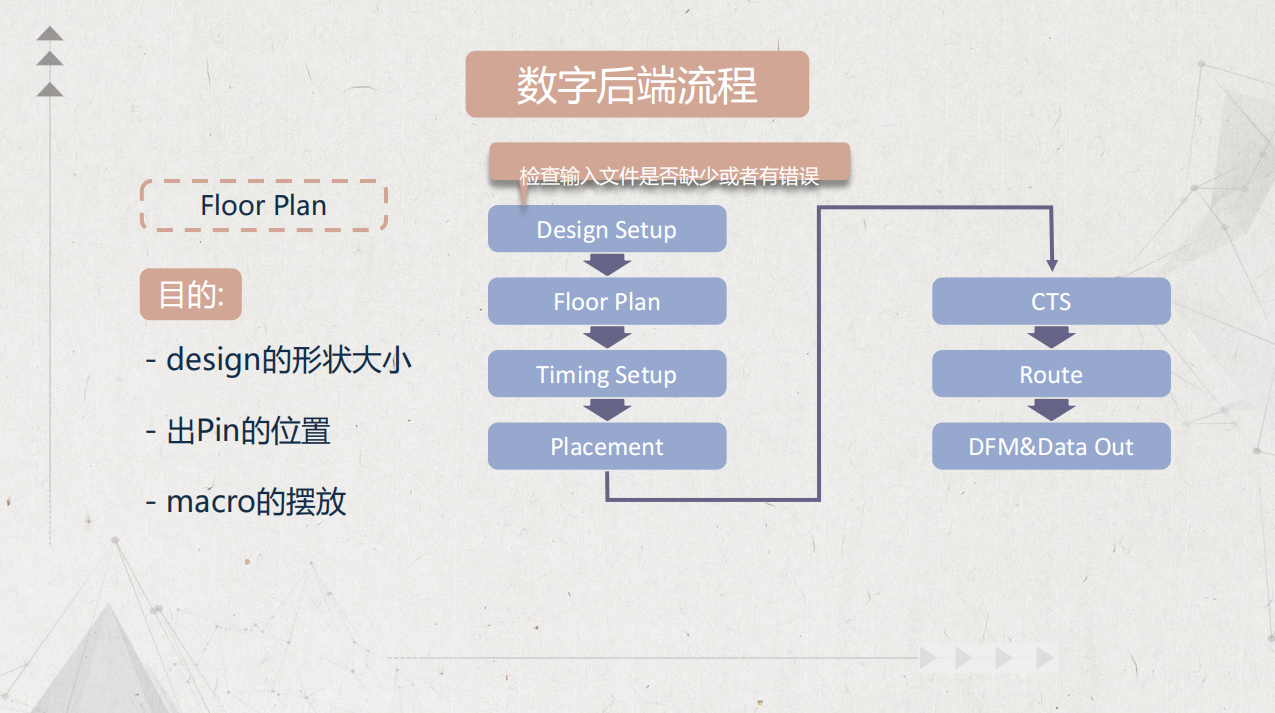

(7)数字后端流程

数字后端设计又称物理设计,将网标格式的文本转化成一个个有物理大小和位置的单元、连线。并且在实现过程中要满足面积、功耗、性能等要求。

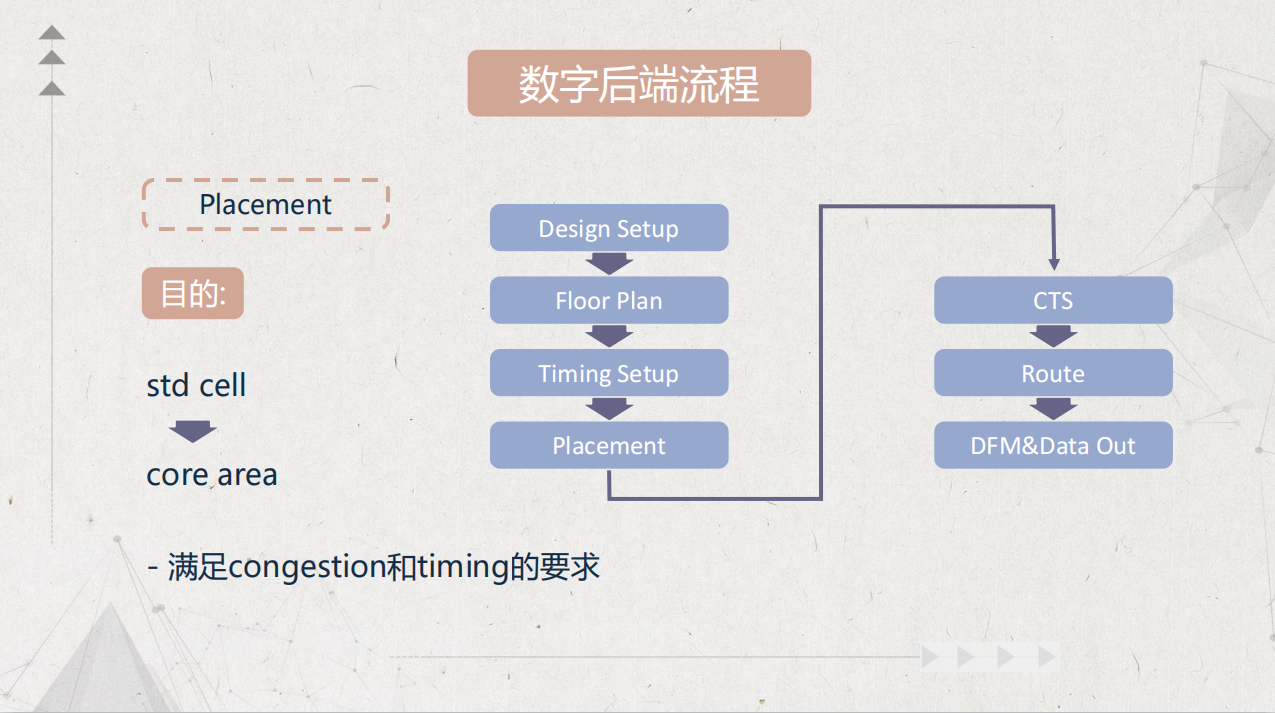

业界主流的后端工具来自 synopsys、cadence 两家公司,虽然两家公司工具不同但是基本流程相似。数字后端流程如图。

Floor Plan:将 Design 导入后端工具后,检查输入文件是否缺少或者有错误。确保 Design 正常 initial 后就可以进行调整 Floor Plan。Floor Plan 主要目的是要确定 design 的形状大小,出 Pin 的位置已经所有 macro 的摆放。

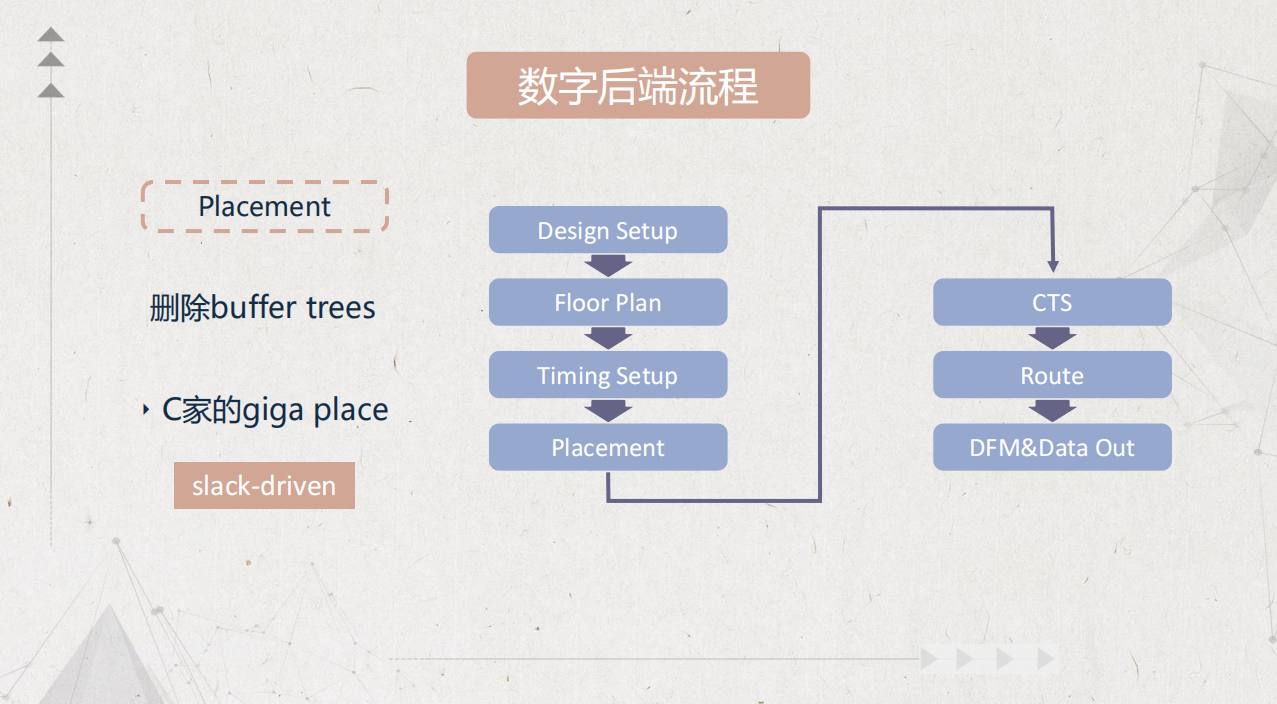

Placement 目的是将所有 std cell 放入 core area 中,并且满足 congestion 和 timing 的要求。

最简单的说可以分为两步: global 和 detail place。global 不考虑 cell 放的位置是否 legal;detail place 的时候会将 cell 放到附近 legal 的位置。在 place 过程中为了得到更好 timing 结果会对关键路径进行逻辑重组,删除 buffer trees。 随着工具的不断发展,目前 place 的引擎已经十分强大。例如 C 家的 giga place,它采用新的算法 slack-driven,通过计算真正 timing而不是预估的 timing 来进行 place, 在 place 的同时进行优化。

Prects 在 Place 之后 CTS 之前,我们会对进行一次 setup timing 优化。只优化 setup,原因是 clock tree 还没做,所有 clock 都是 ideal 的。

CTS:芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。

Routing:CTS 之后整个芯片的大体结构已定。要将信号线通过金属连接起来。绕线过程主要完成一下几个目标。绕线过程中会考虑 DRC 和 LVS,绕完后不会有 DRC/LVS violations 绕线过程中不会导致 timing 变差,也不会引入新的 SI 问题。考虑 DFM,例如 multi-cut via,线宽和线间距。

(8)时序仿真。

同功能仿真,只是将 RTL 代码替换为网表,然后需要加载 SDF 文件和工艺库模型。该步骤的目的在于,在延迟等近似实际工作的条件下,观察功能是否还能保持正确。

半导体产业概述

产业链

1. Foundry

2. Fabless

3. EDA

主要是三大厂商 Cadence 、 Synopsys 和 Mentor Graphics 。

4. Design Service

5. IP vender

- 说点别的,最近在实验室弄了一套小米摄像头,感觉小米的智能家居生态做的挺不错的。

- 寒武纪推出了神经网络处理器芯片,比特大陆提供比特挖矿芯片

数字前端设计流程

架构设计

RTL编写

功能验证

逻辑综合

相当于软件中的编译器,将RTL代码转化为另一种文本形式。

STA

一致性验证

数字后端流程

后记

后面几页ppt就不放了

本文深入探讨了集成电路设计的完整流程,包括芯片设计产业链的五大环节:Foundry、Fabless、EDA、Design Service和IP供应商。详细介绍了数字前端设计的各个步骤,如架构设计、RTL编写、功能验证、逻辑综合、静态时序分析、一致性验证和数字后端流程。同时,提到了半导体产业中的关键企业和工具,如Cadence、Synopsys、 MentorGraphics等,并提及了小米智能家居生态和寒武纪神经网络处理器芯片的例子。

本文深入探讨了集成电路设计的完整流程,包括芯片设计产业链的五大环节:Foundry、Fabless、EDA、Design Service和IP供应商。详细介绍了数字前端设计的各个步骤,如架构设计、RTL编写、功能验证、逻辑综合、静态时序分析、一致性验证和数字后端流程。同时,提到了半导体产业中的关键企业和工具,如Cadence、Synopsys、 MentorGraphics等,并提及了小米智能家居生态和寒武纪神经网络处理器芯片的例子。

784

784

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?