系列文章目录

芯动力——硬件加速设计方法学习笔记(第一章)概述

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(1)

文章目录

前言

学习第三天,打卡学习!

一、延时

1、分支电路中信号有延时

例1: 假设b的延时最大

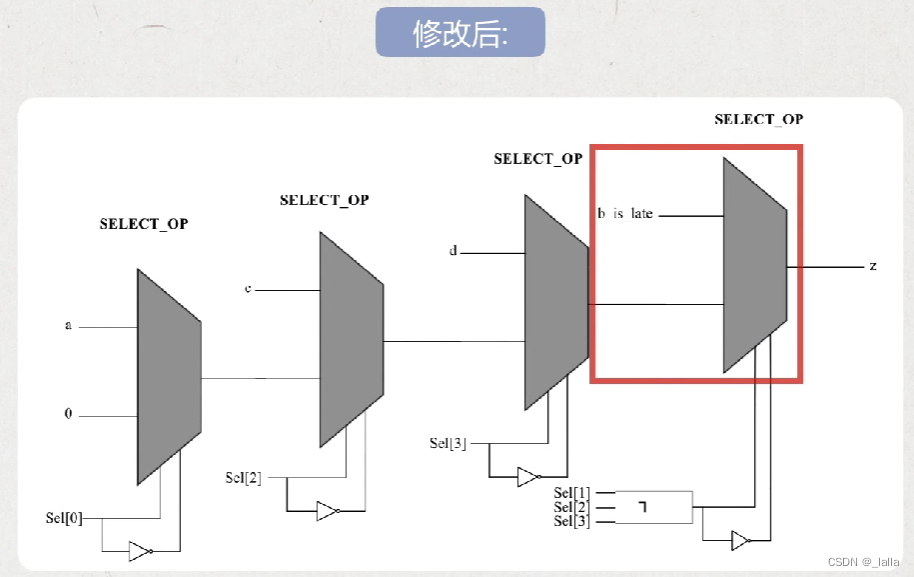

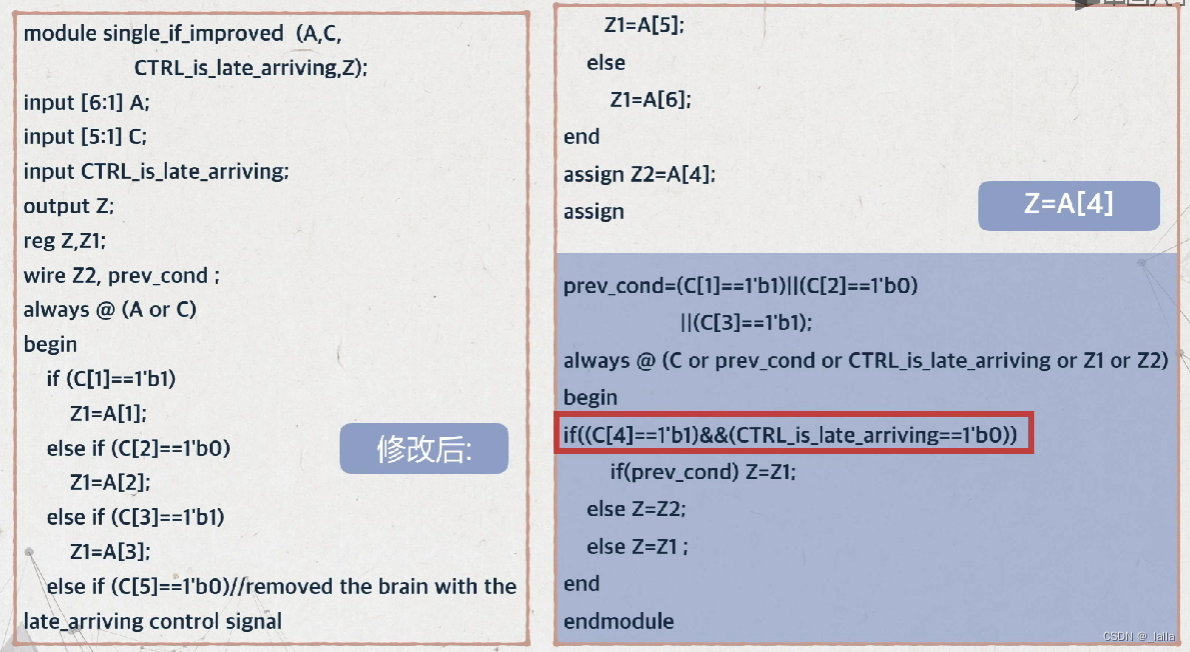

例2: 分支中有一个控制信号比较晚,还是把他挪到最后面

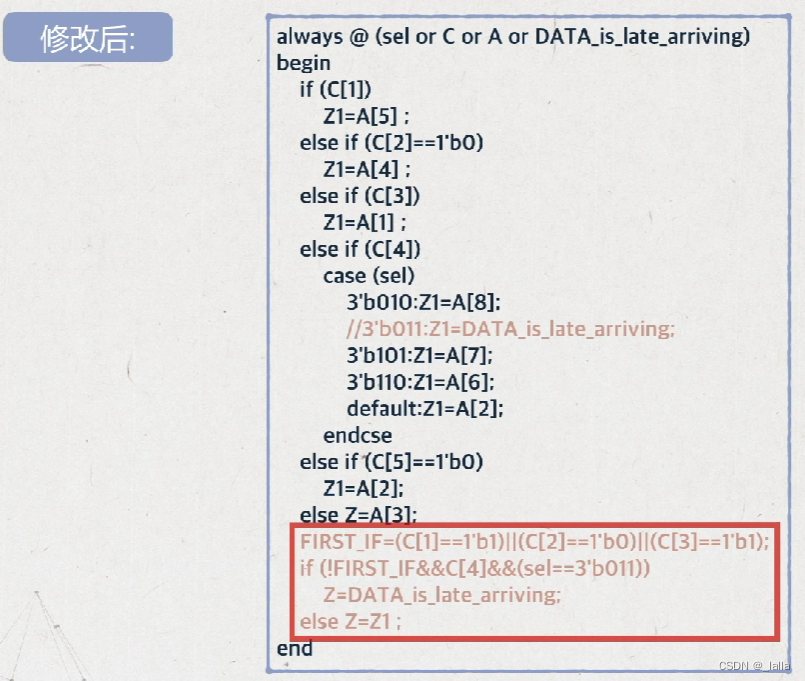

例3: if里面嵌套了case语句

电路是并行case形成的mux、单if语句形成的mux

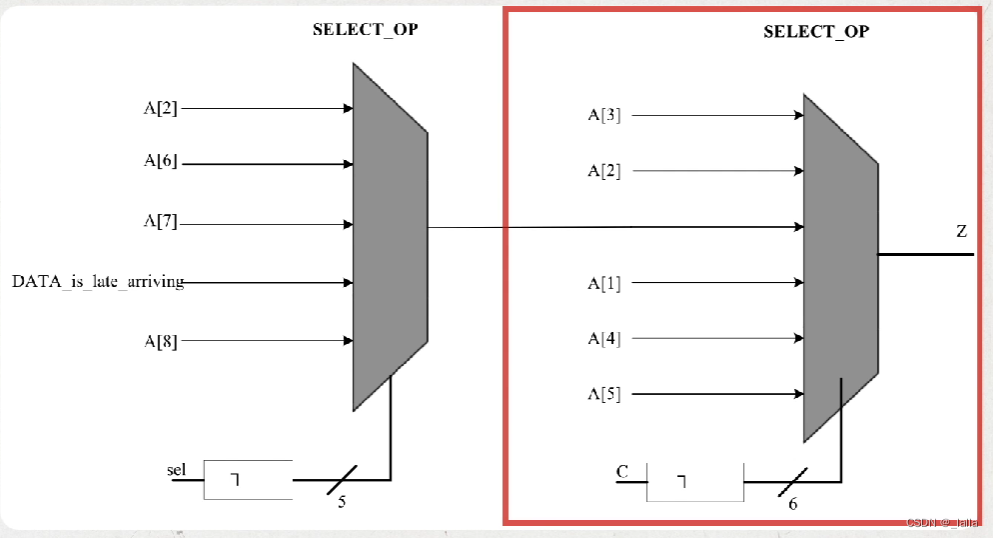

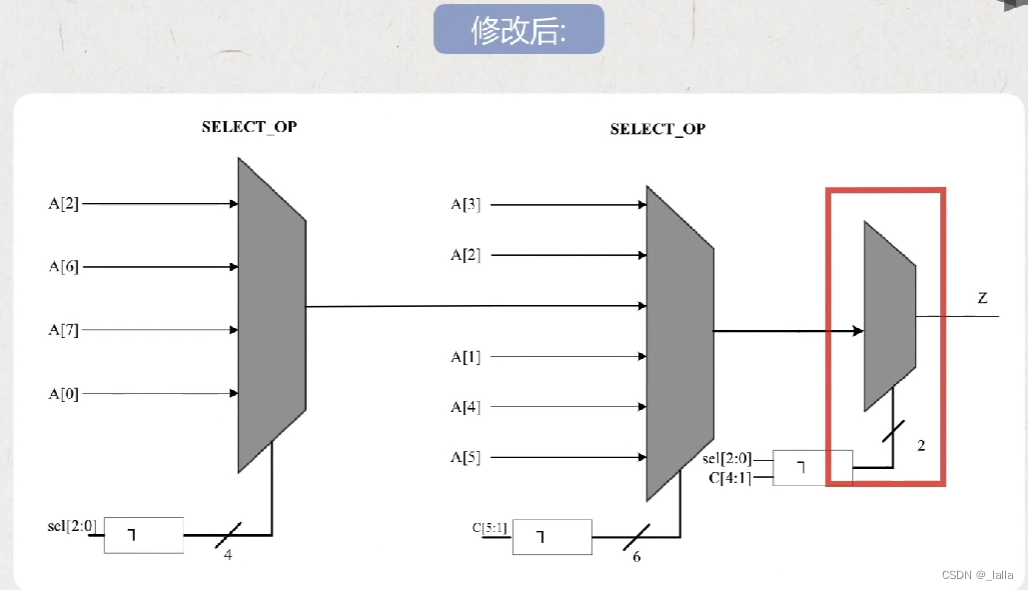

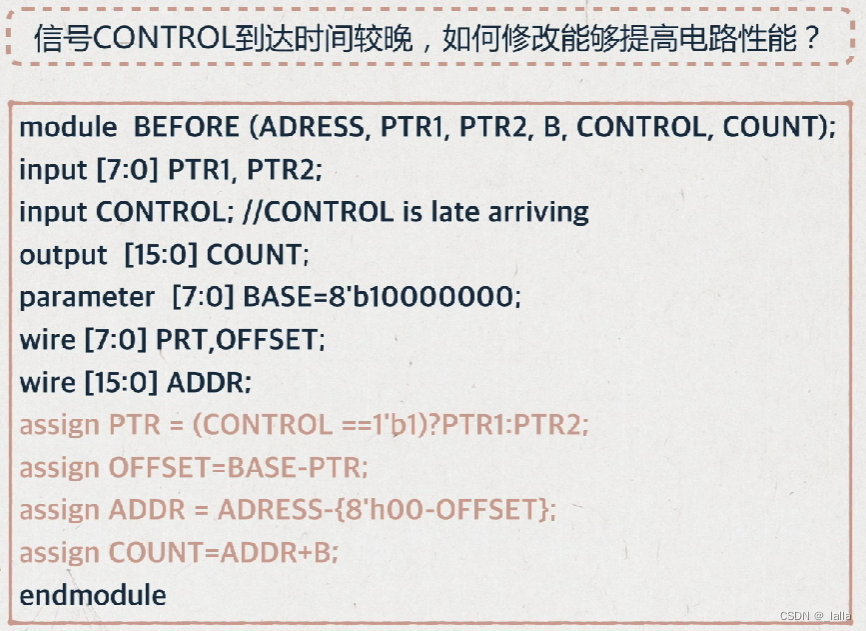

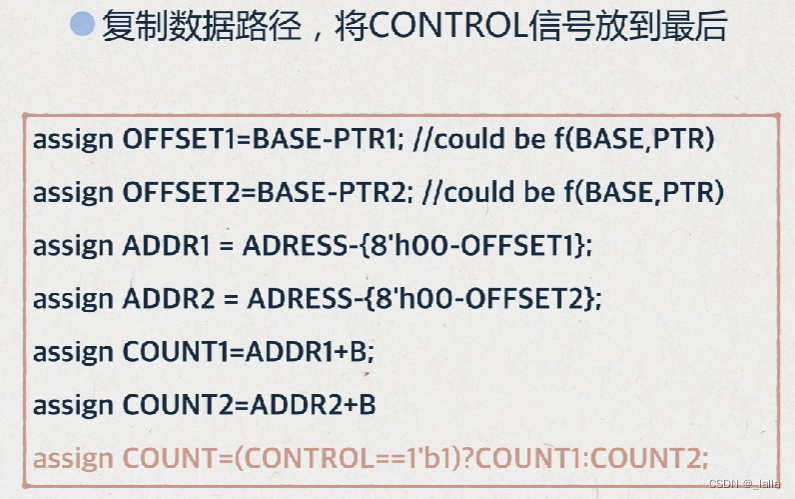

2、数据通道中信号延时

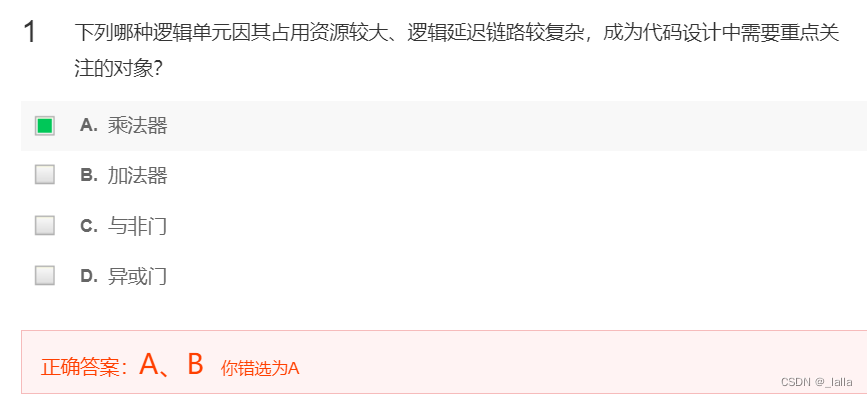

二、面积

要学会估计设计使用资源的数量,如使用了多少个触发器、加法器、乘法器等。

触发器的数量由功能决定,很难减少,同时触发器的面积比较好估计。

因此重点是组合逻辑电路。组合逻辑对应到RTL代码,就是各种运算符。

1、应加以重视,如“ + ”、“-”、“×”、“÷”以及条件语句中的比较运算

对于这些操作,首先应该判断其必要性,是否能用更简单的运算代替。

2、复杂的运算符考虑资源共享

综合器的功能是有限的,从RTL代码方面进行改进,效果更好

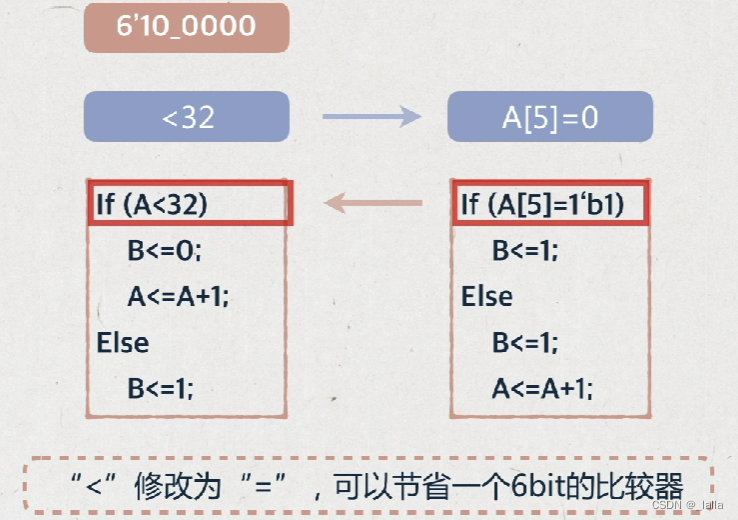

3、多比特的运算

三、功耗

电路动态功耗计算公式

功耗较大:状态机、译码器、多路选择器等

降低功耗的同时,时延和面积也会减少

1、门控时钟

直接关闭整个时钟

2、增加使能信号,使得部分电路只有在需要工作时才工作

使能信号,时钟是一直在翻转的,只是控制信号不再翻转

3、对芯片各个模块进行控制,在需要工作时才工作

4、组合逻辑产生的毛刺会大量消耗功耗

尽量把产生毛刺的电路放在传播路径的最后。另外,可以使用一些减少毛刺的技术。

5、对于有限状态机,可以通过低功耗编码来减少电路的翻转

四、考虑代码对布线布局(routing&placement)的影响

热点:在实现某个功能时需要在一个面积内占用大量的布线资源,如较大的MUX

五、总结

1、在RTL代码编写时要考虑面积、功耗、延时的影响

延迟对应电路性能,降低延迟可以提高芯片的频率,计算速度也就越快。

面积对应流片的成本,成本是芯片生产最重要的因素,面积越小,成本越低。

3764

3764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?