动机

写代码的时候突然想到一组信号能不能同时包含组合逻辑和时序逻辑,就简单尝试了一下。

代码

module test2 (

input clk,

input rst,

input B,

input C,

output reg [1:0] A

);

always @(posedge clk or posedge rst)

if (rst)

A[1] <= 'b0;

else

A[1] <= C;

always @(*)

A[0] = B;

endmodule

主要目的是试一下信号A是否可以这么写,A[0]是组合逻辑,A[1]是时序逻辑。虽然觉得可以,但是不确定。

下面是tb。

`timescale 1ns/1ps

module test2_tb ();

reg clk;

reg rst;

reg B;

reg C;

wire [1:0] A;

always #5 clk = ~clk;

initial begin

rst = 1;

clk = 1;

B = 0;

C = 0;

#10;

rst = 0;

@(posedge clk) begin

B <= 1;

C <= 1;

end

end

test2 U_test2(

.clk(clk),

.rst(rst),

.B(B),

.C(C),

.A(A)

);

endmodule

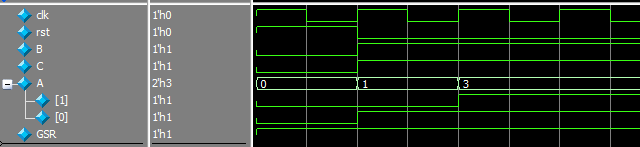

仿真结果

没问题,A[0]和B一致,A[1]是C延迟一拍。

综合结果

综合的电路也和预期一致。

注意,B直连A[0]输出,还是自动综合出了IBUF和OBUF。

2501

2501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?