目录

1.算法仿真效果

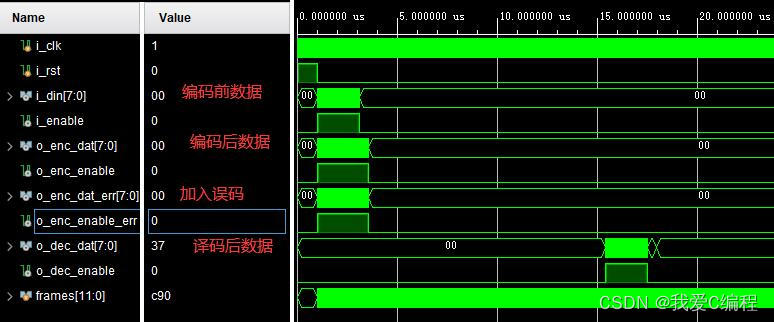

本系统进行了Vivado2019.2平台的开发,测试结果如下:

2.算法涉及理论知识概要

在现代通信系统中,为了确保数据传输的可靠性,经常需要使用各种纠错编码技术。其中,里德-所罗门(Reed-Solomon, RS)码是一种非常强大的线性纠错码,特别适用于纠正多个随机符号错误。随着技术的进步,现场可编程门阵列(FPGA)已经成为实现这些编码方案的高效平台。而IP(Intellectual Property)核则是预先设计好的、可在多个设计中重复使用的功能模块,它大大简化了复杂算法在FPGA上的实现过程。以下将详细介绍基于FPGA和IP核的RS编译码原理。

2.1 RS码基本原理

RS编译码,也就是里德-所罗门编译码(Reed-Solomon Encoding),是一种用于错误检测和纠正的算法,广泛应用于通信、数据存储和网络安全等领域。RS编译码是一种基于有限域(finite field)的纠错编码技术。它利用了多项式运算的性质进行编码,通过在原始数据的基础上添加校验位,使得在数据传输或存储过程中发生错误时,可以通过解码过程检测和纠正错误。

RS编译码的基本原理是将每个信息符号看作是一个多项式的系数,通过将每个符号映射到一个有限域上的元素,从而将纠错问题转化为多项式运算。具体来说,RS编译码通常使用的是二元的m-进制多项式,其中m是一个2的幂次方。例如,对于一个8位二进制数,可以将每个符号映射为一个8次多项式的系数,其中每个系数都取自有限域GF(2^8)。

RS码是一种非二进制、线性分组码,其码字由有限域(Galois Field, GF)中的元素构成。最常用的有限域是GF(2^m),其中m是一个正整数,表示每个符号的位数。RS码以其发明者Irving S. Reed和Gustave Solomon命名,具有两个关键参数:码长n和消息长度k。RS(n, k)码能够纠正最多t个符号错误,其中t = (n - k) / 2。

2.1.1 编码过程

RS编码是将长度为k的信息位映射为一个长度为n的码字。编码过程中,首先选取一个长度为n-k的生成多项式g(x),然后利用该多项式对信息位进行编码。编码公式如下:

c(x) = m(x) * g(x) mod x^n + 1

其中,m(x)是信息位的多项式,c(x)是编码后的多项式。

RS码的编码过程涉及生成多项式的构建和码字的生成。

-

生成多项式:对于RS(n, k)码,其生成多项式g(x)是一个次数为t的多项式,形式如下:

(g(x) = (x - \alpha^0) \cdot (x - \alpha^1) \cdot ... \cdot (x - \alpha^{t-1}))

其中,(\alpha)是有限域GF(2^m)中的一个本原元。

-

消息多项式:原始消息表示为一个次数小于k的多项式m(x)。

-

编码:编码后的码字c(x)是消息多项式m(x)与生成多项式g(x)的乘积,即:

(c(x) = m(x) \cdot g(x))

编码后的码字c(x)具有n个系数,这些系数构成了发送的码字。

2.1.2 解码与纠错

RS解码是在接收到的码字中检测和纠正错误的过程。解码过程中,首先利用接收到的码字计算出错误位置多项式,然后求解该多项式的根,即可确定错误位置。为了纠正错误,需要构造一个错误纠正多项式,然后根据错误位置进行纠正。解码公式如下:

e(x) = c(x) * h(x) mod x^n + 1

其中,h(x)是伴随多项式,e(x)是错误位置多项式。

RS码的解码和纠错过程通常使用基于Berlekamp-Massey算法的解码器或更高效的基于欧几里得算法的解码器。这些算法利用接收到的码字和错误定位多项式的知识来定位和纠正错误。

-

错误定位多项式:该多项式(\sigma(x))的根对应于发生错误的符号位置。

-

钱氏搜索:一种确定错误值的方法,它涉及到求解一个线性方程组。

-

福布斯算法:用于计算错误位置多项式和错误值多项式的另一种方法。

2.2 FPGA和IP核在RS编译码中的应用

2.2.1 FPGA的优势

FPGA以其并行处理能力、可重构性和灵活性在实现复杂的纠错编码方案中具有显著优势。这些特性使得FPGA成为高速、高性能通信系统中实现RS编译码的理想选择。

2.2.2 IP核的作用

IP核提供了预先设计好的功能模块,这些模块已经过优化和验证,可以直接在FPGA设计中使用。对于RS编译码这样的复杂算法,使用IP核可以大大缩短开发周期,降低设计复杂度,并提高设计的可靠性。

2.2.3 实现方式

在FPGA上实现RS编译码通常涉及以下几个步骤:

-

有限域运算:实现GF(2^m)上的加、减、乘和除等基本运算。这些运算通常使用查找表(LUT)或硬件逻辑来实现。

-

编码器实现:根据选定的RS(n, k)参数,实现生成多项式的构建和编码过程。这通常涉及到状态机和组合逻辑的设计。

-

解码器实现:实现基于Berlekamp-Massey算法或欧几里得算法的解码器。这包括错误定位多项式、错误值多项式的计算以及错误纠正逻辑的实现。

-

验证与测试:使用仿真工具和实际硬件对设计进行验证和测试,确保其正确性和性能。

基于FPGA和IP核的RS编译码实现结合了RS码的强大纠错能力与FPGA的并行处理能力和灵活性。通过使用IP核,可以进一步简化设计过程,提高设计的可靠性和效率。这种实现方式在高速、高性能通信系统中具有广泛的应用前景。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/29 22:08:05

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST;

reg i_clk;

reg i_rst;

wire [7:0]i_din;

wire i_enable;

//编码

wire [7:0]o_enc_dat;

wire o_enc_enable;

wire [7:0]o_enc_dat_err;

wire o_enc_enable_err;

//译码

wire [7:0]o_dec_dat;

wire o_dec_enable;

reg[11:0]frames;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

frames <= 11'd0;

end

else begin

frames <= frames+12'd1;

end

end

assign i_din = (frames>=12'd2 & frames<=12'd211)?frames-1:8'd0;

assign i_enable = (frames>=12'd2 & frames<=12'd211)?1'b1:1'd0;

wire [7:0]o_enc_dat_err;

wire o_enc_enable_err;

tops topsu(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (i_din),

.i_enable (i_enable),

.o_enc_dat (o_enc_dat),//编码out

.o_enc_enable(o_enc_enable),

.o_enc_dat_err (o_enc_dat_err),//编码out+误码

.o_enc_enable_err(o_enc_enable_err),

.o_dec_dat (o_dec_dat),//译码out

.o_dec_enable(o_dec_enable)

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

#1000

i_rst=1'b0;

end

always #5 i_clk=~i_clk;

endmodule

00_056m4.完整算法代码文件

V

本文详细介绍了里德-所罗门(RS)码在通信系统中的应用,特别是如何利用FPGA和IP核进行高效编码和解码。此外,还展示了Verilog核心程序实现RS编译码的示例,展示了从理论到实践的全过程。

本文详细介绍了里德-所罗门(RS)码在通信系统中的应用,特别是如何利用FPGA和IP核进行高效编码和解码。此外,还展示了Verilog核心程序实现RS编译码的示例,展示了从理论到实践的全过程。

7003

7003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?