参考:各种芯片简述以及算力解释

不要太较真自动驾驶算力(TOPS)

文章目录

一、CPU计算性能指标

现在随着计算机使用了多级流水线结构,取指、译码、执行等并行方式,单纯使用频率确定性能不太合理,所以采用计算性能来测定CPU性能比较合理,主要有MIPS,DMIPS和FLOPS三个主要概念。

1. MIPS

MIPS(Million Instructions Per Second):字面理解为百万条指令/秒,即每秒执行百万级指令数。这是衡量CPU速度的一个指标。像是一个Intel 80386 电脑可以每秒处理3百万到5百万机器语言指令,即我们可以说80386是3到5MIPS的CPU。MIPS只是衡量CPU性能的指标。

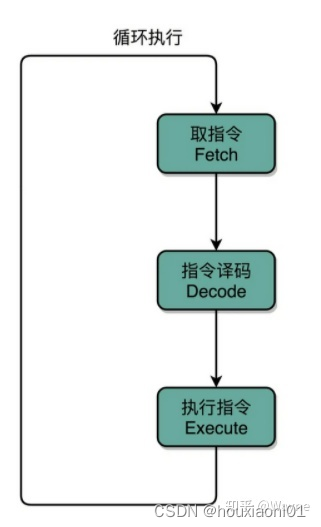

CPU执行指令

程序编译和运行过程中,代码会经过编译器转化成机器可以理解的指令。CPU每个指令周期分为取指令、指令译码、指令执行三个过程,只有在指令执行时才真正有效,在取指令和指令译码时,CPU时间是白白浪费的,而同样的运算在不同架构不同指令集需要的指令数也不一样。

除了 Instruction Cycle 这个指令周期,在 CPU 里面我们还会提到另外两个常见的 Cycle。一个叫 Machine Cycle,机器周期或者 CPU 周期。CPU 内部的操作速度很快,但是访问内存的速度却要慢很多。每一条指令都需要从内存里面加载而来,所以我们一般把从内存里面读取一条指令的最短时间,称为 CPU 周期。

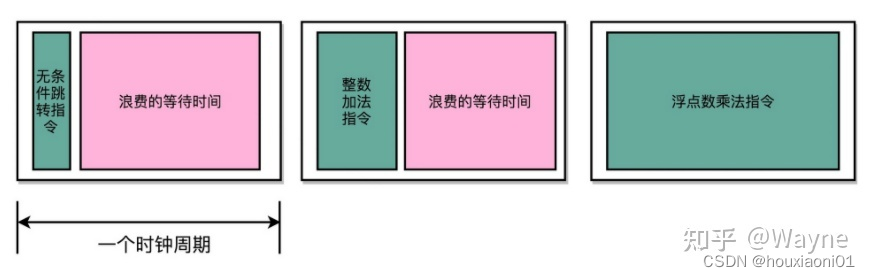

还有一个是Clock Cycle,也就是时钟周期以及我们机器的主频。一个 CPU 周期,通常会由几个时钟周期累积起来。一个 CPU 周期的时间,就是这几个 Clock Cycle 的总和。

对于一个指令周期来说,我们取出一条指令,然后执行它,至少需要两个 CPU 周期。取出指令至少需要一个 CPU 周期,执行至少也需要一个 CPU 周期,复杂的指令则需要更多的 CPU 周期。

从上图可以看出,时钟周期是固定的,但是每个指令执行用时不同,所以需要提高CPU执行效率。

当前提升CPU性能的方法有:流水线技术、流水线冒险/预测、超标量Superscalar、超长指令字设计VLIW、单指令多数据流SIMD等技术(将来慢慢介绍)。尤其是SIMD 技术,是一种“指令级并行”的加速方案,或者说是一种“数据并行”的加速方案。在处理向量计算的情况下,同一个向量的不同维度之间的计算是相互独立的。而CPU 里的寄存器,又能放得下多条数据。于是,我们可以一次性取出多条数据,交给 CPU 并行计算。

但是,因为各个架构的CPU指令集各不相同,所以作为一家厂商的前后代产品对比也许还行,不同厂商之间的对比就比较难看出端倪了。所以有了DMIPS。

2. DMIPS(干石MIPS)

就是赫(chou)赫(ming)有(zhao)名(zhu)的Dhrystone MIPS。Dhrystone是测量处理器运算能力的最常见基准程序之一,常用于处理器的 整型运算性能 的测量。Dhrystone是一种整数运算测试程序。

Dhrystone的解释如下:

A short synthetic benchmark program by Reinhold Weicker weicker.muc@sni.de, weicker.muc@sni-usa.com, intended to be representative of system (integer) progra

本文详细介绍了CPU计算性能的衡量指标,包括MIPS、DMIPS和FLOPS。MIPS是每秒百万指令数,而DMIPS通过Dhrystone基准程序提供了一个标准化的比较方式。FLOPS则是衡量浮点运算能力的单位,常用在科研领域。此外,文章还讨论了算力的重要性,特别是在神经网络计算中,以及跑分测试如CoreMark和其工作原理。

本文详细介绍了CPU计算性能的衡量指标,包括MIPS、DMIPS和FLOPS。MIPS是每秒百万指令数,而DMIPS通过Dhrystone基准程序提供了一个标准化的比较方式。FLOPS则是衡量浮点运算能力的单位,常用在科研领域。此外,文章还讨论了算力的重要性,特别是在神经网络计算中,以及跑分测试如CoreMark和其工作原理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5113

5113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?