目录

七、 大于/大于等于/小于/小于等于比较器逻辑层级及资源使用

前言

最近是无意间看到一个博主写FPGA高速设计的一系列文章,受益颇多,想分享出来一起去学习与讨论FPGA高速设计,并对该博主的文章进行一些小知识点的整理,也是对学习的一个复盘。

了解这些技术方法目的主要是为了进行代码设计的时候能够让我们规避一些问题,比如可以提前评估逻辑资源使用,最后工程是否能跑到我们所需的时钟频率,减少时序为例等,最终减少我们反复去迭代代码的时间。

一、什么是FPGA高速设计?FPGA高速设计的好处是什么?

博主的意思是不是说你的设计频率高,比如设计到400M,500M这样的就叫做高速设计了,而是如果之前的模块代码即使只能跑到20M,但是通过代码的优化可以跑到50M,也是也叫做高速设计。

但其实在工作中很少对与必须要求FPGA跑到很高的频率设计,如果最终代码跑步不上所要求的频率,那就降频处理,如果实在有要求那么就使用资源更多或是型号更高端的芯片。但如果仔细去review代码会发现还有很大的提升地方。

这这里博主提供一个例子就很有代表性:

有些同学会说,提高主频有啥用呢?很简单,我以视频处理举个栗子,你们公司用kintex-7芯片设计的产品可以跑200M,视频处理最大可以支持1080P@60fps,现在老板说还需要做更高端的产品,功能不变,但是需要支持4K @60FPS视频处理,如果不更改代码,你们不得已必须选择更加昂贵的FPGA芯片,但是这时你跳出来说,boss,我可以依然使用之前的kintex-7芯片,只需要优化下代码就可以支持4K视频,这时你一定是公司的一大功臣,活活帮公司省了多少真金白银啊。如果你和我犟,说公司不需要性能更好的视频处理器,那我告诉你如果高速设计帮你节省了FPGA内部资源,你愿意吗?目前很多视频设计中都是用多ppc模式,1ppc表示每个时钟处理一个像素的信息,但是你的像素时钟不够高,无法在kintex-7芯片上支持4K,其中简单办法就是使用2ppc,每个时钟处理两个像素信息,做视频处理的同学都知道,BRAM在设计中的使用和吃饭一样频繁,数据位宽增加直接影响BRAM的使用个数,同时还会增加其他相关逻辑的资源,但是当你把主频提高到400M,像素时钟也同时提高一倍,此时你只需要按部就班使用1ppc进行处理,直接节省了大量的逻辑资源和BRAM的利用,成本不变的情况下,为更多功能的加入提供了可能。

由此可见高速设计是可以节约成本的,帮助我们在同样的芯片上能做出更好的产品。同时也能帮助我们节省编译时间,因为如果代码写的不是很合理,软件工具要帮助我们去不断的优化布局布线,而且最终的结果也会存在时序违例的问题。

个人觉得博主所说的不仅仅是设计方法,而是提供大家在编写代码时的一个设计规范,同时也能够让大家明白这样设计的原因好处在哪里。

二、FPGA CLB逻辑基本单元了解

博主整个系列博文都是以7系列的芯片为举例说明,我也会将Ultrascale的进行补充。

一般学习FPGA的同学在首次接触到FPGA时,资料的第一章都会介绍FPGA的资源,告诉FPGA内部资源有哪些。刚开始接触肯定会觉得代码和这个FPGA资源还关系不到,但是到慢慢深入理解Verilog,慢慢使用FPGA去做项目编写代码,会发现自己写的代码会被映射到FPGA内部这些资源中,而代码最后对应到FPGA内部电路图取决与你的代码设计,所以你的代码质量是整个项目的基础。

如果你已经很了解FPGA资源,那就直接跳过这一章节,如果还想再了解,可以继续往下看。

1.CLB逻辑单元内部结构

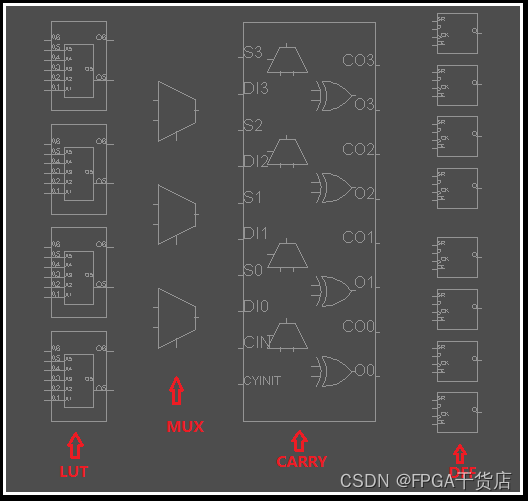

Xilinx的基本逻辑单元叫做CLB,每个CLB中会有两个SLICE,每个SLICE中又包含4个6输入LUT、1个4输入CARRY,3个MUX和8个DFF,下图就是SLICE的内部资源。

而且SLICE分为SLICEM和SLICEL两种,SLICEM中的LUT主要作为分布式RAM使用,SLICEL主要用来搭建逻辑使用。

Ultrascale的SLICE资源更加多,包含个8输入LUT、1个8输入CARRY,7个MUX和16个DFF。

2.LUT查找表

LUT翻译过来叫查找表,它的作用是实现所有逻辑函数的功能模块。对于FPGA来说,无论什么逻辑都可以用LUT来实现。数字电路中学过与非门、异或门、选择器等等基本单元,但是LUT可以把这些功能全部实现,只要输入够多,它可以实现任何复杂的bit运算。

在这个有个问题:LUT可以实现任何逻辑功能,那么ASIC不使用LUT搭建电路,而是使用专本的门电路搭建呢?

那我们看下LUT的实现:对于6输入的LUT,可以认为他是6bit位宽的存储器,能够存储2^6=64位数据,输出是1bit的数据,也就是说6输入为6bit地址线,按照输入特定的地址将对应的1bit数据读取出来,所以LUT的延迟要比专用逻辑电路大,对于FPGA来说,即使综合出一个反相器,也需要使用一个LUT实现,则FPGA使用的资源要远大于ASIC。

3.CARRY进位链

7系列CARRY进位链是4输入,每一位的运算都是重复的。

博主将进位链的各信号及功能实现都进行详细的说明了:进位链描述,就不在这里将了。

三、加法器逻辑层级及资源使用

1.什么是逻辑层级?

在最长路径中(也就是所谓的关键路径)两个寄存器之间的逻辑组合所包含的LUT、CARRY、MUX的个数就是逻辑层级。

2.加法器逻辑层级

博主使用7系列芯片对加法器的逻辑层级进行了详细的说明,K7芯片的全加器逻辑层级,可以仔细的阅读理解。

最后发现两个等位宽的数相加,N bit的全加器则需要使用N个LUT,使用N/4个CARRY的逻辑资源,N/4+1的逻辑层级;

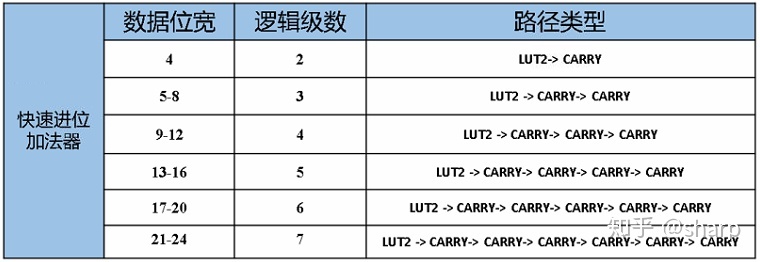

最后总结出K7芯片的全加器逻辑层级的表格:

在这里有个小问题哈,博主是以等位宽的数据相加解释说明,但是如果两个数据位宽不相等,其逻辑层级和使用的资源是否仍和上述表格一样呢?动手试试。

四、累加器逻辑层级及资源使用

博主使用7系列芯片对加法器的逻辑层级进行了详细的说明,K7芯片的累加器逻辑层级,可以仔细的阅读理解。

最后发现S=S+1累加器 ,N bit的累器则需要使用N个LUT,使用N/4个CARRY的逻辑资源,N/4+1的逻辑层级;

最后总结出K7芯片的累加器逻辑层级的表格:

五、被加数为1的加器逻辑层级及资源使用

C=A+1这种类型,暂且叫它为“被加数为1的加法器”,博主也对这种类型的加法器进行的逻辑层级及资源使用的分析,被加数为1的加法器。

最后发现C=A+1类型加法器,使用N/4个CARRY的逻辑资源,N/4的逻辑层级;

注意:在12bit位宽以下,vivado倾向于只使用LUT进行综合,大于12bit以后只使用CARRY进行综合。

最后总结出K7芯片的被加数为1的加器逻辑层级的表格:

六、相等/不相等比较器逻辑层级及资源使用

对于一般相等/不相等比较器,12bit以下都是两级逻辑,位宽极小的使用纯LUT的综合方式,12bit以上,每增加12bit多一级CARRY。

最后总结出K7芯片的相等/不相等比较器逻辑层级的表格:

七、 大于/大于等于/小于/小于等于比较器逻辑层级及资源使用

对于大于/大于等于/小于/小于等于比较器,最后总结出K7芯片的大于/大于等于/小于/小于等于的比较器逻辑层级的表格:

八、乘法器的逻辑层级及资源使用

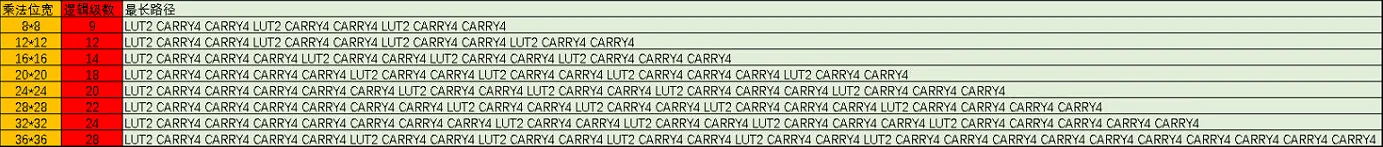

对于乘法器,最后总结出K7芯片的乘法器器逻辑层级的表格:

九、条件语句逻辑层级

不同套嵌级数的if-else对应的逻辑层级和具体路径类型,一般不会用到太多的优先级判断逻辑,比如DDR仲裁中,也只有16级判断,对应的逻辑层级也不超过4级。由此可见,当有逻辑层级较高的路径时,找到代码后不要着急拆分if-else逻辑,需要仔细查看导致层级增加的代码。

上述的if-else语句最为精简,条件判断只是最简单的优先级判断,但如果if语句中包含运算逻辑,那么逻辑层级就会在此基础上增加。

总结

1.大位宽加法器的弊端:

1)位宽越大逻辑层级越高,导致当前加法器路径时序不容易收敛;

2)位宽越大级联的SLICE越多,通过CARRY电路图看到进位值Cn并没有通过寄存器输出,所以工具会尽量将加法器使用的SLICE资源靠拢,不利于其他资源的布局和布线。

例如:以上就是今天要讲的内容,本文仅仅简单介绍了pandas的使用,而pandas提供了大量能使我们快速便捷地处理数据的函数和方法。

2. if-else语句逻辑层级太大原因

if-else语句并不会对逻辑层级产生太大的影响,如果逻辑层级太高,首先需要查看是否条件判断时使用了大位宽的运算;另外写代码时需要注意,如果有大位宽的运算作为判断条件,必须要提前打拍,转为1bit信号再驱动选择器。

1213

1213

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?