FIFO-first in first out,正面意思很好理解。这部分着重介绍同步FIFO,之后再介绍异步FIFO。

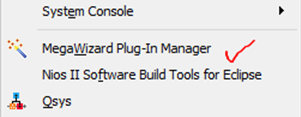

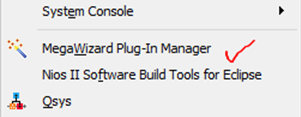

通过fifo的学习,同时为大家介绍quartus ii 中的ip核的调用。具体步骤如下:在MegaWizard Plug-in Manager中搜索fifo,即可进入fifo的io核编辑界面。

编辑界面如下:选择8bit数据位宽,fifo深度32字节(红色标注1、2表示),3表示用作同步fifo(单时钟)。

这一页按如下配置。

FIFO-first in first out,正面意思很好理解。这部分着重介绍同步FIFO,之后再介绍异步FIFO。

通过fifo的学习,同时为大家介绍quartus ii 中的ip核的调用。具体步骤如下:在MegaWizard Plug-in Manager中搜索fifo,即可进入fifo的io核编辑界面。

编辑界面如下:选择8bit数据位宽,fifo深度32字节(红色标注1、2表示),3表示用作同步fifo(单时钟)。

这一页按如下配置。

1066

1066

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?