Spyglass CDC跨时钟错误

本文基于VC_SpyGlass_CDC_UserGuide整理了3种常见的cdc(Clock Domain Crossing)错误。需要注意的是:

- 本文描述的跨时钟错误在特定场景下,有些是允许的,甚至有些是正常设计。因此IC设计者想要确认跨时钟错误需要分析应用场景。

- 还有一些CDC错误是spyglass 工具无法发现的,因此不能全部依赖工具检查。

- 有些项目组为了避免新手对cdc理解不深刻造成bug,对跨时钟设计做了更加严格的规范。例如,下文中的裸跨是不允许存在的。

1、没有跨时钟 CDC Unsynchronized

没有采用跨时钟模块,即咱们通常说的裸跨,不同时钟域的数据直接互连,会存在亚稳态问题。同步电路会进行STA(静态时序分析)保证setup-hold time满足要求,因此寄存器能够保证正确采样。而不同时钟域的信号之间没有setup-hold time要求,无法保证正确采样。

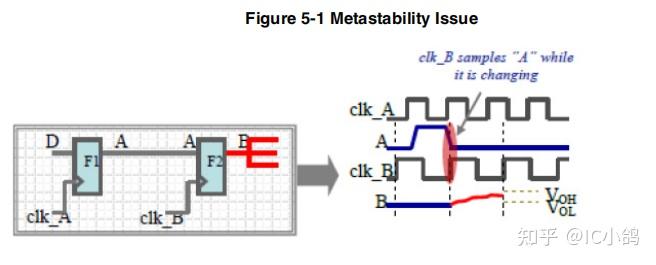

图5-1 所示为亚稳态的案例,F1是clk_A时钟域的寄存器,F2是clk_B时钟域的寄存器,clk_A和clk_B是异步时钟,寄存器F1的输出信号A发生跳变的时刻有可能与clk_B的上升沿发生重叠,此时对寄存器F2来说,在setup-hold time时间区间内,输入A没有保持稳定,因此寄存器F2输出的B是不确定状态,这就是亚稳态。

解决方案:根据实际场景添加对应的跨时钟模块,例如bit同步器,脉冲跨时钟模块,异步fifo,多比特跨时钟等等。

鸽子解读1:

没有跨时钟,不一定就是错误;在一些场景中,为了节约资源不跨时钟是允许的。

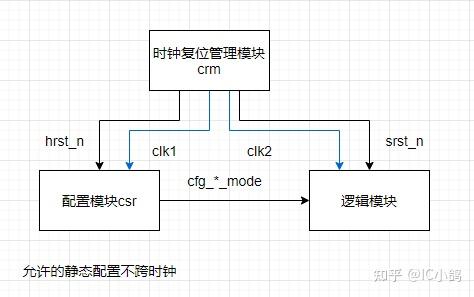

下图所示案例: 配置模块csr模块产生的配置信号cfg_mode是clk1时钟域,直接用于clk2时钟域的逻辑模块。

在芯片使用过程中,复位和配置顺序如下:hrst_n先释放—>完成csr模块寄存器配置—>释放srst_n。

在srst_n复位释放后,静态配置cfgmode不再发生改变。这种情况中,功能逻辑模块处于复位状态时,cfg*_mode发生跳变,这种情况下即使发生了亚稳态也没有影响,因为功能逻辑模块还没允许。

鸽子解读2:

在部分握手机制的模块中,没有跨时钟,也能保证不会出现亚稳态。

CDC无法识别是否实现握手机制,如果跨时钟模块实现握手机制,即能够保证图5-1中的F2准备采样时信号A已保持稳定,虽然会报错,但是不会出现亚稳态。在多bit的配置信号跨时钟模块中就存在这样的情况。

2、CDC Glitch

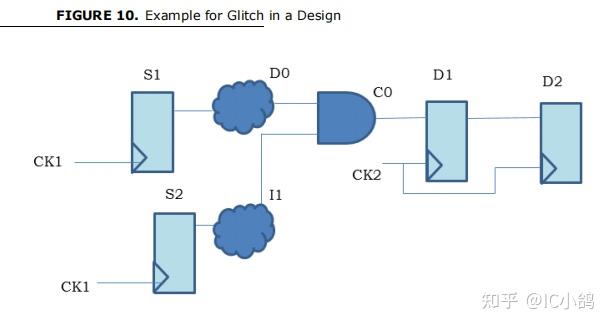

简单来说,就是组合逻辑直接跨时钟,组合逻辑会存在glitch,导致glitch被目的时钟采样到,导致出现不期望的信号

解决方案:增加源时钟域寄存器打拍,寄存器输出的信号才跨时钟。

特殊场景:如果图10中的D0或者I1是一个准静态信号(几乎不会跳变的),那么不会产生glitch,也是可以接受的。

2.1 Glitch 危害

Glitches in a design can be caused because of following three reasons:

Re-convergence of same source (同一个bit信号的组合逻辑)

Multiple sources of different domains converging (多个源时钟域的信号的组合逻辑)

Multiple sources from same domain converging (同一个时钟域的多个源信号的组合逻辑)

2.2 glitch–电路案例

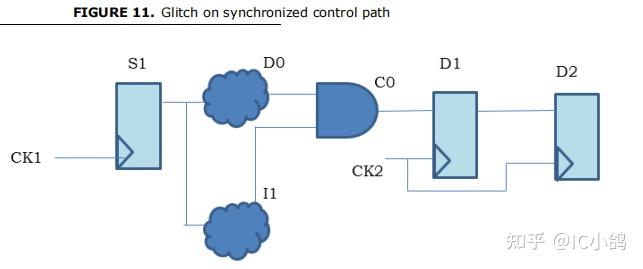

图11:In the above example, source S1 diverges and converges back at C0. Because of different delay in path D0 and I1, glitch can occur at C0. The glitch if occurs very close to clock CK2, it will be captured by the multi-flop structure D1 and propagated downstream. Thus, such unexpected output of the control synchronizers might not be able to act as a proper qualifier downstream.

图12采用了qualifier(限定符)来避免亚稳态,通过qualifier (CK2)来保证C1处于稳定状态。由于没有提供外围电路图,所以不好理解。后期我们会持续更新。

图13中 qualifier(限定符)生成逻辑没有设计好,无法保证C1处于稳定状态,因此图13不仅存避免亚稳态,还存在glitch。由于没有提供外围电路图,所以不好理解。后期我们会持续更新。

3、跨时钟重新汇聚–CDC-Convergence

3.1 Convergence 危害

CDC-Convergence会产生不期望的信号组合,导致功能异常

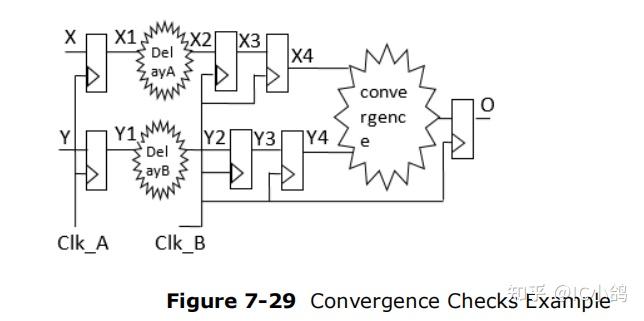

如果多个信号从源时钟域通过不同的跨时钟路径进入目的时钟域,然后这些信号在目的时钟域中又聚合到一起,那么就有可能因为信号的重新聚合导致电路功能上的异常。例如下图7-29和7-28中,x和y的组合(x,y)在同步前只有(1,1)和(0,0)的组合,在同步后出现了(1,0)的组合,还有可能出现(0,1)组合。

如下图7-29和7-28所示,X、X1、Y和Y1 属于clk_a时钟域,delay A和delay B表示不同的延时(走线延时),X3,X4,Y3,Y4属于clk_b时钟域。clk_a和clk_b属于异步时钟。 X4和Y4作为输入进行组合逻辑获得O。

假设因为某些原因,x和y的组合(x,y)只会出现2’b00 或者2‘b11的情况。在正确设计过程中,我们期望x4和y4的组合(x4,y4)也只会出现2’b00 或者2‘b11的情况。但是由于不同的跨时钟路径会导致(x4,y4)出现错误组合。见图7-28,由于delay A和delay B的延时不同,导致X2和Y2到达同步器D端口的时间有差异,因此采样后的值X3和Y3可能会出现一个clk_b周期的差异,此时(x3,y3)出现了2‘b10的组合,此组合会传递到(x4,y4)。因此输出的Q可能是不符合预取的值。此为Convergence导致的错误

3.2 Convergence --电路案例

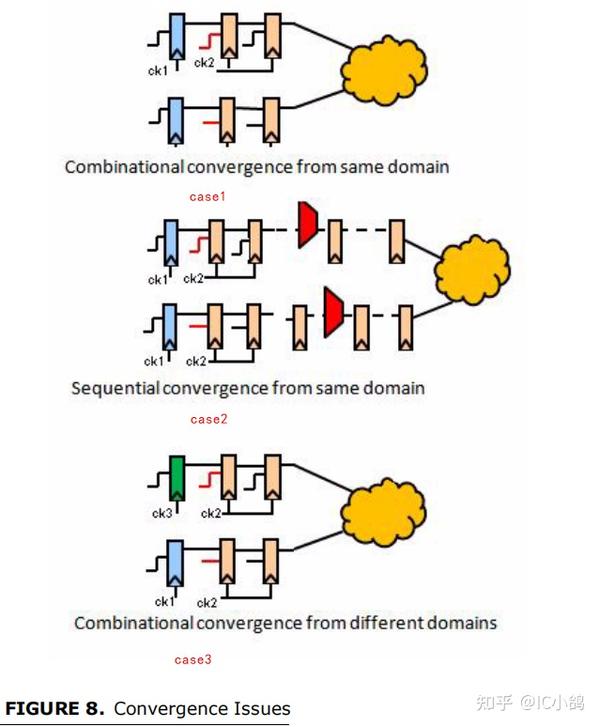

图8显示了3种汇聚的情况:

case1:同一个源时钟域的信号同步后立即汇聚在组合逻辑

case2:源时钟域信号同步后在目的时钟域打了若干拍后再汇聚

如果当目的时钟域打拍数量过大,例如20级,超过了spyglass 工具默认配置值,此种情况spyglass工具就无法检查出问题了。

case3: 不同源时钟域的信号同步后立即汇聚在组合逻辑

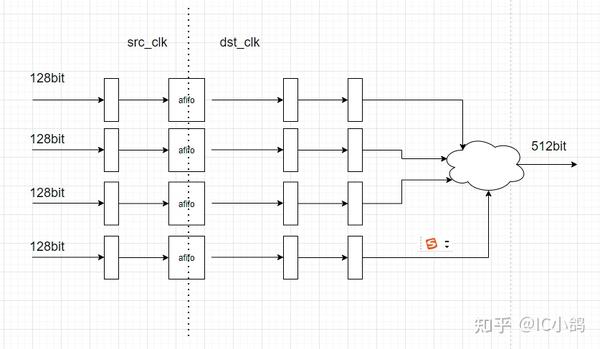

case4:源时钟数据分开经过afifo跨时钟,在dst_clk打了若干拍后汇聚成512bit,与case2类型类似

参考文档:VC_SpyGlass_CDC_UserGuide

1154

1154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?