虽然“左移”一词起源于软件行业,但其重要性在成本飙升的芯片行业中经常被提起。

特别是在汽车行业,高可靠性的芯片是一个漫长的迭代过程,可能需要多次重新ECO流片。

Shift-left是指相比传统开发流程,在更早期发现和修复错误,而不是在实施期间发现它们,因为修复它们的成本会高出100倍。

在验证中利用左移可以减少ECO,使产品更可靠,更快的上市时间,从而降低成本。

左移的过程由两个部分组成:“查找错误”和“修复错误”。前者是验证工程师花费大部分时间的地方。

下图数据突出了验证工程师们花时间的地方。

工程师将大部分时间花在测试规划、测试平台(TB)开发、运行仿真和调试上。

在左边,你可以看到ASIC和验证工程师花费了大约41%的时间进行debug 。在右边,我们看到FPGA工程师的数字是46%。数据收集表明,debug对任何项目的成功都至关重要。

对于混合信号验证来说,这种情况甚至更加严重。在数字芯片中集成AMS模块的客户通常会有专门的模拟设计团队创建模拟IP或使用第三方IP。这些模拟模块使用原理图和SPICE设计,并在本地测试平台上验证。然后交付这些模拟模块,用于顶层集成。

系统集成可能会决定使用模拟IP的纯晶体管格式,或者根据他们的验证需求决定使用模拟模块的更高抽象。这些抽象可能不太准确,但速度很快,易于集成,也可以使用Verilog-AMS或VHDL-AMS更准确地表示。

实数模型(RNM)正在成为模拟模块建模的新甜点,因为它们在性能和准确性之间提供了平衡。

实数建模(RNM)是离散时域中模拟电路的功能建模。如下图所示,真正的平滑模拟信号大致可以用离散步进响应表示。

处于离散时域允许模型保持在100%的数字流中,允许对模型进行非常快速的事件驱动仿真,可能比SPICE快10到1000倍。没有模拟仿真中需要求解的矩阵。然而,准确性是有限制的,因为这只是模拟的传递函数建模。此外,模拟模块的频域建模要复杂得多。

那么,为什么要使用实数模拟模型呢?为什么不使用数字Verilog?毕竟,SoC在数字领域中经过验证。SoC同时具有模拟和数字模块,主要挑战是这两个域之间信息握手的建模。

基于Verilog/System Verilog抽象,wire只有三种状态(0,1和X)。它无法捕获模拟功能行为,这可能会导致信息丢失并最终导致功能故障。

可以在下图中看到这一点,其中wire无法捕获从A模块到B模块的真实值。在实数建模中,实线(wreal或SV nettype)可以携带实数值,从而能够对正确的模拟行为进行建模。

RNM模型的速度和精度优势有助于混合信号芯片左移——在没有完成原理图的情况下,验证可以更早开始,模型也可以重复使用。RNM模型还可以实现高级混合信号验证,例如UPF和UVM。最后,由于我们处于离散领域,只需要一个仿真器——数字求解器。

然而,使用实数建模需要一些开销。首先,设计者必须了解模拟设计的正确功能行为,建模需要额外的时间和专业知识。其次,需要用原理图设计来检查模型功能等价性和仿真精度。

RNM方法中的三项主要活动是:构建/更新模型、验证模型和使用模型。整个流程涉及反向注释和优化,以提高模型的质量。

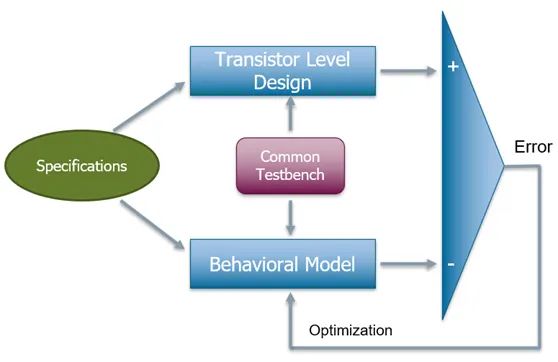

RNM模型的质量说明了它与真正的SPICE电路行为有多相似。必须不断检查原理图与RNM模拟的功能正确性。

请记住,一个糟糕的模型比“没有模型”更糟糕。方法是为模型和原理图构建一个通用的测试平台,为两个模块提供相同的激励,运行仿真,检查结果,并修改或优化模型。

即使经过精心的关注,错误bug也可能在RNM或混合信号验证流程中存在。bug可能是由于编码错误,例如非法赋值。这非常普遍,因为RNM的方法和标准仍在发展。连接RNM模块需要清楚地了解复杂的概念,如SV nettypes 。不当使用这些可能会导致功能故障。bug也可能是由于没有正确验证与SPICE的模型等价性而导致的。

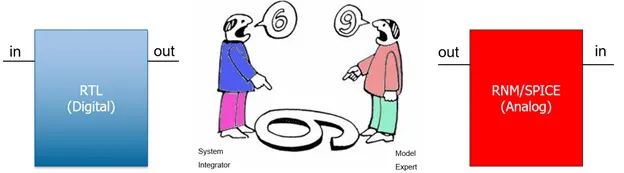

由于利益相关者内部的沟通不畅,出现了错误的使用模式。通常,模拟模块设计与建模专家共享规格,他们创建并测试模型。他们可能会使用单独的测试平台,因此由于建模和系统集成之间的沟通不畅,可能出现功能故障。

例如,如果一个模块的端口顺序被交换,在顶层集成该模块期间可能会引入一个错误,这个场景可能会引入一个导致功能故障的错误。

所有这些场景和在模拟和数字界面上发生的问题的复杂性使调试混合信号仿真成为一项非常繁琐和乏味的任务。几十年来,验证工程师依靠手动观察波形和遍历源代码来识别混合信号错误。这种方法会深刻影响整个验证周期和流片时间,最终推迟上市时间。

使用实数建模肯定有助于混合信号验证的左移趋势。然而,验证团队需要有一个强大的RNM方法来构建RNM模型,根据SPICE验证它们,并正确地将它们集成到整体验证流程中。

981

981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?