标准单元库Standard cell library是ASIC设计流程中的组成部分,有助于大幅缩短设计时间。ASIC设计中使用的标准单元与其他一些文件共同组成标准单元库。

标准单元库:

标准单元库是定义明确和预先K库的逻辑单元的集合,具有多个驱动强度和多个阈值电压的crll,并且标准单元的布局也是预先定义好的。它还包含一些physical only cell和一组place and routing(PnR)工具所需的库文件。

预表征K库:

在将标准单元纳入标准单元库之前,标准单元 需经过原理图设计、仿真,然后是符号创建、布局设计(根据标准单元的布局规则)、物理验证、提取和表征。因此,标准单元库中可用的cell没有任何DRC违规,具有良好的PPA特性,适用于自动布局布线的PnR工具。

多驱动强度cell:

低驱动强度cell需要更少的功耗和面积,但具有更多的延迟和更多的transition time,而高驱动强度cell可以驱动更多数量的cell并具有快速的transition time。因此,根据要求,PnR设计工程师选择cell的驱动强度,以优化面积、功耗和性能。

Multi-Vt cell:

与高阈值电压(HVT)cell相比,低阈值电压(LVT)cell的延迟更小,但泄漏功耗更高。因此,根据timing和功耗的要求,PnR工程师使用HVT和LVT单元来平衡设计的功耗和timing。多Vt cell的面积没有差异。现代标准单元库通常包含ULVT、LVT、SVT、HVT类型的cell,其中Vt是递增的。

physical only cell:

在物理设计中,我们需要在标准单元之间添加各种类型的physical only cell,以减轻各种影响和制造问题。这些cell没有任何逻辑功能。例如,为了克服latch-up问题,我们需要添加well tap cells。类似的还有,Decap cells, endcap cells, antenna cells和filler cells。

然后,我们将讨论标准单元库以及一组重要文件。

cell集合:

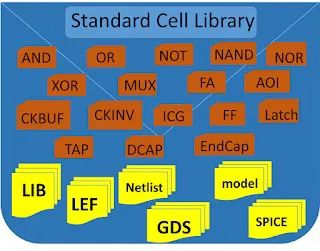

一般来说,标准单元库包含以下类型的单元格:

- 所有基本的门(如AND、OR、NOT、NAND、NOR、XOR等)

- 复杂门(如MUX、HA、FA、Comparators、AOI、OAI等)

- 时钟树cell(如clock buffer、时钟反相器、ICG cell等)

- 触发器和latch

- delay cell

- physical only cell

- 可扫描的触发器

除了标准单元之外,还有一些自动布局布线工具需要的文件。

-

- LIB文件(.lib)

- LEF文件(.lef)

- Netlist文件(.v)

- GDS文件(.gds)

- SPICE网表(.sp)

- 模型文件(.m)

此处提及的所有文件格式都参考了Cadence工具。在Synopsys工具中,一些文件格式不同,但文件内的信息是相同的。

在K库期间生成时序库(LIB或DB)文件。库文件包含cell延迟、功耗和面积信息。物理库(LEF)文件是cell布局的抽象视图。LEF文件包含cell边界、cell内引脚、位置、方向和每个引脚的金属层的信息。Netlist文件是定义cell功能的Verilog文件。GDS文件是cell的布局。SPICE网表是SPICE格式的cell网表,用于仿真。模型文件包含SPICE仿真所需的cell的各种设计参数。

4707

4707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?