标准单元standard cell是ASIC设计流程中作为基本构建块使用的定义明确和预先表征pre-characterized的单元。

注:这个表征也就是我们通常所说的K库。

所有这些cell的高度相等,可以轻松放入标准单元行row中 ,并节省了大量ASIC设计时间。

标准单元的布局

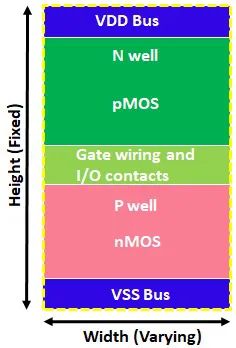

所有标准单元的高度都相同。在下图的帮助下,对标准单元的主要特征进行解释。

标准单元布局样式

在标准单元的顶部,有VDD rail,底部有VSS rail。两个电源导轨都拉入Metal-1层。在VDD rail和VSS rail之间有三个主要区域,一个nwell区域、一个nwell和pwell区域的间隙。nwell区域靠近VDD rail,pwell区域靠近VSS rail。pMOS晶体管建在nwell内部,因此所有pMOS晶体管都在cell的上半部分,同样,所有nMOS都在标准单元的下半部分。

原理图的布局可以用各种方式绘制。例如,NAND门的布局可以按照以下两种不同的风格绘制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?