本文详细解释了为什么两级触发器同步器可以帮助防止亚稳态传播并解决数字IC设计中的CDC问题。

时钟域交叉(CDC)的主要问题是,当目标时钟域捕获异步跨时钟域信号时,由于建立或保持时序违例,亚稳态状态可以在整个设计中传播,导致芯片故障。CDC设计中的亚稳态是无法预防的,但可以使用同步器来避免亚稳态的传播。

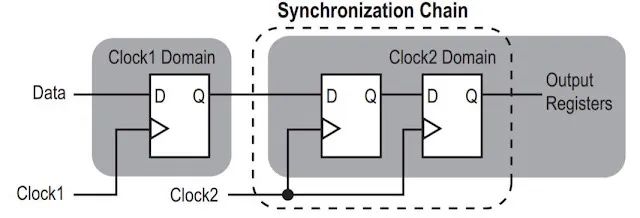

j两级触发器同步器如何防止亚稳态传播?

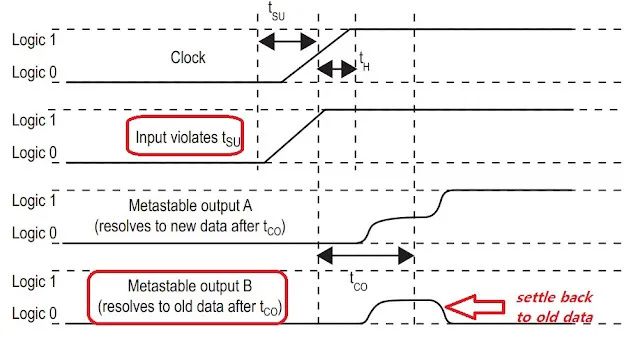

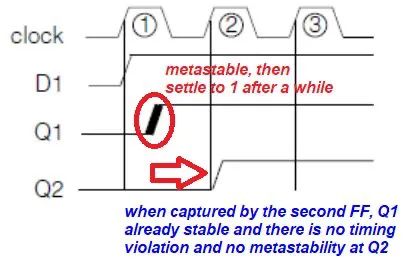

如上图所示,当第一个触发器

(FF)数据输入违反建立或保持时序要求时,输出A/B将变为亚稳态。然而,在不可预测的延迟(Tco)后,FF输出将稳定在某个逻辑水平。

这就是第二个FF的作用,也就是防止亚稳态在整个设计中传播。由于亚稳态将在Tco后稳定到稳定状态,当时钟下一个上升边缘被第二个FF捕获时,Q1输出或D2输入数据可能已经稳定,也就没有建立或保持时序违例了。因此,FF2可以在没有亚稳态的情况下成功存储Q1/D1的稳定逻辑电平。换句话说,亚稳态状态可以通过FF2的输出可以安全地被下一个逻辑块使用。

目标时钟的时钟周期越高,亚稳态传播到下一个逻辑块的概率就越小,因为这为在第二个FF捕获之前,有更多的时间来稳定。双触发器同步器是CDC设计中最常用的同步器

平均故障间隔时间(MTBF)参数可以对亚稳态导致的设计失败概率进行建模。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?