功耗分析方法的更新终于上线了,希望没有让大家久等 😃

在上一篇分享EDA工具里的功耗分析方法(上)中,一起见识了EDA工具在功耗分析中的策略和归一化的方法,便于表述起见,引用下表作为本章的知识起步点:

| 功耗类别 | 目标类别 | 计算公式 | 解释 |

|---|---|---|---|

| 内部功耗 | pin | P l i n t e r n a l = ∑ 1 n A P i n i n t e r n a l P_{linternal}=\sum_1^nAPin_{internal} Plinternal=∑1nAPininternal | 基于所有pin上漏电功耗的总和 |

| 翻转功耗 | net | P s w i t c h i n g = O N e t s w i t c h i n g P_{switching}=ONet_{switching} Pswitching=ONetswitching | 基于cell的output net 上的反转率和cap进行的核算 |

| 漏电功耗 | cell | P l e a k a g e = C e l l l e a k a g e P_{leakage}=Cell_{leakage} Pleakage=Cellleakage | 基于对cell的自身的漏电的library查看 |

在上文也有提到一个更为精准化的描述方式,SDPD (Status Dependency Path Dependency),这个对于功耗计算有实际的影响。那么为何在功耗的计算里边会有这个SDPD呢?SDPD又是通过怎么样的方式影响功耗计算呢?一起打开工艺库的信息一探究竟吧!

工艺库的功耗描述

工艺库里的漏电功耗(leakage power)描述

打开一个MUX2 cell的lib描述,看看和leakage power相关的的信息

cell ("SEL_MUX2_4") {

cell_footprint : "DST_MUX2";

# default leakage power= default_VBP_leak + default_VDD_leak

cell_leakage_power : 0.021083775;

# 偏置电压对应的功耗

leakage_power () {

related_pg_pin : "VBP";

value : "1.37375e-05";

# common-power leakage

leakage_power () {

related_pg_pin : "VDD";

value : "0.0210700375";

# SDPD !D0&!D1&!S leakage power @ VBP

leakage_power () {

related_pg_pin : "VBP";

when : "!D0&!D1&!S";

value : "5.57835028e-06";

# SDPD !D0&!D1&!S leakage power @ VDD

leakage_power () {

related_pg_pin : "VDD";

when : "!D0&!D1&!S";

value : "0.0183689763";

- 漏电电压是由所有的power rail 所构成:譬如这里就有bias和common的区分

- SDPD是所有输入可能的描述

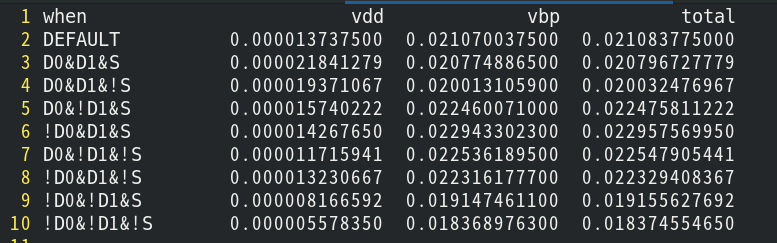

可以使用脚本快速进行抓取转成列表。

可以看到,这是一个三输入的器件,那么总计会有8中输入可能,lib的leakage的信息基于输入可能性的全完备罗列。

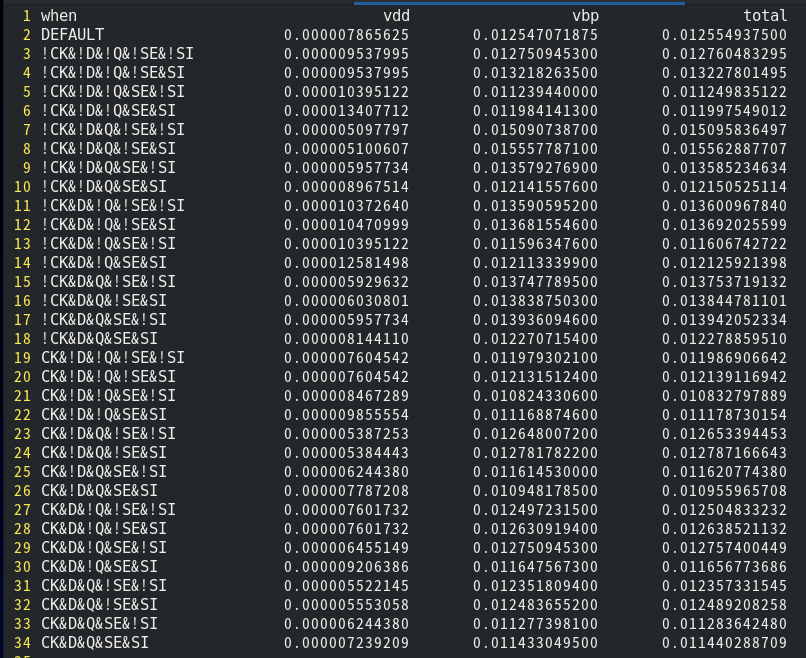

对于一个包含SI和SE的DFF,这里有CLK的器件,对于不同Q的输出,器件的状态也不一样,会导致漏电的不同,所以可以看到FF的漏电信息,包含的输出口Q的影响,这样总共就有4+1=5个管件的组合方式,亦即32中可能,加上默认,全备的漏电信息表格如下:

至于为何会有Q输出管教的信息来组合成为leakage power tabel,一起回顾一下大学课本里的下图就可以领略到其中的原理了:Q和!Q都会反接回来构成类似锁存的结构体:

图片来自网络,侵删

还有一个细节可以通过此表了解到,bias电源导致的漏电比主电源(VDD)要来的小的多。这也是吻合偏置电压的原理的。

工艺库里的内部功耗(internal power)描述

以MUX2 为例,一起看一下interenal power的描述:

cell ("SEL_MUX2_4") {

......

pin (S) {

capacitance : 0.002820029;

direction : "input";

fall_capacitance : 0.002761232;

max_transition : 4.308;

related_ground_pin : VSS;

related_power_pin : VDD;

rise_capacitance : 0.002878826;

internal_power () {

# bias PG related internal_power description

related_pg_pin : "VBP";

# condition

when : "!D0&!D1";

fall_power ("pwr_tin_8") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

values ("-5.63411e-05, -5.540512e-05, -6.377697e-05, -4.595821e-05, -6.756144e-05, -6.15605e-05, -6.171516e-05, -6.163207e-05");

}

rise_power ("pwr_tin_8") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

values ("8.111282e-05, 7.08698e-05, 5.968669e-05, 5.155256e-05, 5.807869e-05, 6.204414e-05, 6.182517e-05, 6.175735e-05");

}

}

internal_power () {

# common PG related internal_power description

related_pg_pin : "VDD";

# condition

when : "!D0&!D1";

# the internal_power during pin S falling edge

fall_power ("pwr_tin_8") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

values ("0.002097898, 0.00210684, 0.001989685, 0.002036636, 0.001995899, 0.001987284, 0.001991492, 0.002053458");

}

# the internal_power during pin S rising edge

rise_power ("pwr_tin_8") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

values ("-0.0001334809, -6.114718e-05, -0.000153519, -0.0001819992, -0.0002029397, -0.0002175415, -0.0002181976,

}

}

}

......

pin (X) {

direction : "output";

function : "((D0&!S)|(D1&S)|(D0&D1))";

max_capacitance : 0.8309614;

max_transition : 4.308;

min_capacitance : 6.155e-05;

related_ground_pin : VSS;

related_power_pin : VDD;

power_down_function : "!VDD+!VBP+VSS+VBN";

internal_power () {

related_pg_pin : "VBP";

# Path Dependency

related_pin : "D0";

# Status Dependency

when : "!D1&!S";

# X: falling edge power due to related D0 change. positive unate

fall_power ("pwr_tin_oload_8x7") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941");

values ("-0.0003287909, -0.0003265358, -0.0003263012, -0.0003258171, -0.0003259071, -0.0003233576, -0.0003219219", \

......

"-0.0003294999, -0.0003285813, -0.0003292956, -0.0003293134, -0.0003286557, -0.0003291086, -0.0003283838");

}

# X: rising edge power due to related D0 change. positive unate

rise_power ("pwr_tin_oload_8x7") {

index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308");

index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941");

values ("0.000327204, 0.000329085, 0.0003304601, 0.0003274369, 0.0003265309, 0.0003275536, 0.0003209762", \

......

"0.0003299443, 0.000328975, 0.0003286823, 0.0003299806, 0.0003291929, 0.0003285925, 0.0003283199");

}

}

}

......

}

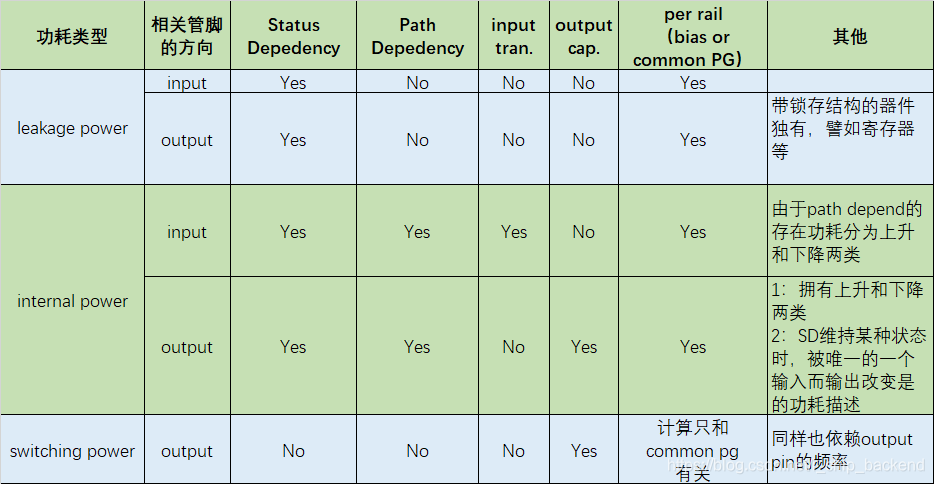

可以看到,internal power除过是status dependency,同时也是path dependency。基于internal power的特性,这里也同时需要考虑 input tran和output_cap的状态。

通过脚本抽取,可以看到如下特性:

- 输入pin:会对应一个rise和fall的internal power per rail。对应的,每一个input的internal power也是被其他输入pin的状态所影响。

- 输出pin:在一个input pin的path dependency的情况下,在其他的input pin的status dependency,这个唯一变化的输入pin的变化,会带来相应的rise和fall的internal power

工艺库里的功耗描述小结

上面的阐述比较多,为了方便大家阅读,以下面的表格做一个相关的小结:

花了一些时间一起学习了一下lib,看到这里,大家应该可以理解为什么工具需要使用SDPD的方式来核算internal和leakage的power了吧:所有的计算都是基于基础数据结构和类型

SDPD对于功耗计算的影响

在实际的芯片当中,一个器件在不同时间的表现状态可以不同,这里就像一个真值表,假定设计里边有如下一个inverter器件的工作状态。

所以,在对功耗的核算中,工具引入了下面两个重要的参数

- Status Possibility (SP): 各种状态的出现比率,通常以一个周期的高电平所占比率来体现,譬如一个占空比50%的时钟,那么他的SP就是0.5。这个参数会直接影响leakage pwoer,间接影响internal power

- toggle rate (TR):反转率,通常指一个单位时间(time unit)内信号的反转次数,包含上升沿和下加沿,譬如在一个以ns为单位时间的工艺里,1GHz的信号对应的toggle rate就是2。这个参数会直接影响internal power

leakage power的计算公式

所以,芯片的leakage power,就是多有的State Dependency下对应的出现概率的之和,公式如下

P

l

e

a

k

a

g

e

_

t

o

t

a

l

=

∑

i

=

1

n

P

S

D

(

i

)

∗

R

S

D

_

S

P

(

i

)

P_{leakage\_total}=\sum_{i=1}^nP_{SD(i)}*R_{SD\_SP(i)}

Pleakage_total=i=1∑nPSD(i)∗RSD_SP(i)

其中

R

S

D

_

S

P

R_{SD\_SP}

RSD_SP是指在某种SD 所对应的出现的概率(SP)。

∑

i

=

1

n

R

S

P

=

1

\sum_{i=1}^nR_{SP} =1

i=1∑nRSP=1

internal power的计算公式

internal power是pin based和SD、PD多维数组计算体

P

i

n

t

e

r

n

a

l

t

o

t

a

l

=

∑

i

=

1

n

P

i

n

t

e

r

a

l

_

p

o

w

e

r

_

(

i

)

P_{internal_total}=\sum_{i=1}^nP_{interal\_power\_(i)}

Pinternaltotal=i=1∑nPinteral_power_(i)

这里的

P

i

n

t

e

r

a

l

_

p

o

w

e

r

P_{interal\_power}

Pinteral_power是任意一个pin对应的internal power,也是包含input和output

这里对于每一个pin上的leakage_power可以用下面的公式来表达

P

i

n

t

e

r

a

l

_

p

o

w

e

r

=

∑

i

=

1

n

(

P

S

D

(

i

)

_

r

i

s

e

_

p

o

w

e

r

)

+

P

S

D

(

i

)

_

f

a

l

l

_

p

o

w

e

r

)

)

∗

P

t

o

g

g

l

e

_

r

a

t

e

P_{interal\_power}=\sum_{i=1}^n(P_{SD(i)\_rise\_power)}+P_{SD(i)\_fall\_power)})*P_{toggle\_rate}

Pinteral_power=i=1∑n(PSD(i)_rise_power)+PSD(i)_fall_power))∗Ptoggle_rate

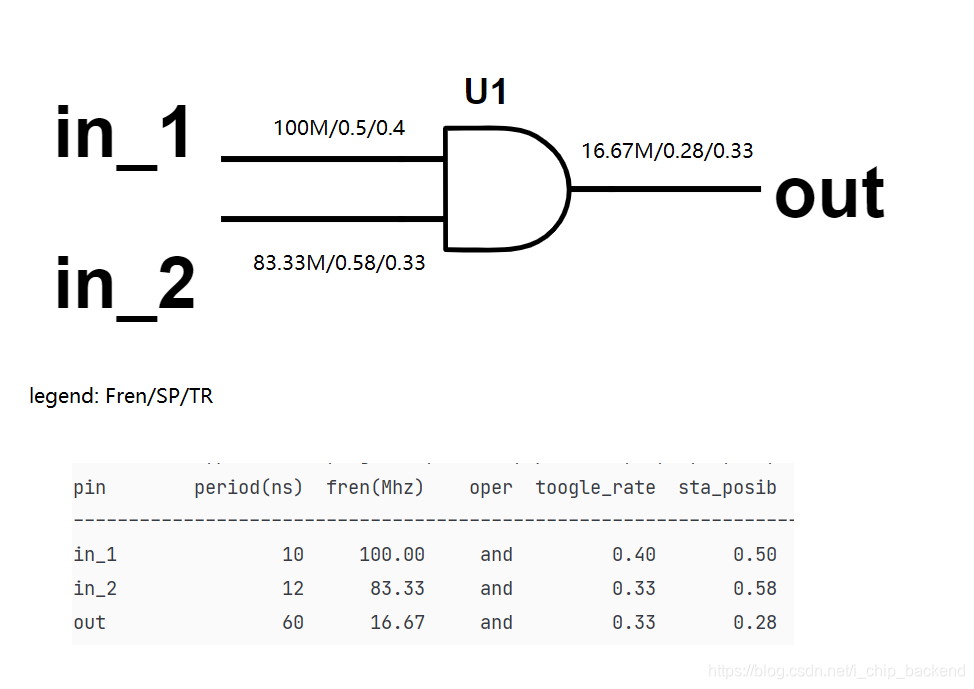

SP和TR计算示例

目前为止,有了TR和SP就可以展开对leakage_power和internal_power的计算。在实际的芯片里边,可以使用一些手段来计算器件的TR和SP,为此,笔者使用python完成了一个这样的一个功能:基于输入管脚对简单组合逻辑进行输出管脚的TR和SP的计算:

拥有了计算功耗计算的公式,以及自研程序,功耗计算的大门也就向大家彻底打开了。

本章词汇

| 词汇 | 解释 |

|---|---|

| Bias | 偏置电压:偏置电压是指晶体管放大电路中使晶体管处于放大状态时,基极-射极之间,集电极-基极之间应该设置的电压 |

【敲黑板划重点】

cell的leakage和internal powe都是和pin的强关联,同时也和TR和SP等有关系,需要仔细理解其中的奥秘,才能做到百战不殆

参考资料

Rakesh Chadha • J. Bhasker An ASIC Low Power Primer

艾思 自研tcl脚本:基于lib库的功耗信息提取

艾思 自研python脚本:TR、SP的核算“

7858

7858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?