一、实验目的

熟悉QuartusII仿真软件的基本操作,并用VHDL语言设计一个异或门、3-8译码器和模型机指令译码器。

二、实验内容

1、熟悉QuartusII软件的基本操作,了解各种设计输入方法

2、用VHDL语言设计一个异或门、3-8译码器和模型机指令译码器,查看并分析其原理图,最后进行仿真验证。

三、实验方法

-

实验方法

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是Quartus II。

-

实验步骤

-

新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径,三个实验项目分别设置三个project name为XOR2、DECODER38和COMMAND)-【next】(add添加文件,三个实验项目分别设置文件名XOR2.vhd、DECODER38.vhd和COMMAND.vhd)-【properties】(检查文件类型type=VHDL)-【next】(三个项目都统一选择芯片类型family=Cyclone;name= EP1C3T100A8)-【next】-【finish】

(2).新建:【file】-【new】(选择VHDL File)-【OK】

2、写好源代码,保存文件(分别为XOR2.vhd、DECODER38.vhd和COMMAND.vhd)。

3、编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译,编译成功。

4、波形仿真及验证(包括功能仿真和时序仿真)。

新建一个vector waveform file。通过操作:右击 -【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】。接着设置输入波形,然后点击【start simulation】开始仿真,查看时序仿真输出波形图。

在【assignments】-【setting】-【simulator settings】-【simulation mode】中,将timing修改为functional,然后再点击【processing】- 【Generate Functional Simulation Netlist】成功后点击【start simulation】开始仿真,查看输出功能仿真波形图。

5、时序分析:选择【start classic timing analyzer】-在compilation report中选择【timing analysis】-【tpd】(查看引脚到引脚的延时)

6、查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

四、实验过程

(一)异或门的实现

-

编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

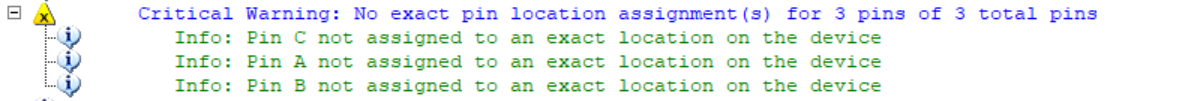

警告信息共两条:

c) RTL视图

d)结果分析及结论

程序正常通过编译,出现两则警告。第一则提示“定义的管脚没有和外部的管脚连接”,由于这次我们只用到仿真,不需要下载文件到板子上,因此暂时没有必要去分配管脚,可以不必理会。

第二则提示“尚未指定管脚的信号设置,默认将会接地”,解决办法:点击【assignments】-【device】-【device and pin options】-【unused pins】 ,设置为输入三态As input tri-stated,否则未用管脚的输出可能出错,修改后警告不复现。

2、波形仿真

- 波形仿真过程:插入A,B,C三个节点(A、B为输入节点,C为输出节点),设置输入波形,点击为A设置时钟信号period=200;offset=0,设置B period=200;offset=30,保存并对应仿真。

- 功能仿真波形图

c) 结果分析及结论

0-30ns:A=0,B=1,C=1;按异或门0⊕1=1正确;

30-60ns:A=0,B=0,C=0;按异或门0⊕0=0,正确;

60-90ns:A=1,B=0,C=1;按异或门1⊕0=1,正确;

90-120ns:A=1,B=1,C=0;按异或门1⊕1=0,正确;

d)时序仿真波形图

e)结果分析及结论

0-30ns:A=0,B=1,C=1;按异或门0⊕1=1正确;

30-40ns:A=0,B=0,C=1;按异或门0⊕0=0,但由于有时间延迟,反应慢了10ns。C显示的是0⊕1的情况;

40-60ns:A=0,B=0,C=0;按异或门0⊕0=0,正确;

60-70ns:A=1,B=0,C=0;按异或门1⊕0=1,但由于有时间延迟,反应慢了10ns。C显示的是0⊕0的情况;

70-90ns:A=1,B=0,C=1;按异或门1⊕0=1,正确;

90-100ns:A=1,B=1,C=0;按异或门1⊕1=0,但由于有时间延迟,反应慢了10ns。C显示的是1⊕0的情况;

100-120ns:A=1,B=1,C=0;按异或门1⊕1=0,正确;

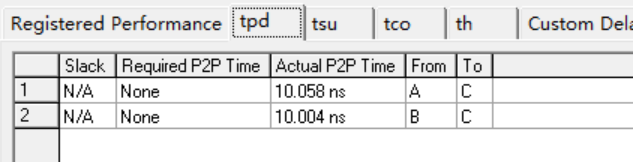

3.时序分析

a)时序分析图

b)结果分析及结论

A引脚到C引脚的实际p2p时间为10.058ns,B引脚到C引脚的实际p2p时间为10.004ns。两者时延相近,A比B慢0.054ns,结果是由时间长的决定,故整体为10.058ns。

(二)3-8译码器的实现

1.编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

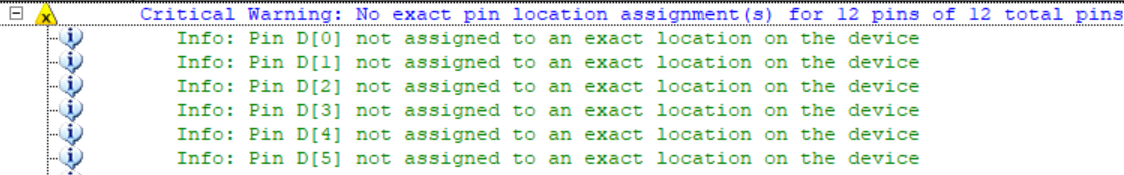

警告信息共一条,与前一个项目的警告类型相似:

c) RTL视图

d)结果分析及结论

程序正常通过编译,我采用的是直接对照最小值函数进行数据流方式的设计,从RTL电路原理图看出实际实现的电路原理是类似分层设计的样式。

2、波形仿真

- 波形仿真过程:插入A,B,C三个节点(A、B为输入节点,C为输出节点),设置输入波形,点击为A设置时钟信号period=60;offset=0,设置B period=120;offset=0,设置C period=240;offset=0,设置EN period=480;offset=0,保存并对应仿真。

功能仿真波形图

c) 结果分析及结论

0-240ns:EN=0;使能开关关闭,输出为00000000,正确;

(240-480ns:EN=1,使能开关开启)

240-270ns:A=0,B=0,C=0,EN=1;最小项函数A’B’C’,输出10000000,正确;

270-300ns:A=1,B=0,C=0,EN=1;最小项函数AB’C’,输出01000000,正确;

300-330ns:A=0,B=1,C=0,EN=1;最小项函数A’BC’,输出001000000,正确;

330-360ns:A=1,B=1,C=0,EN=1;最小项函数ABC’,输出00010000,正确;

360-390ns:A=0,B=0,C=1,EN=1;最小项函数A’B’C,输出00001000,正确;

390-420ns:A=1,B=0,C=1,EN=1;最小项函数AB’C,输出00000100,正确;

420-350ns:A=0,B=1,C=1,EN=1;最小项函数A’BC,输出00000010,正确;

450-480ns:A=1,B=1,C=1,EN=1;最小项函数ABC,输出00000001,正确;

d)时序仿真波形图

e)结果分析及结论

0-240ns:EN=0;使能开关关闭,输出为00000000,正确;

(240-480ns:EN=1,使能开关开启)

240-250ns:A=0,B=0,C=0,EN=1;最小项函数A’B’C’, 但由于有时间延迟,反应慢了约10ns,显示的是EN=0的情况;

250-270ns:A=0,B=0,C=0,EN=1;最小项函数A’B’C’,输出10000000,正确;

270-280ns:A=1,B=0,C=0,EN=1;最小项函数AB’C’,但由于有时间延迟,反应慢了约10ns,仍输出10000000;

280-300ns:A=1,B=0,C=0,EN=1;最小项函数AB’C’,输出01000000,正确;

300-310ns:A=0,B=1,C=0,EN=1;最小项函数A’BC’ ,但由于有时间延迟,反应慢了约10ns,仍输出01000000;

310-330ns:A=0,B=1,C=0,EN=1;最小项函数A’BC’,输出001000000,正确;

330-3400ns:A=1,B=1,C=0,EN=1;最小项函数ABC’ ,但由于有时间延迟,反应慢了约10ns,仍输出00100000;

340-360ns:A=1,B=1,C=0,EN=1;最小项函数ABC’,输出00010000,正确;

360-370ns:A=0,B=0,C=1,EN=1;最小项函数A’B’C,但由于有时间延迟,反应慢了约10ns,仍输出00010000;

370-390ns:A=0,B=0,C=1,EN=1;最小项函数A’B’C,输出00001000,正确;

390-400ns:A=1,B=0,C=1,EN=1;最小项函数AB’C,但由于有时间延迟,反应慢了约10ns,仍输出00001000;

400-420ns:A=1,B=0,C=1,EN=1;最小项函数AB’C,输出00000100,正确;

420-430ns:A=0,B=1,C=1,EN=1;最小项函数A’BC,但由于有时间延迟,反应慢了约10ns,仍输出00000100;

430-350ns:A=0,B=1,C=1,EN=1;最小项函数A’BC,输出00000010,正确;

450-460ns:A=1,B=1,C=1,EN=1;最小项函数ABC,但由于有时间延迟,反应慢了约10ns,仍输出00000010;

460-480ns:A=1,B=1,C=1,EN=1;最小项函数ABC,输出00000001,正确;

3.时序分析

a)时序分析图

……还有好几张图我就不放了

b)结果分析及结论

C引脚到D[5]引脚的实际p2p时间为12.185ns ,是所有引脚间tpd最长的,A引脚到D[6]引脚的实际p2p时间为10.813ns,时延最短。

(三)模型机指令译码器的实现

1.编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

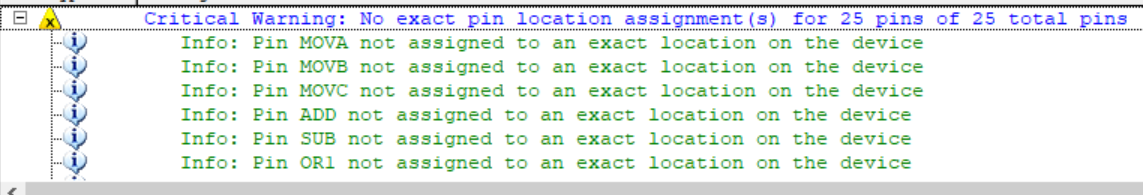

警告信息共一条,与前一个项目的警告类型相似:

c) RTL视图

d)结果分析及结论

程序正常通过编译,我采用数据流方式进行设计,利用与非运算判断寄存器类型R1、R2,利用与运算对应各个操作指令。

波形仿真

- 波形仿真过程:插入IR,EN,MOVA,MOVB,MOVC,ADD,SUB,OR1,NOT1,RSR,RSL,

JMP,JZ,JC,IN0,OUT0,NOP,HALT十八个节点(IR,EN为输入节点,其余为输出节点),设置输入波形,点击为EN设置时钟信号period=500;offset=0,设置IR为计数器,从00000000起8位2进制循环计数,保存并进行对应仿真。

b)功能仿真波形图与分析

限于篇幅,选取几个输出指令进行说明:

0-250ns,使能开关处于低电平0,所有指令输出均为0,正确

当IR输入为1111 0000、1111 0001、1111 0010、1111 0100、1111 0101、1111 010、1111 1000、1111 1001时,MOVA输出为1,正确;当IR输入为1111 1010时,MOVA理应输出1,但是此时使能开关为0,故输出0,正确。

当IR输入指令为1001 0000、 1001 0001、 10010010、 10010100、 1001 0101时,ADD输出为1,正确;当IR输入为1001 0110时,ADD理应输出1,但是此时使能开关为0,故输出0,正确。

当IR输入指令为1011 0000、 1011 0001、 10110010、 10110100、 1011 0101、1011 1000、1011 1001、1011 1010时,OR输出为1,正确;当IR输入为1011 0011、1011 0111时,不符合低两位编码为R2,OR输出0,正确。

c)时序仿真波形图及分析

限于篇幅,选取几个输出指令进行说明:

对于2.40us处 IR输入变为1111 0000,MOVA理应输出1,但是由于时间延迟,输出仍然是之前的状态0,在约16ns后的大致2.416us处才输出1。

同样,在2.43us处IR输入变为1111 0011,MOVA理应输出0,但是由于时间延迟,输出仍然是之前的状态1,在约12ns后的大致2.442us处才输出0。

同时我们看到,按照时间延时回推,在2.48us处IR由1111 0111转为1111 1000后MOVB、MOVA先后发生了一次冒险。

对于2.43us处IR输入变为1111 0011,MOVC理应输出1,但是由于时间延迟,输出仍然是之前的状态0,在约10ns后的2.44us处才输出1。

同样的,对于2.44us处IR输入变为1111 0100,MOVC理应输出0,但是由于时间延迟,输出仍然是之前的状态1,在约10ns后的2.45us处才输出0。

对于320ns处IR输入变为0010 0000,IN0理应输出1,但是由于时间延迟,输出仍然是之前的状态0,在约14ns后的334us处才输出1。

同样的,对于440ns处IR输入变为0010 1100,IN0理应输出0,但是由于时间延迟,输出仍然是之前的状态1,在约13ns后的453ns处才输出0。

我们看到,据时间延迟回推,大致在400ns处IR输入由0010 0111变为0010 1000时IN0发生了一次冒险。

3.时序分析

a)时序分析图

b)结果分析及结论

IR[4]引脚到MOVA引脚的实际p2p时间为16.734ns ,是所有引脚间tpd最长的;IR[0]引脚到JC引脚的实际p2p时间为8.290ns,时延最短。

五、实验结论

通过此次试验,我对QuartusII软件的基本操作有所熟悉,并对异或门、3-8译码器和模型机指令译码器的设计原理有了更加全面和细致的了解,在波形仿真过程中,我尝试使用多种仿真模型,学习并运用了各个波形变化的分析方法,提高了对数字电路与逻辑设计的整体理解,在后期试验中可以尝试使用更多不同的方法设计电路,并比较差异和不同,对时序分析的时延差异原理也应当进行更加具体的分析。

2063

2063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?