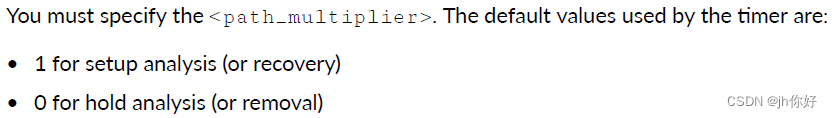

set_multicycle_path的语法:

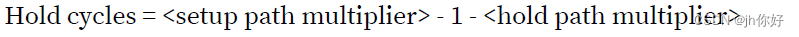

保持关系与建立关系相关联。 使用以下公式计算最常见情况下的保持周期数:

默认情况下, setup path multiplier 是用对应的目的时钟定义的.要修改有关源时钟的setup需求,使用 -start 选项。

同样的,hold path multiplier 是用对应的源时钟定义的,要修改有关目的时钟的hold需求,使用 -end 选项。

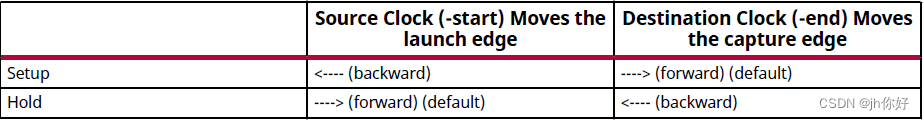

默认情况下:setup path对应的计算起点是目的时钟,向前(从左到右)移动。

----- 对应的:hold path对应的计算起点是源时钟,向后(从右到左)。

在同一时钟域下,选项-end和-start没有啥区别。

约束前

约束后:

setup check第二个capture沿,hold check自动移到第一个capture沿。默认情况下hold自动在setup的前一个周期。

设置命令:

Relaxing Setup While Maintaining Hold

-end选项用于让hold相对于capture沿向后(backward)移动一个周期。

对于一个setup是4周期的约束:

下面是一个hold不加-end的例子:

由于需要四周期保持时间,时序驱动的实现工具通常必须在数据路径中插入大量延迟,以满足慢速和快速时序角的保持时序。这会导致不必要的面积和功耗。因此,尽可能放宽保持要求非常重要。

不加-end,属于默认情况,hold相对于源时钟向后移动4个周期。

由于源时钟和目的时钟相同,所以图5-9和图5-10等价。

波形相同,但是相位偏移的两时钟域:

默认情况下timing tool识别到的关系:

慢时钟域到快时钟域的multicycles:

STA tool将按照下面的关系分析:

经过上面设置第一种multicycle之后:

经过上面设置第二种multicycle之后:

上面的设置如果不加-end,hold将沿着发射沿向前(从左到右)移动2个周期,加上-end后hold沿着capture向后(从右往左)移动2个周期。

对于慢时钟域到快时钟域,当setup multicycle设置为N时,hold相应的应该设置为N-1(选-end),如下:

***快时钟域到慢时钟域的multicycles:

两时钟之间的关系:

STA TOOL识别出的两者的关系:

设置setup和hold的multicycle:

setup选-start,表示setup check沿着发射沿向后(从右向左)移动3-1个周期。hold check从setup check沿着发射沿(默认)向前(从左向右)移动1+2个周期。

对于慢时钟域到快时钟域,当setup(选-start) multicycle设置为N时,hold相应的应该设置为N-1,如下:

其他情况:

set_multicycle_path 6 -setup -to [get_pins C_reg[*]/D]

这条命令设置了所有的前级寄存器时钟端口到C_reg寄存器的D端口路径都是多时钟周期路径,且都是6个周期。通过这条命令告诉工具,仅仅在第六个时钟周期进行建立分析。而set_multicycle_path 6 -setup -from A_reg/Clk -to [get_pins C_reg[*]/D],则是仅仅现在从A寄存器的时钟端口到C_reg寄存D端口的这一条路径而已。

这时允许的最大延迟时间为:60 - Tsu - Tuncertainty - Tco

从前面分析所知:保持时间的分析在建立分析的前一个周期,但是从默认这里开始分析保持时间会出问题,一般都是从发送沿开始分析。所以要从0时刻开始分析。因此:

hold时序分析:

data arrival time > data required time —— —— 目标时钟的上升沿在源时钟之后(右边)

data arrival time < data required time —— —— 目标时钟的上升沿在源时钟之前(左边)

multiple设置之前可以先查看原始的PT时序中hold与setup的关系 ,确定默认的地点位置和终点位置

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?