4.边耦合器在垂直方向上的结构

4.1. 多个上波导的边耦合器

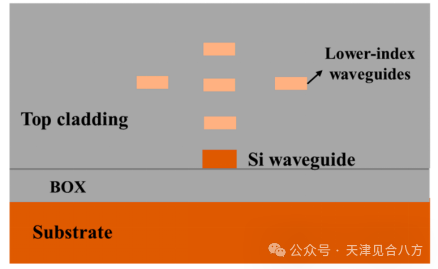

典型的硅光子集成电路基于SOI平台,其由厚的硅衬底、BOX层(用于隔离的埋入式二氧化硅)、光路层和包层(用于自下而上保护的顶部二氧化硅)组成。可以改变BOX层和包层的垂直尺寸,以提高器件性能。对于光纤到芯片边耦合器的垂直结构设计,主要是为了在垂直方向上扩大有效模式面积,以实现光纤和耦合器之间的高模式匹配。图10显示了一种获得大有效模式面积的方法,多个波导放置在硅倒锥波导上方[74,75]。上辅助波导通常由折射率低于硅的材料制成,如氮化硅(SiN)和氮氧化硅(SiON),这些材料与典型的硅光子平台和CMOS制造工艺很好地兼容。图10展示了一种引入辅助多波导的模式[76],原则上,辅助波导应放置在倒锥上方,以便分布在窄锥形外部的传播模式可以向上传输和约束。由于存在折射率高于周围二氧化硅包层的上辅助波导,光往往被限制在多个辅助波导中。因此,下硅倒锥与上辅助波导一起支持叠加模式,模式面积变大,与光纤芯的面积相当,这有助于有效地与光纤耦合。

从技术上讲,可以通过改变辅助波导的数量、材料折射率和方向来控制最终的模式分布,Voigt等人讨论了具有不同图案的辅助波导的性能[76]。考虑到制造问题,因为它们与硅光子制造工艺非常兼容,因此制作多个SiN或SiON波导是可行的。然而,应注意对齐以达到预期性能,并且在沉积每一层时需要仔细设计对齐标记。通常,应该考虑一下几种情况下的对齐问题。首先,上辅助波导需要与硅倒锥横向对齐,以确保适当的模式分布和转换;其次,由于辅助波导位于不同的高度(或不同的层),应实现层间对准以获得所需的波导图案;最后,在硅倒锥内形成叠加模式,因此,辅助波导也应沉积在锥形部分上方并纵向对齐,以促进向上模式过渡。

图10. 多波导辅助硅倒锥形(横截面图)

[75]中展示了一种新型的模斑尺寸转换器,该转换器由多个上部SiON波导组成,用于与标准单模光纤耦合。这种模斑转换器总长度450um,耦合损耗可低至0.4dB。单模光纤的1dB对准容差大于2um,而3dB对准容差接近4 um,这种新颖的设计降低了单模光纤对准和固定到光子芯片的复杂性,但对制造可行性来说是相当具有挑战性。

4.2. 级联多级锥的边耦合器

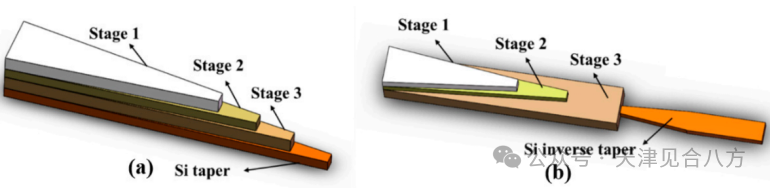

上一节展示了一种通过在具有SiO2隔离层的硅倒锥上方生长的辅助波导实现的边耦合器在垂直方向上的结构。因此,通过级联锥体实现传播模式的垂直过渡也是可行的,如图11所示。基于多级锥体的边耦合器由不同层中的多个单向锥体组成,其宽端靠近光纤,窄端靠近连续的光子波导。在宽端,不同层的锥形融合,从而使边耦合器具有与光纤芯相当的大横截面积,光可以较好的耦合进耦合器。在多级锥体区域,顶层锥体长度最短,而底层锥体长度最长。当光在级联的多级锥中传播并到达顶层锥末尖端时,由于横截面积太小,光不能很好地约束在顶层中,并且它倾向于透射到下面的连续层中(该层的折射率高于周围的SiO2包层)。同样的,光在第二层锥体中传播一定距离,然后在传播到第二锥尖端时继续向下传输,直到到达底层,其中底层与硅波导连接。

关于每一层的材料,它可以是硅、氧化硅、氮化硅或其他具有适当折射率和兼容性的聚合物。基于级联多级锥体的边耦合器根据以下机制可分为两种主要类型。在图11a所示的第一种类型下,硅锥作为底层,与上层沿同一方向级联,宽端靠近光纤,窄端与光子波导连接[77-79],在每一层中,光首先以完全支撑模式存在,当它传播到窄锥端时,模式会过渡到尺寸较长的下层,最后,该模式可以传输到底部硅器件层,并进入光子光路中传播。至于图 11b 所示的第二种类型,在底层埋入硅倒锥以实现模式转换 [80–82],上层的结构和机制在两种类型中是相同的,然而,在倒锥形上方的级联多级锥形类型中,底层的长方体形状不同,实际上充当等效的包层。一个关键的设计原则是,底层的折射率应该比硅低,这样模式才能转换为埋入硅倒锥形,然后是硅光子波导。

图 11.两种多级锥(a) 正锥和 (b)倒锥。

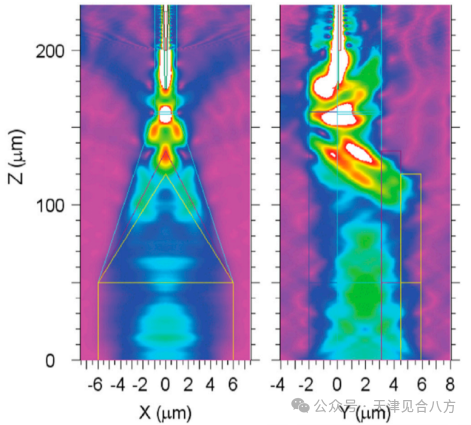

图 12 介绍了在硅倒锥形埋入底层的的级联多级模式转换器中的模式分布 [82]。这种配置有三个 SiO2级,黄色锥形包络代表第一级,而蓝色锥形包络代表最后一级。在图 12 的右侧,它显示了光场在每层之间向下传输。这种光纤-波导模式转换器在约 200 μm 的总长度内具有 1.5 dB 的低损耗和 100nm的1 dB 的带宽。在多级上波导的辅助下,该耦合器可以直接与 1550 nm 工作波长附近的单模光纤耦合。采用多种(超过五种)光刻和蚀刻工艺形成 Si 和 SiO2 锥形,并在每次沉积之前应用化学机械抛光(CMP)。在此设计中光纤水平和垂直方向上超出 1 dB 的对准公差分别为 2.5 μm 和 2 μm。

图 12.在图9b所示条件下,多级边耦合器中模拟的光场分布。(左)模态分布的顶视图;(右)模态分布的侧视图。

级联多级边耦合器中的级数不受限制但应适当,过多的层会增加制造复杂性,而太少的层可能会导致模式转换到硅层的模式不足,通常,使用3~5层边耦合器。制造过程的复杂性取决于使用多少阶段,因为需要光刻、蚀刻和抛光来准备每层的锥形结构。此外,每层锥形的侧壁粗糙度也会导致耦合效率的过度损失[83‒87]。应考虑层间锥尖对齐,并且需要在传统的 SOI 结构上生长较厚的包层,以减少与纤芯的模式尺寸不匹配。总而言之,多级边耦合器的制造与典型的 CMOS 工艺兼容,主要工艺包括光刻、蚀刻、沉积和抛光。然而,由于存在多个阶段,制造可能非常复杂和耗时,这限制其广泛应用。在使用单模光纤的研究应用场景中,这种配置是合适的,因为它的光斑尺寸大、模式失配低、对准容差高。

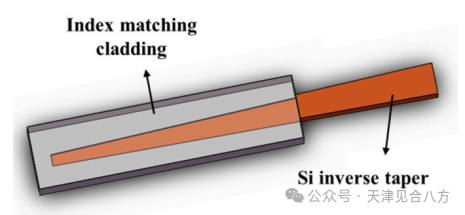

4.3. 折射率匹配包层的边耦合器

除了基于级联多级锥形的边耦合器外,还有一些关于埋在折射率匹配薄层中的硅倒锥边耦合器的研究工作[88–95]。图 13 显示了由折射率匹配包层辅助的边耦合器的典型结构,我们可以观察到,与 SiO2 包层下方的 Si 层不同,包括 SiN、SiON 和聚合物在内的其他种类的材料被用来设计光纤纤芯和硅波导值之间的折射率。在某些情况下,在硅波导和顶部折射率匹配包层之间可能有一个额外的中间层。Lee等人应用了两种聚合物的组合,即具有较高折射率的WIR30-490作为顶部包层,ZPU450作为与硅锥形连接的次级波导[88]。Pu等人减少了SiO2包层的厚度,并设计了一个厚的聚合物波导作为其顶部包层[89]。Bakir等人在典型二氧化硅的基础上进行了调整,并用折射率更高的氧化物(约为1.6)代替了二氧化硅[90]。Raghunathan等人使用化学气相沉积,在非晶硅芯顶部形成聚合物包层[91]。Ku 等人设计了一种由 SU-8 三维锥形和氮氧化硅中间体组成的结构。SiON 沉积在硅波导周围,可以逐渐将光从 SU-8 三维 锥形传输到底层硅层 [92]。Jia 等人使用了由 SiON 制成的中间层,该中间层围绕着 Si 核,并被 SiO2 顶部包层包围。在这种结构中,SiON 中间层可以被视为围绕 Si 波导的二级芯 [93],Takei 等人与 Jia在[93] 种的设计相似。其中使用SiON作为过渡材料,并作为耦合器中的次级核心[94]。Maegami 等人设计了一种 SiO2 垫片来隔离 Si 锥形和 SiON 层,Si 锥形是刀形的,侧壁是倾斜的 [95]。

图 13.在与折射率匹配包层的中的硅锥形示意图

在[89]中,由于 Si 倒锥形的尖端宽度较窄(约 40 nm),EBL 被施加在 SOI 晶圆上形成 Si 锥形,并施加热氧化以在 Si 锥形上生长具有 30 nm 厚度的 SiO2 薄层。SU8 聚合物的顶部包层在SiO2薄层上旋涂,然后用 EBL 图案化。Si、SiO2 和 SU-8 层的厚度组成经过精细优化,使模式转换器中的有效折射率接近耦合光纤的有效折射率。在 300 μm 长的基底面中实现了TM 模以约 0.36 dB 的超低损耗,垂直和水平方向上 1.5 μm 错位有额外 3 dB 损耗。借助与适当厚度的包层匹配的折射率,可以直接增加纤芯和光子波导之间在尺寸和有效折射率方面的模式重叠。折射率匹配层的制造过程比前面几节中提到的具有多个辅助波导和多级锥形的边耦合器的制造过程更简单。一个先决条件是确定适当种类的折射率匹配材料或根据折射率值的要求合成特定类型的材料。理论上,匹配包层的折射率应接近纤芯的折射率,以减少折射率失配。光学光刻或电子束光刻的选择取决于整个构型中的特征尺寸,通常为锥形尖端宽度。考虑到仅使用一个锥形及其较窄的尖端宽度,光斑尺寸通常比标准单模光纤小得多(约 3 μm)。因此,带有折射率匹配包层的边耦合器特别适用于与透镜光纤或光斑尺寸被压缩的高数值孔径 (HNA) 光纤耦合。

4.4. 基于三维锥的边耦合器

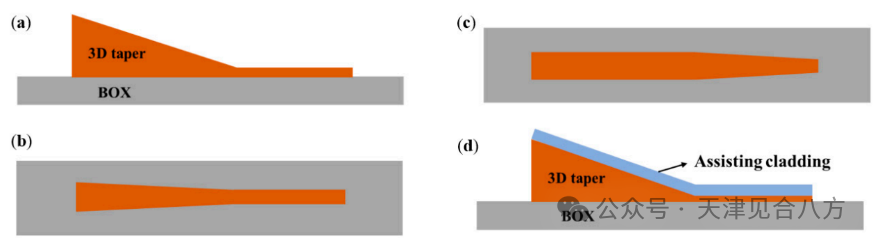

典型的锥形仅在纵向和横向维度上具有锥形轮廓,而锥形的厚度保持不变。但是,可以通过可以逐渐收敛的三维锥形传输来自光纤的光。如图 14a 所示,三维锥形宽端与光纤对齐,其结构尺寸方面与光纤纤芯相当。然后,它开始在垂直和水平方向上逐渐变细,以与硅波导连接。通常,三维锥形可分为两种主要类型:一种是纯硅基三维锥形,另一种是其他中间材料辅助的三维锥形。关于纯硅基三维锥形 [96‒99],也有两种不同的方法来调整三维轮廓。在以前的一些工作中[96,99],锥形的宽端在垂直和横向上都变得更窄,直到形成与硅波导具有相同厚度和宽度的窄端,如图14b所示。在其他一些作品中[97,98],3D锥形首先开始减少厚度,而宽度保持不变。然后三维锥形过渡到与硅波导厚度相同的薄硅板,然后横向板逐渐变细,类似于传统的二维锥形,然后与硅波导连接,如图 14c 所示。

图 14.(a) 硅三维锥(侧视);(b) 和 (c) 两种类型的三维锥形轮廓(俯视);(d)其他材料辅助的三维锥

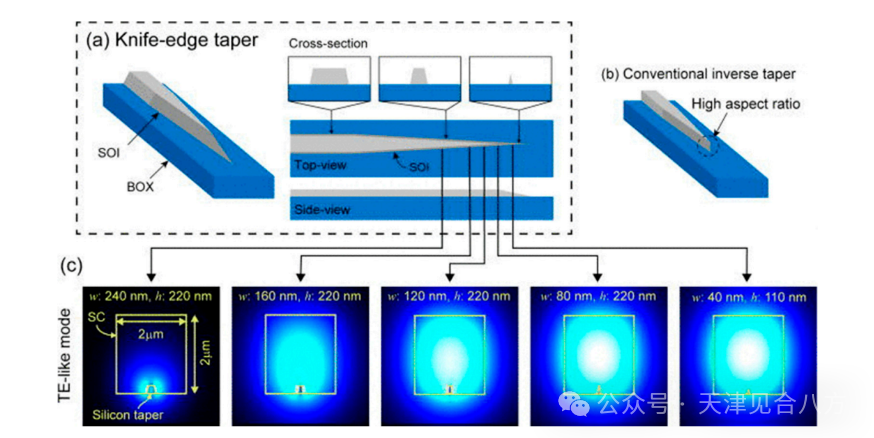

还有一些三维锥形由其他材料辅助,以与光纤纤芯匹配,同时考虑尺寸和有效折射率的匹配,如图 14d 所示。在这种情况下,应用了非晶硅 [100,101]、SU-8 [92,102]、SiON [92] 和其他类型的折射率匹配材料。这些材料与硅光子平台兼容,并且在硅之间具有适中的折射率二氧化硅和硅,这可以帮助改善光纤和波导之间的模式匹配。图 15a 展示了一种遵循图 14b 中描述的状态的刀刃三维锥形耦合器。与图 15b 中的传统倒锥形相比,其锥形尖端经过专门设计,纵横比较低。i线步进器用于制作图案,硅锥形通过电感耦合器等离子反应离子蚀刻 (ICP-RIE) 制备,以形成倾斜的侧壁。然后,在 CF4 气环境中中进行干法蚀刻。引入由苯并环丁烯制成的次级芯来设计折射率,并保护功能性硅波导在蚀刻过程中免受 CF4 的暴露。在实际测量中,窄刀口形状的尖端与光纤对齐。对于图 15c 中所示的 TE 模式转换,很明显当光在锥形内传播时,模式的限制越来越强。对于此配置,TE 模式转换损耗为 0.35 dB,器件尺寸为 180 μm。

图 15(a)刀锥形的示意图;(b) 传统的倒锥形;(c) TE 模的模式分布

虽然可以用三维锥连接大型纤芯,但考虑到制造工艺,三维锥并不容易。在上述研究工作中,多种制造技术被用于制作三维锥,包括灰调光刻 [96]、用于倾斜表面的 KOH 湿法蚀刻 [97]、阴影掩模 [100]、在氢环境温度下退火 [101] 等。这些制造过程在一定程度上难以操作和控制,因此,它们限制了三维锥形的适应性和实用性。换句话说,理想的三维锥形的设计确实是一个制造技术的问题。必须准确、精确地控制反应速度和反应物剂量,以达到所需的垂直锥形斜率,并避免厚楔形塌陷。

4.5. 基于悬臂结构的边耦合器

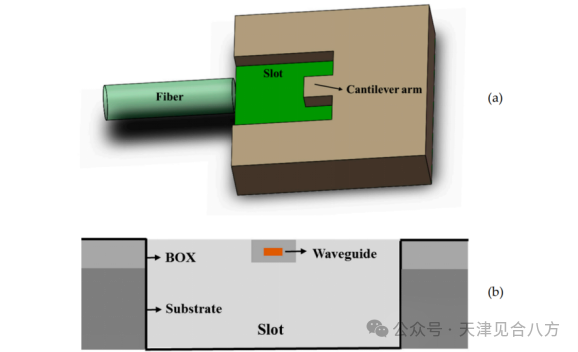

在前面的部分中已经描述了边耦合器的几种垂直变化形式,包括由多个波导辅助的耦合器、基于级联多级锥形的耦合器、具有折射率匹配包层的耦合器和基于三维锥形的耦合器。基本上,这些边耦合器都是基于硅倒锥形上设计额外结构。典型的 SOI 晶圆使用厚硅作为衬底,并生长一层厚度为几微米的二氧化硅作为掩埋氧化层,以将器件层与衬底隔离开来。同样的,也适用于设计硅倒锥形之下的结构。悬臂结构通常是用MEMS,它们在边耦合器设计中也发挥着重要作用[103–107],这种结构的示意图如图 16 所示。它基于初始单硅倒锥形,将 BOX 层和 BOX 层下方的衬底部分切至一定厚度,并露出SiO2 的 Si 锥形悬梁。设置了几根支撑梁来支撑悬臂,以实现结构稳定性。将光纤放置在蚀刻槽中,并与悬臂的劈裂面对齐。

图 16.(a) 悬臂式边耦合器的典型结构;(b) 悬臂的横截面。

详细的工艺流程见 [103],该转换器由悬浮的 SiO2 波导和重叠的 Si 锥形组成。这种新颖的设计在 1520 至 1600 nm 的宽波长范围内使用 5 μm-MFD 透镜光纤时,耦合损耗约为 2.0 dB。对准公差的 1 dB 超额损耗约为 1.7 μm。该器件具有相当大面积,长度为 550 μm。总体而言,这种悬臂式边耦合器以尺寸过长为代价实现了较好的耦合性能。但制造过程的复杂性和难度使这种配置与其他耦合器相比竞争力较低,而其他耦合器可以在更容易的制造下实现类似的性能。尽管如此,悬臂结构实际上是一种新颖而巧妙的设计。一方面,蚀刻后留下的底切槽可以进一步将功能结构与具有高折射率的 Si 衬底隔离开来,并且可以显著减少进入 Si 衬底的模式泄漏。在某些情况下,在悬臂下方的槽中填充折射率匹配油,以进一步减少纤维头和耦合器之间的折射率不匹配[31]。从另一个侧面看,剩余的悬臂与光纤相似[104],也就是说,悬挂臂本身充当等效芯,蚀刻槽中的环绕中间体充当等效包层。这种相似结构有助于高效耦合。

设计悬臂式边耦合器的主要障碍是复杂的制造工艺,因为制造悬臂结构非常具有挑战性。需要多个光刻和刻蚀步骤才能依次获得悬臂和深沟槽。此外,应精确设计和调整图案掩模,以控制悬臂的尺寸。这些限制使得悬臂式边耦合器难以进行大规模生产。然而,悬臂式边耦合器的精细结构有助于在研究场景中利用更高的器件性能。它还有可能将悬臂边耦合器与MEMS 集成,这可能会激发新型光子器件和集成系统的灵感。

总之,对于具有垂直结构的边耦合器,制造过程通常比水平结构的设计更复杂且不可行,单片制造工艺与平面光子集成电路更兼容。此外,硅衬底或标准 SOI 晶圆的包层的过度制造将导致高成本和较差的集成性。

790

790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?