下面的答案仅仅是参考:有任何错误,欢迎私信,留言。

1:D

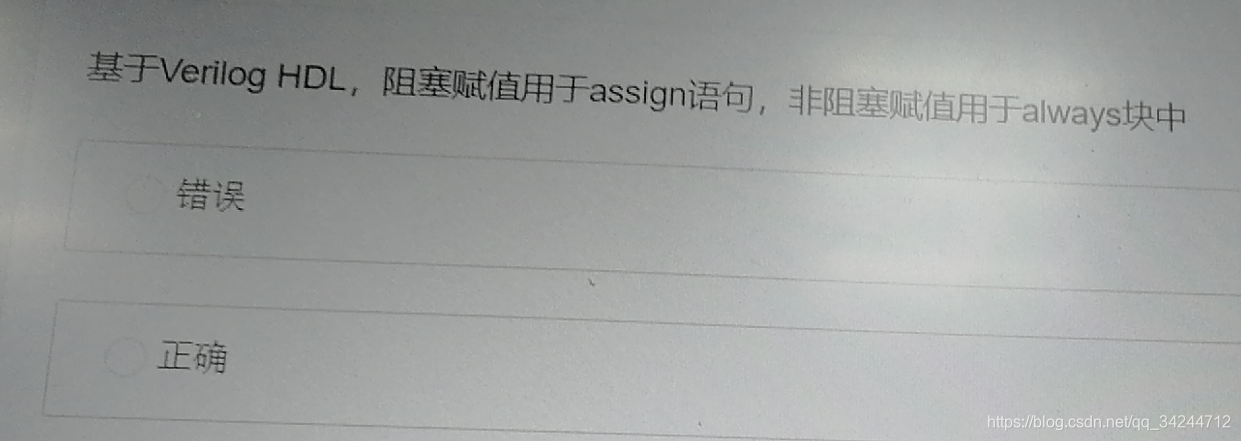

阻塞赋值“=”(组合逻辑电路),非阻塞赋值“<=”(时序逻辑电路)

2.正确

时序逻辑电路的定义:

3.错误吧,阻塞赋值在always 也可以用

4.选2

5选C

有些时候,设计中可以使用Latch。异步复位不插入组合逻辑,是防止产生更多的毛刺信号

6.选C

7选C

8.A:cnt

9正确:没看懂

10选B

moore的输出只和当前状态有关。

mealy的输出和当前状态和输入都有关

11.最早到达

12.D

always 中赋值必须是reg

初学verilog的同学们,可能潜意识就认为一个reg对应一个触发器,其实不然。

我们先看一个例子:

1 `timescale 1ns/100ps

2

3 module prj_1(

4 input b1,b2,

5 output reg a1,a2

6 );

7

8 always@(*) begin

9 #5 a1 = b1;

10 end

11

12 always@(*) begin

13 a2 = #5 b2;

14 end

15 endmodule

由于always模块要求赋值左端都是reg类型,所以定义a1、a2均为reg类型。

注意,第8行,敏感列表是"*",*号代替了本always模块里面所有的触发信号。

查看其RTL电路图,会发现是这样的

可以看到,设计的电路是一个纯粹的组合逻辑电路,不会综合出DFF。为什么会这样呢?

以下是verilog-2001的标准中对wire和reg的定义如下:

wire:

A wire net can be used for nets that are driven by a single gate or continuous assignment.

reg:

Assignments to a reg are made by procedural assignments (see 6.2 and 9.2). Since the reg holds a value between assignments, it can be used to model hardware registers. Edge-sensitive (i.e., flip-flops) and level sensitive (i.e., RS and transparent latches) storage elements can be modeled. A reg needs not represent a hardware storage element since it can also be used to represent combinatorial logic.

这段话的意思是:在过程赋值语句中,表达式右侧的计算结果在某种条件的触发下放到一个变量当中,而这个变量可以声明成reg类型的。根据触发条件的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

也就是说,综合出触发器的条件是,需要有时钟的沿触发。

13.A

14正确

15C:

16.B

17A:门电路

18.A

19.正确:

20.C

21

22.没看懂

23.2^n

24.选A

25.A

26.C

27.选B

相对而言,异步电路的速度可以比较好的适应变化的温度和电压条件,而不是必须考虑最坏情况。换句话说,如果温度,电压等条件发生变化,导致电路延时变大,异步电路本身就可以适应这种变化,“自动”降低速度,而不会发生功能的错误

28.选C

29.错误

30.选A

A+A`B=A+B

31.B

32.ABCD

33.ABCD

34.A B C D

35.ABCDEF

36.ABCD

37.16片

38.A:0,0

39.错误。应该是最小时间

40.错误:定义了32个位宽为256bit的数组

41选D:芯片面积

42.D:不确定

43正确

44错误

45.错误(看不懂)

46.X=4

47.

48错误

49错误

50.正确

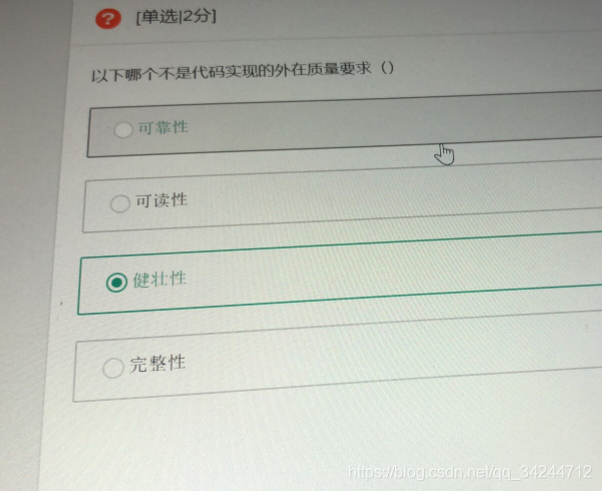

51.B:可读性

52C:!

53.正确

54错误

1、Moore型状态机:下一状态只由当前状态决定,

2、Mealy 型状态机:下一状态不但与当前状态有关,还与当前输入值有关

55.门电路

56.正确

57正确

58选C:

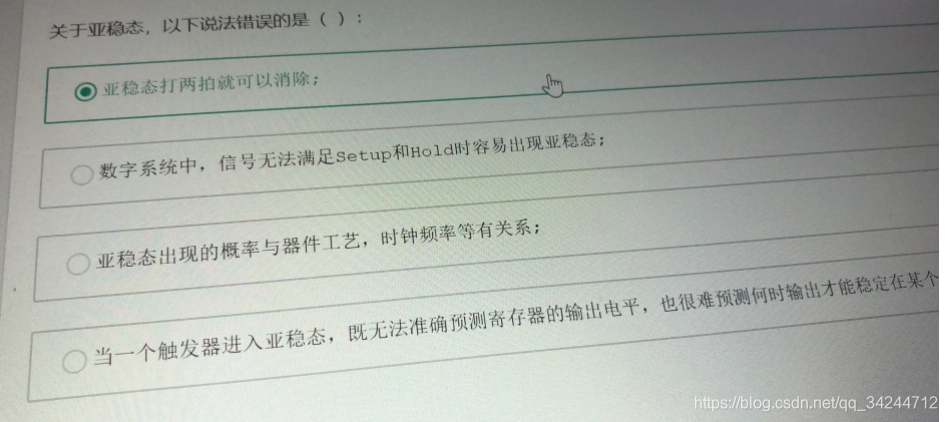

59.A:就可以消除,太绝对了。

2681

2681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?