一个高速信号SerDes通道(例如PCIe、112G/224G-PAM4)包含了这些片段:

- 传输线

- 连通孔(PTH or B/B via)

- 连接器

- 高速Cable

- 锡球(Ball and Bump)

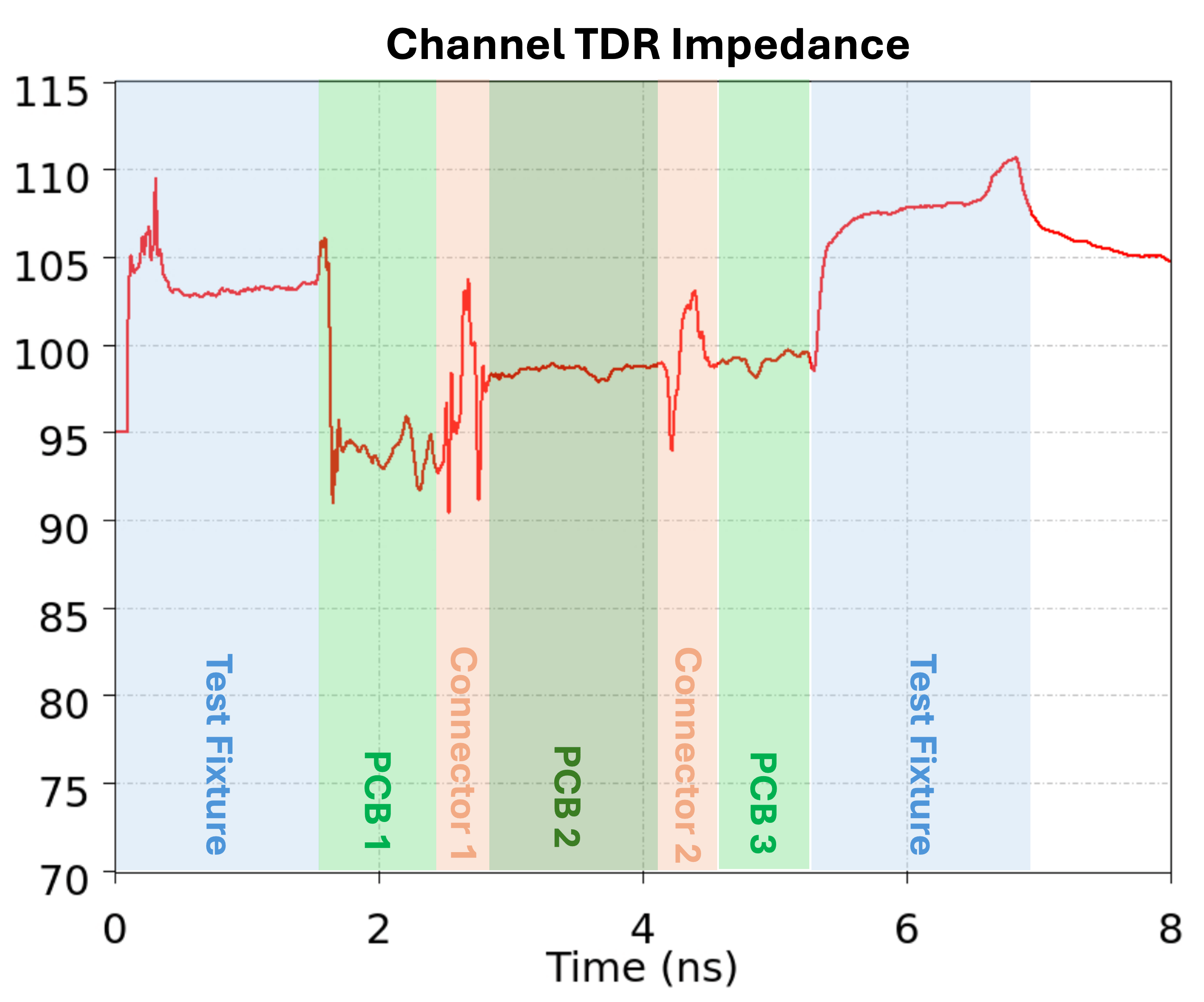

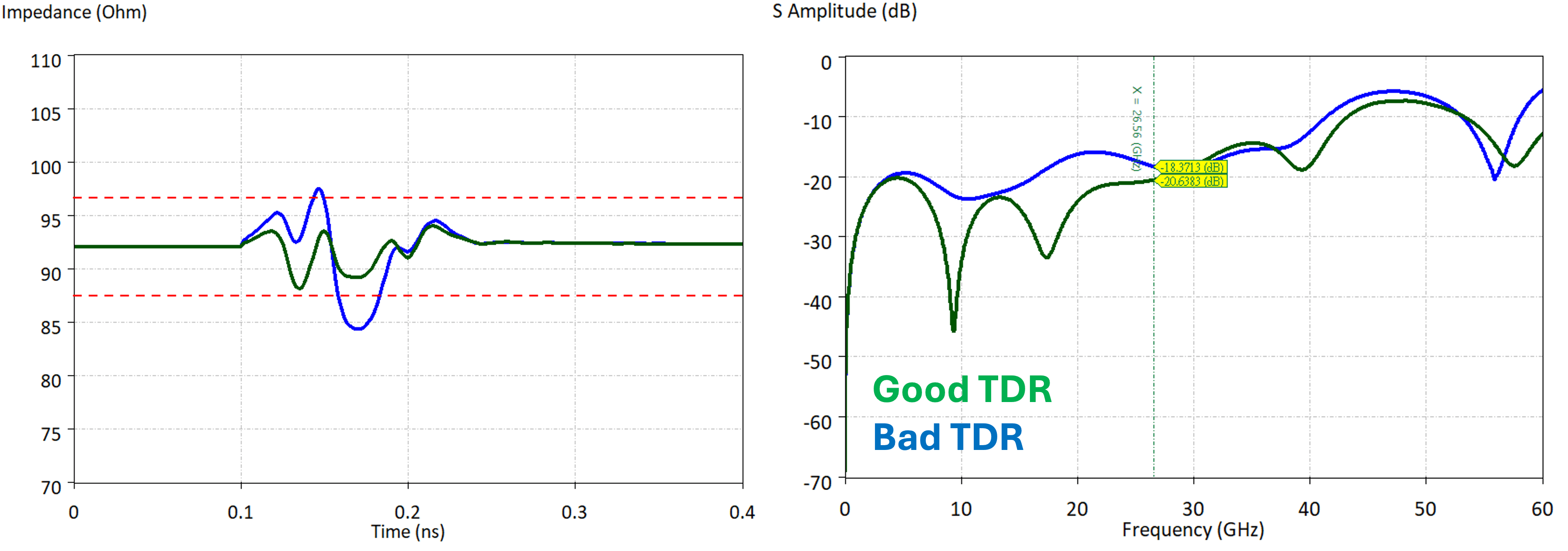

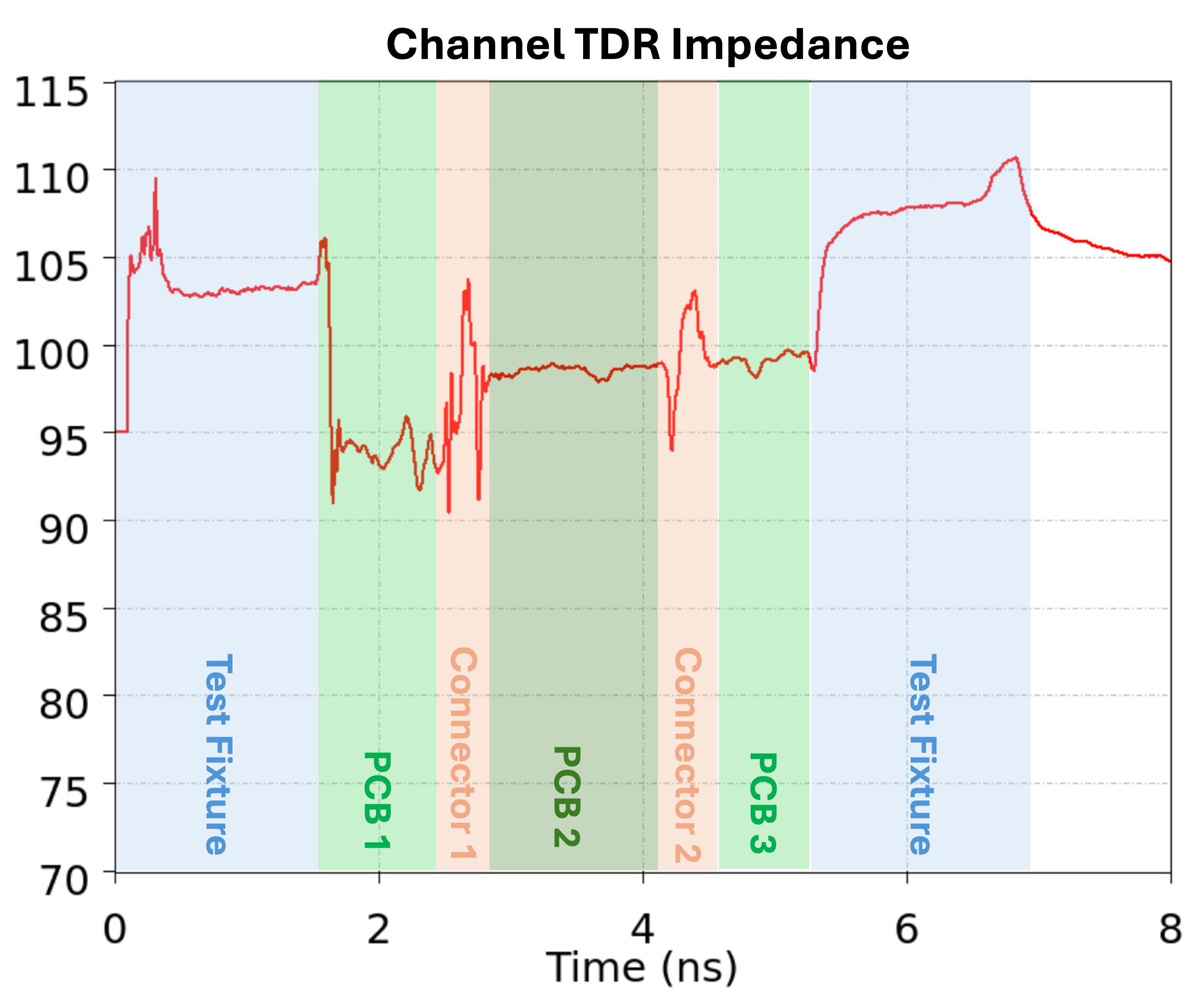

我们会希望所有的片段都可以有一致的阻抗,以求讯号不会有太多的反射。 可是事实是这些片段有着自己本身结构的问题,要完全达到相同的阻抗设计难度是不可能的,我们能做的只有尽量去减少阻抗的跳动。 例如下面这张TDR图,设计阻抗在95Ohm,扣除test fixture外,我们控制阻抗在95上下10%,这样通道的SI特性才会好!

PCB阻抗匹配

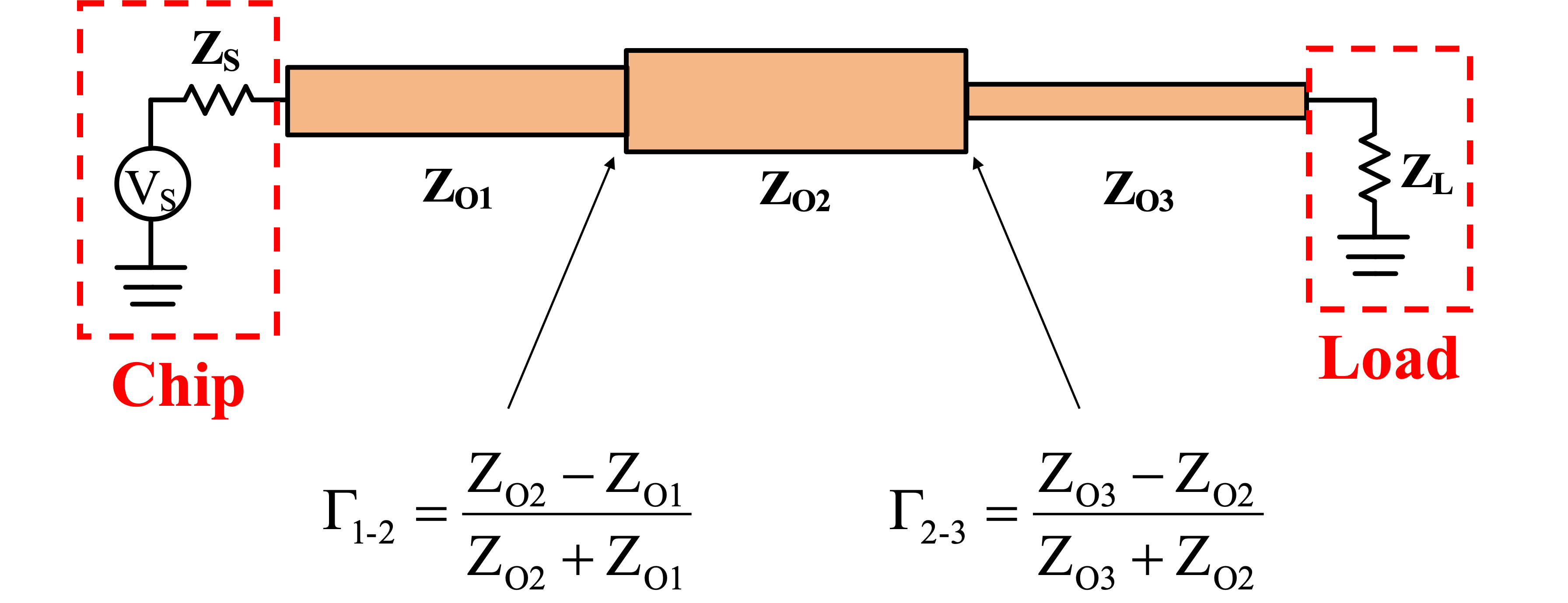

通道的每个片段都有其阻抗,这些阻抗都应该要接近芯片IP的内部阻抗,比如PCIe=85Ohm、112G SerDes=100Ohm,我们将其称作阻抗匹配。 一个阻抗匹配的通道(或者说是Transparent Channel),通道的反射是很低的,反射系数会趋近于0,系统SI工程师理应寻求管道将通道阻抗控制在一定的范围内。

我们每天在做的就是找到方法降低反射系数,反射系数越低,则return loss越好,整体SI性能也会提升!

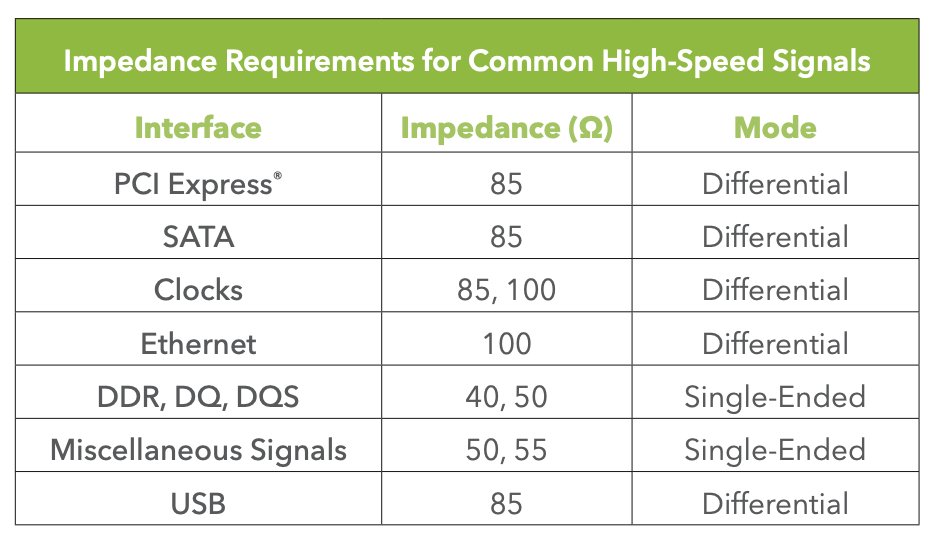

每个高速讯号通道都会有自己的阻抗要求,例如PCIe为85Ohm,网络讯号SerDes为100Ohm(现在大多设计在90~95Ohm)。

传输线与连通孔的阻抗匹配

对于PCB设计者而言,主要关注以下两者:

1. 传输线的阻抗控制

a. 根据不同介质厚度,计算差动对的线宽、线距以满足阻抗条件。 (我们在这里介绍过如何分析)

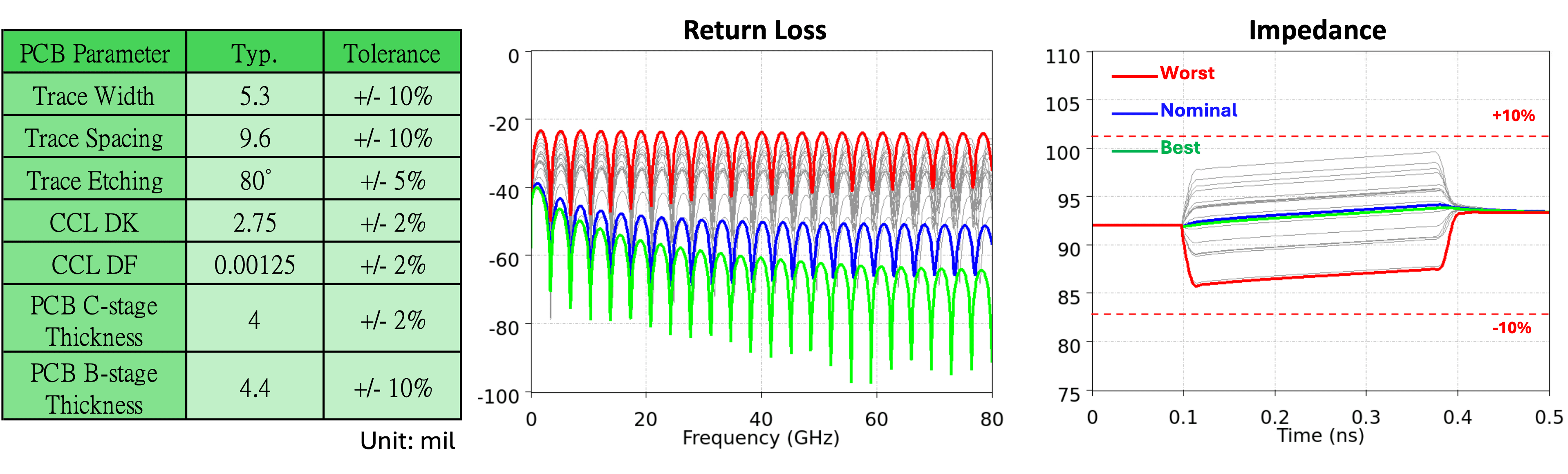

b. 考量PCB制程误差,例如材料DK、PCB蚀刻条件。 以往要在设计端分析制程误差是很费力费时的,假设有7个变量,每个变数有10个点要分析,排列组合下,就会有7^{10}个组合,一个模拟假设1小时,我想应该不用算需要多少时间了吧? AI的出现解决了这个问题,现在许多EDA供应商都有推出其AI的版本,例如Cadence有一套Optimality,软件会边跑模拟边判断参数是否收敛,是否需要跑完所有case,整个模拟跑完一轮,花不到半天,时间变得超级省!

极力建议大家要做这些分析,设计端先将这些误差考虑进去,可以大大减少后续Debug的时间,产品在量产时的可靠度也才会提高!

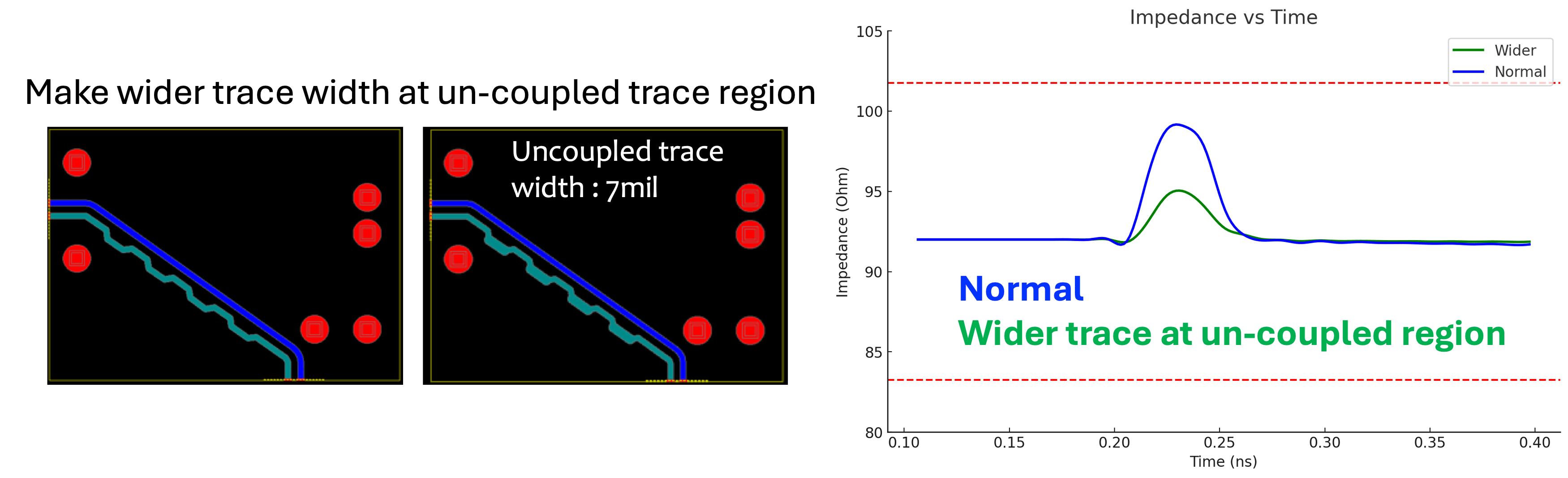

c. 仔细注意设计细节,很多时候一个小小的细节会影响一锅粥。 例如差动对的PN长度差异,现在224G的要求已经低到0.5~1mil,难免会有许多所谓的tune线,这些tune线使得线距变宽,阻抗随之会有变化,透过EM solver我们可以知道tune线区域的阻抗为何,并且针对这个区域给些solution,阻抗就可以很好地被控制!

2. 连通孔Via的阻抗控制

a. 使用3D EM Solver (例如Cadence Clarity)萃取阻抗,并控制阻抗在可被允许的范围内(5~10%)。

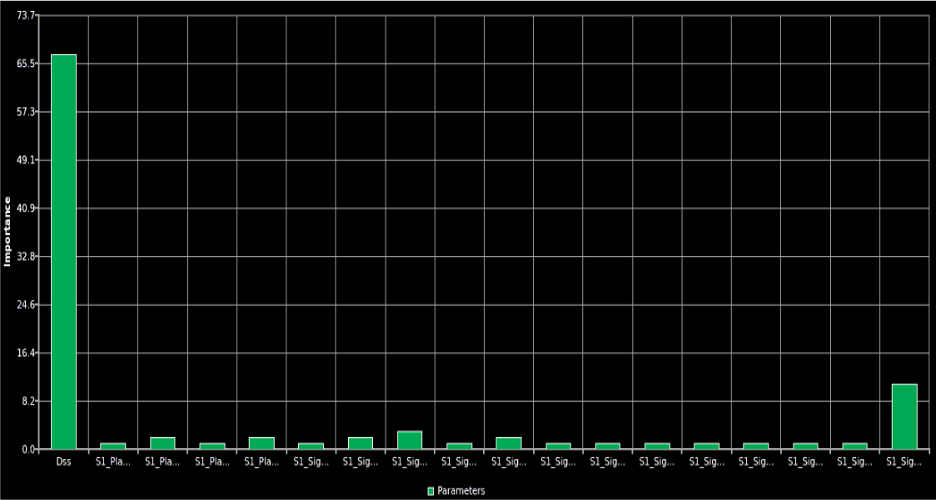

b. 与传输线类似,模拟PCB制程变异对于Via阻抗的影响,尝试找出Worst case。 我们也可以利用Cadence Optimality找出在这么多的工艺变量中,哪几个变量对于Via阻抗比较敏感。 像下面这个分析,就是Dss(PN两个Via的间距)对于阻抗最为敏感,换句话说,这个参数的变动很容易造成阻抗的剧烈变化,这是因为这个Via设计在强耦合的条件,如果我们将其改为弱耦合(增加间距),敏感性就会降低,对于阻抗的控制上也会较好!

ERL – 将反射损耗数值化

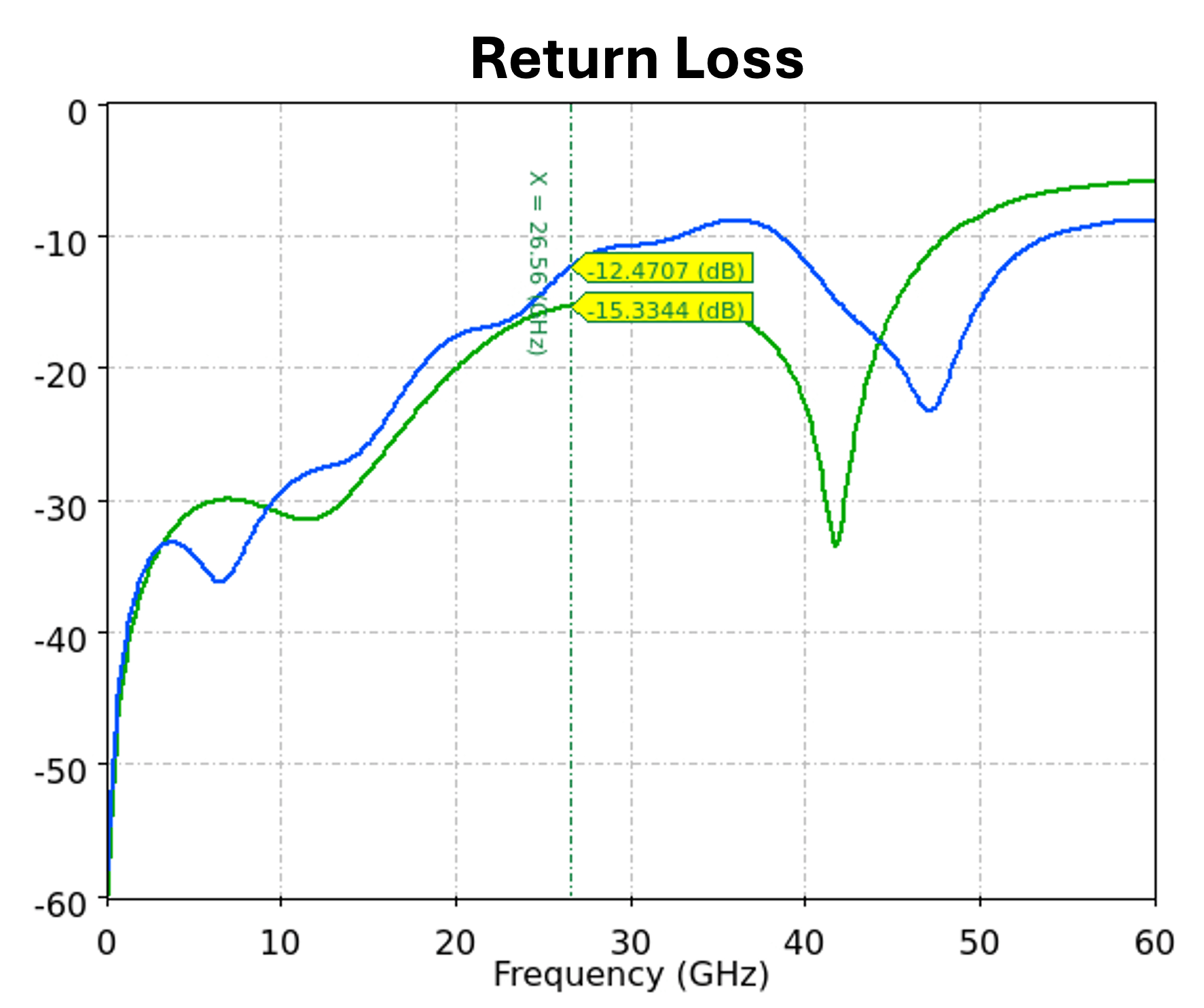

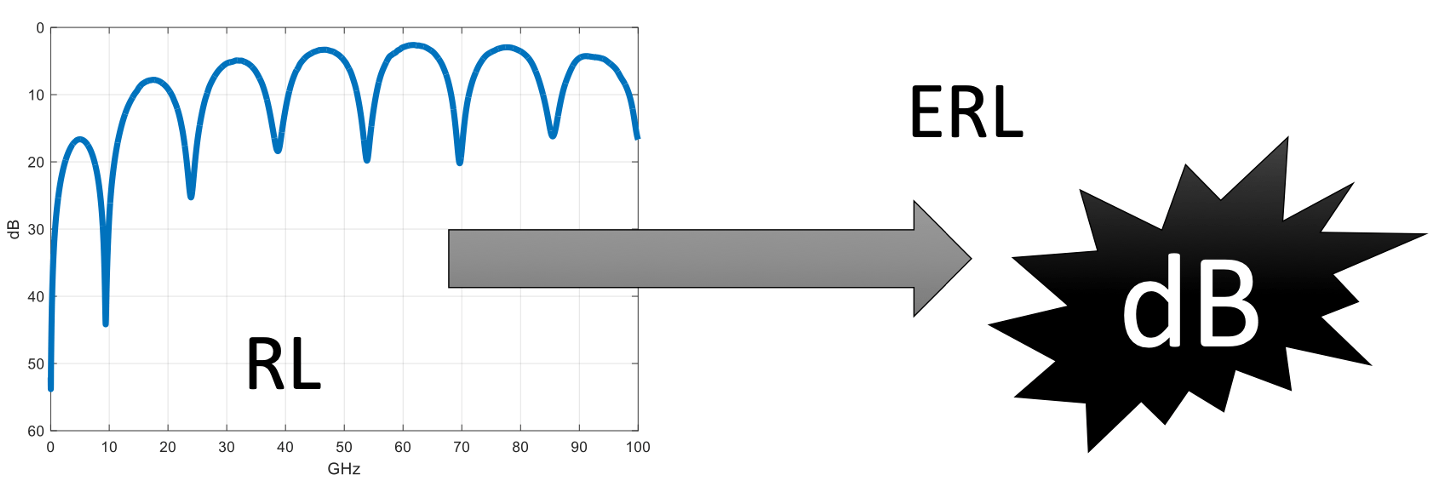

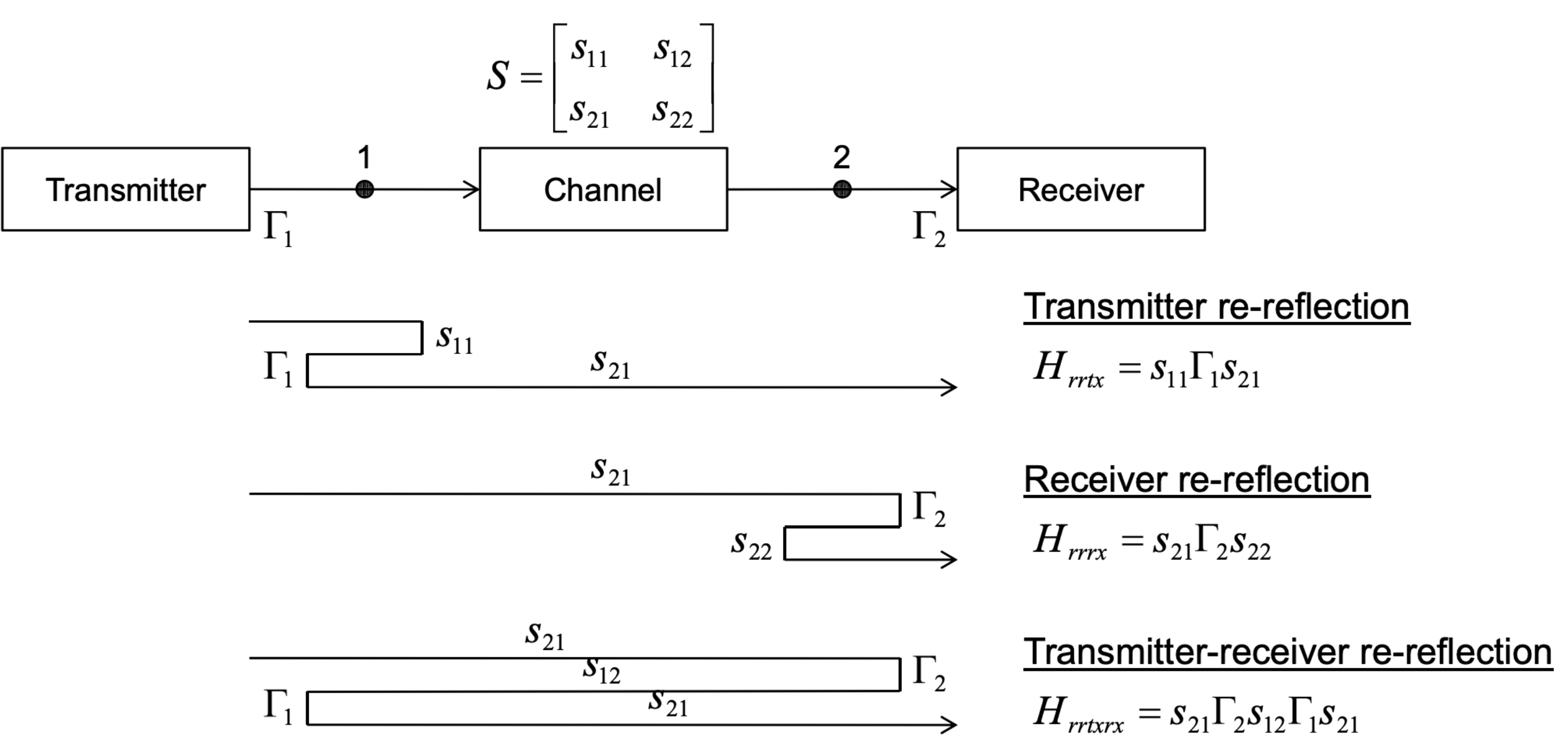

我们在比对两个通道的Return loss时,常常会发生一个问题,像下图,蓝色线的低频RL比较好,但是10-45GHz变的比较差,再往高频又变得相反,由于高速讯号SI看的带宽是从0到相当高频(视data rate而定),所以我们很难判定哪个通道有较好的反射。

而ERL(Effective Return Loss)解决了这个问题!

透过将具有带宽的return loss转换成一个数值,我们就可以很轻易地判断哪个通道的反射比较好。

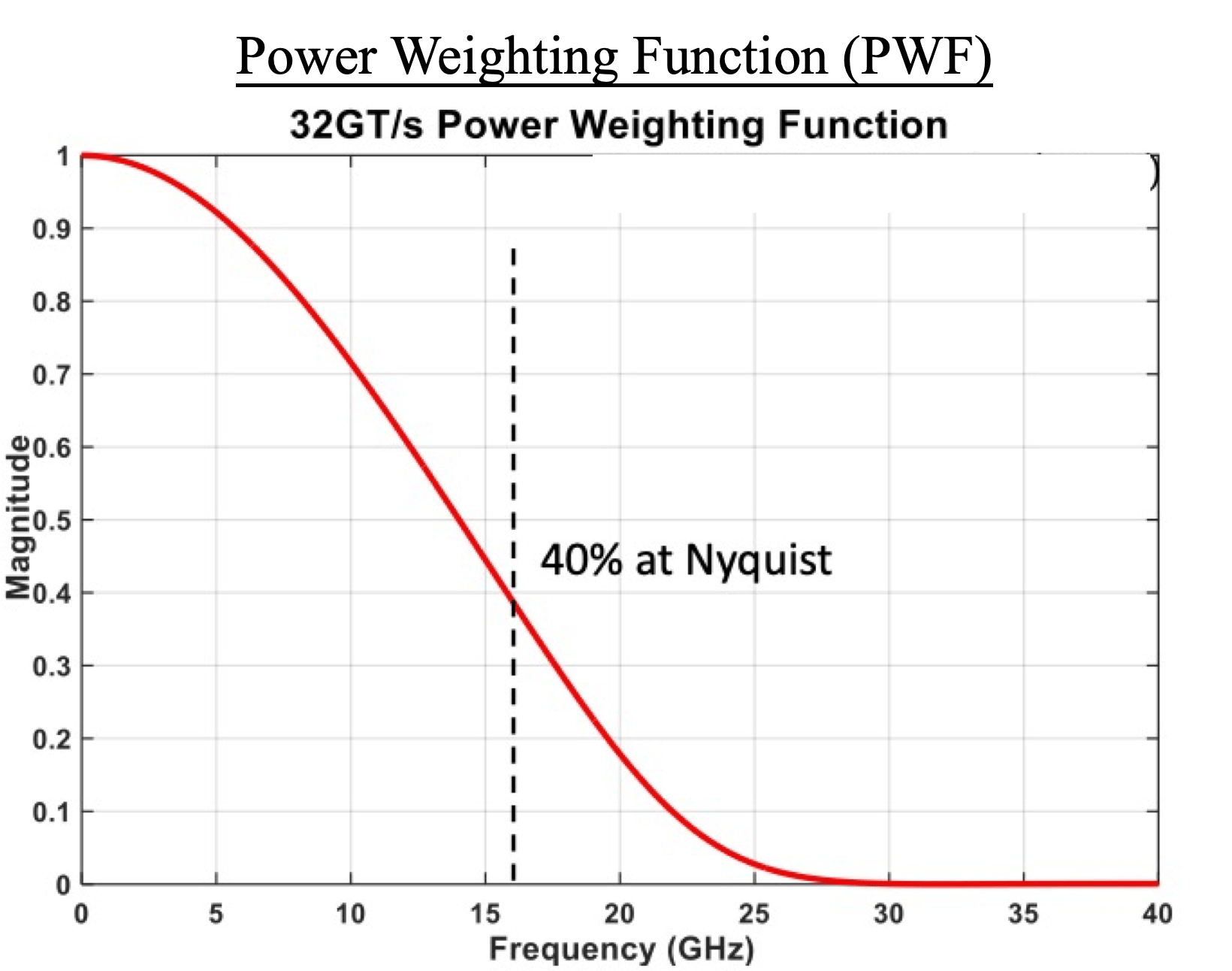

具体实现是通过将整个无源通道(Passive Channel)的Transfer function算出来之后,乘上讯号在不同频率上的功率密度,再利用傅立叶转换成时域Impulse response,再转换成dB数值。 也就是说,我们不用再去担心到底return loss的低频与高带,哪个好才是好,ERL已经将讯号的带宽考量进去,并针对带宽做权重比例分配,完整呈现通道的反射状况。

简单的阻抗匹配 Design Guideline

要做好阻抗匹配可以参考以下建议

- 控制传输线阻抗与高速信号的阻抗要求一致。

- 讯号线的参考平面需要保持完整。 (我们在这里有相关分析)

- 注意蛇形走线造成的阻抗不匹配。

- 运用3D电磁仿真软件求得Via的阻抗,并执行制程稳定度分析。

- 妥善处理不连续结构(例如Pad、Solderball)。

1465

1465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?