乘法器的基本原理可以通过多种方法实现,例如移位相加法、查找表法等。在Verilog中,我们可以使用内建的乘法运算符“*”来实现乘法功能。

首先明确计算的范围。8位2进制1111_1111=255,所以两个8位二进制数的取值范围是0-255。考虑最大值255*255=65025=(1111_1110_0000_0001)2。所以输出结果最大值是16位二进制。

因此在定义输入端口时,应定义8位input[7:0] a,b;

在定义输出端口时,应定义16位output[15:0] out。

设计文件:

module test6(clk,a,b,out);

input clk;

input [7:0] a,b;

output [15:0] out;

assign out = a * b;

endmodule

测试文件:

module tb_test6;

// 定义输入信号和期望的输出信号

reg [7:0] a_tb, b_tb;

wire [15:0] product_tb;

// 实例化被测试的8位乘法器模块

test6 my_est6 (

.a(a_tb),

.b(b_tb),

.out(product_tb)

);

// 初始化和仿真时间控制

initial begin

// 设置测试向量

a_tb = 8'b1111_1111; // 输入A设为255

b_tb = 8'b0000_0001; // 输入B设为1

#10; // 等待10个时间单位,让信号稳定

if (product_tb !== 16'b1111_1111_0000_0001) begin

$display("Test Failed: Expected 16'b1111_1111_0000_0001, Got %b", product_tb);

$finish;

end else begin

$display("Test Passed for inputs 255 and 1.");

end

#10 $finish;

end

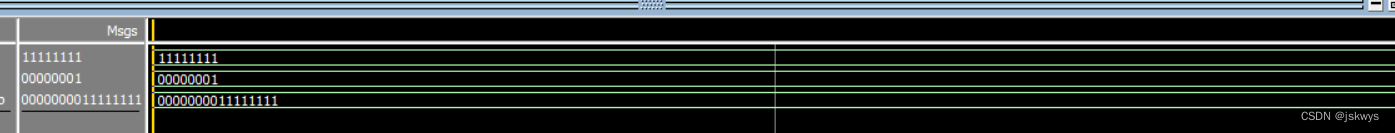

endmodule测试波形:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?