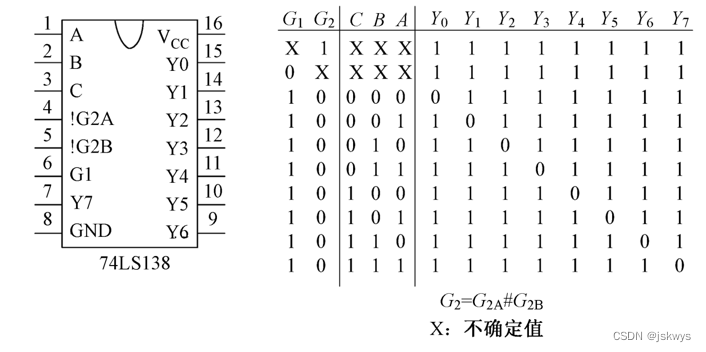

译码器是一种组合逻辑电路,它接收一组二进制输入信号,并根据这些输入信号激活一个或多个输出信号。在本实验中,译码器增加了两个使能端G1和G2来控制译码器的工作状态。只有当G1为高电平且G2为低电平时,译码器才会根据输入的地址信号进行译码操作。其他情况下,译码器将保持禁用状态,即所有输出线保持高电平。

在Verilog中,我们可以使用条件语句(如case语句)来实现这种译码功能。

图1 3线8线译码器符号及功能表

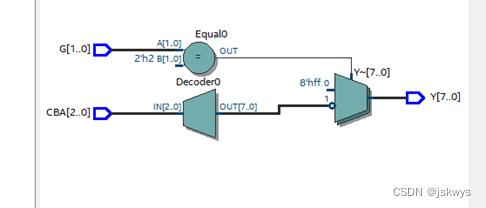

代码:

module test4_exp5_17(CBA,Y,G);

input [2:0] CBA;

input [1:0] G;

output [7:0] Y;

reg [7:0] Y;

always @ (CBA or G)

begin

if( G==2'b10)

case (CBA)

3'b000 : Y = 8'b11111110;

3'b001 : Y = 8'b11111101;

3'b010 : Y = 8'b11111011;

3'b011 : Y = 8'b11110111;

3'b100 : Y = 8'b11101111;

3'b101 : Y = 8'b11011111;

3'b110 : Y = 8'b10111111;

3'b111 : Y = 8'b01111111;

default : Y = 8'bxxxxxxxx;

endcase

else Y = 8'b11111111;

end

endmodule测试文件:

`timescale 1ns/1ns

module tb_test4_exp5_17;

reg [2:0] CBA;

reg [1:0] G;

wire [7:0] Y;

test4_exp5_17 mytest4_exp5_17 (.CBA(CBA),.Y(Y),.G(G));

initial

begin

G=2'b01;

#5 G=2'b10;

CBA=3'b000;

repeat(8) #5 CBA=CBA+1;

end

endmodule网表文件:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?